modelsim仿真rom时,输出高阻态原因

软件版本:modelsim se-64 2019.2

在网上搜到相关博客《modelsim仿真fifo和rom时候,输出出现高阻》

其中有的操作是无关紧要的:

如:

1. 在 ; List of dynamically loaded objects for Verilog PLI applications 下一行处加

Veriuser = D:/Modeltech/convert_hex2ver.dll

当然,以上路径为你的convert_hex2ver.dll文件所在处

2. 注意,将这个两个文件添加之后需要先编译这两个文件,执行一次完全编译,否则不起作用!

有效操作:

3. 找到altera_mf.v和220model.v这2个文件然后把他们一起编译一下就可以了,

这两个文件在quartus 安装目录eda/sim_lib下。

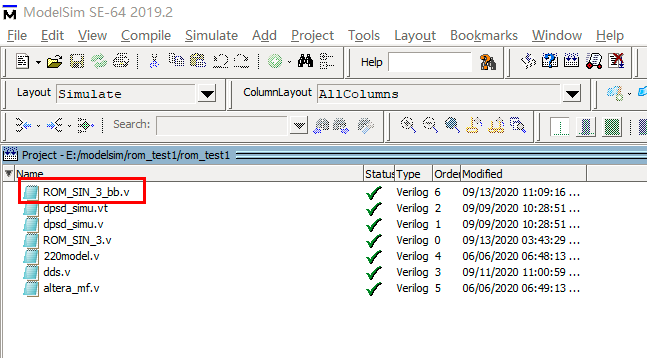

4. 另外加上我自己发现的projects中不能添加多余文件,如图下添加之后输出即为高阻态,

浙公网安备 33010602011771号

浙公网安备 33010602011771号