数字芯片低功耗设计分析-Mos管基础

首先我们要分析Cmos电路的功耗来源。

高器件延迟的Cmos电路之所以能取代低延迟的TLL,最大的优点之一就是功耗低,主要原因静止状态下截止电流极低。原因在于Cmos(Complemetary Symmetry Metal-Oxide-Semiconductor Circuit) 内部互补对称的两个Mos管总是处于一个截止一个导通的状态,而且截止内阻极高。

不过实际电路中,还是存在静态功耗和动态功耗两部分的。

动态功耗又可以分为两部分,第一是负载电容充放电的功耗,第二是mos管瞬间导通的功耗。

负载电容充放电所产生的功耗与负载电容的电容量,信号翻转频率,以及电源电压平方成正比

瞬间导通功耗和电源电压,输入信号翻转频率以及电路内部参数有关。

降低动态功耗的方法也很简单,也就是降低信号翻转频率。而数字电路中无非就是组合逻辑和时序逻辑(寄存器)。

对于时序逻辑(寄存器),就是我们常用的Clock Gating,门控时钟。具体做法就是在寄存器不用的时候,将它的时钟关闭,这样它就会停止翻转。

而对于组合逻辑,也就是门电路,我们也把它上游的寄存器关闭。除此之外,还可以将模块经常翻转的的输入端口置成常量,因为这个算是最上游了吧,这样就彻底消除了所有的翻转。

静态功耗和温度,电压,以及生产工艺有关。特别是栅极宽度进入nm级之后,漏电流成为静态电流的主要成分,生产工艺的影响越来越大。

降低温度,电源电压,以及优化工艺可以降低静态功耗。

顺便说一句,更低的电压还能带来更高的速度,我的理解就是因为上升和下降的时间都可以变短了,举例子就是DDR从2到3再到4,电压从1.8->1.5->1.2。

那么对于低功耗优化设计可以做如下总结:

- 修改逻辑,减少资源使用量。

- 使用更好的工艺。

- 降低电压,使用电压分区设计

- 降低频率,使用频率分区设计

- 关闭时钟。

另外在这里总结一下关于二极管电路的一些知识。

N沟道Mos管 negative 截止 P沟道Mos管 positive 截止

直流噪声容限,二极管电路的直流噪声容限远小于交流噪声容限,Cmos门电路的输出最高低电平要低于输入最高低电平,差值为直流输入低电平噪声容限。输出最低高电平要高于输入最低高电平,差值为直流输入高电平噪声容限。

交流噪声容限,即能改变门电路输出的短脉冲,因为负载电容和寄生电容的存在,短脉冲会被滤除。但是能否滤除的根本决定因素在于电荷量,假如电荷量足够大,能完全充满这些电容达到导通/截止电压的话,还是会造成输出改变。(充电是为了升高电压使得二极管导通截止状态改变)因此可以说交流噪声的脉冲越短,容限越大(需要更高的脉冲电压,因为电荷量等于电流和时间的积分,而电流等于电压除以电阻)。

扇出表示一个电路的输出端能驱动同类型负载电路输入端的数目。这个值取决于工作频率和负载电容。因为限制扇出的主要因素就是负载电容充电速度和建立保持时间的关系。而建立保持时间又与工作频率直接相关。工作频率越高,扇出越小,负载电容越大,扇出越小。

线与逻辑,就是与,不过实现有点复杂,就是有个前提条件。条件是线与的输入也要是OD门/OC门的输出端,这几个输出端的连线直接相连就能实现与的逻辑。而OC(Open Collector) 集电极开路 对应TLL(三极管),OD(Open Drain) 漏极开路 对应Mos,原理相似。开路我们则想到上拉和下拉电阻。

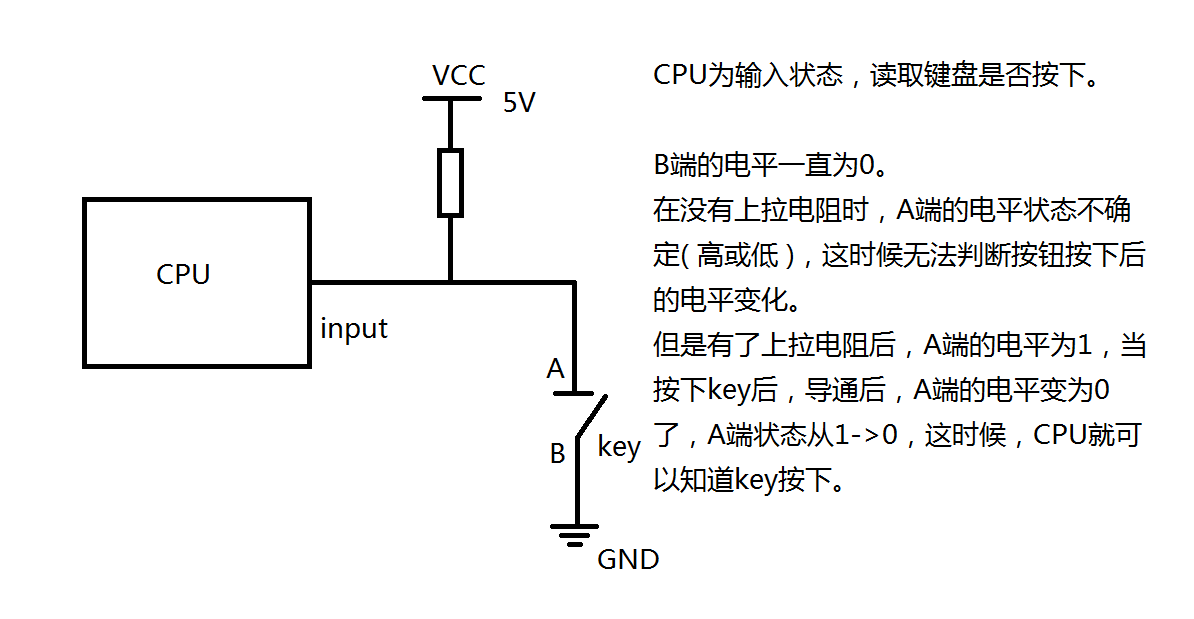

上拉/下拉电阻:原因在于,管脚悬空(空气电阻很高,高阻态)时容易出现感应电动势,这时难以确定电平状态,因此需要对应的操作将其拉高或者置低到一个确定的值。

对于输入来说,假如原来输入是低电平,那么断开时需要接Vcc拉至高,io的阻抗很高,加电阻只有很小的分压。如果没有电阻,那么不断开的时候就会出现问题,Vcc直接连到了低电平(也有可能是接地,那么就会短路),这个时候假如不短路我们也无法确定输入电压。

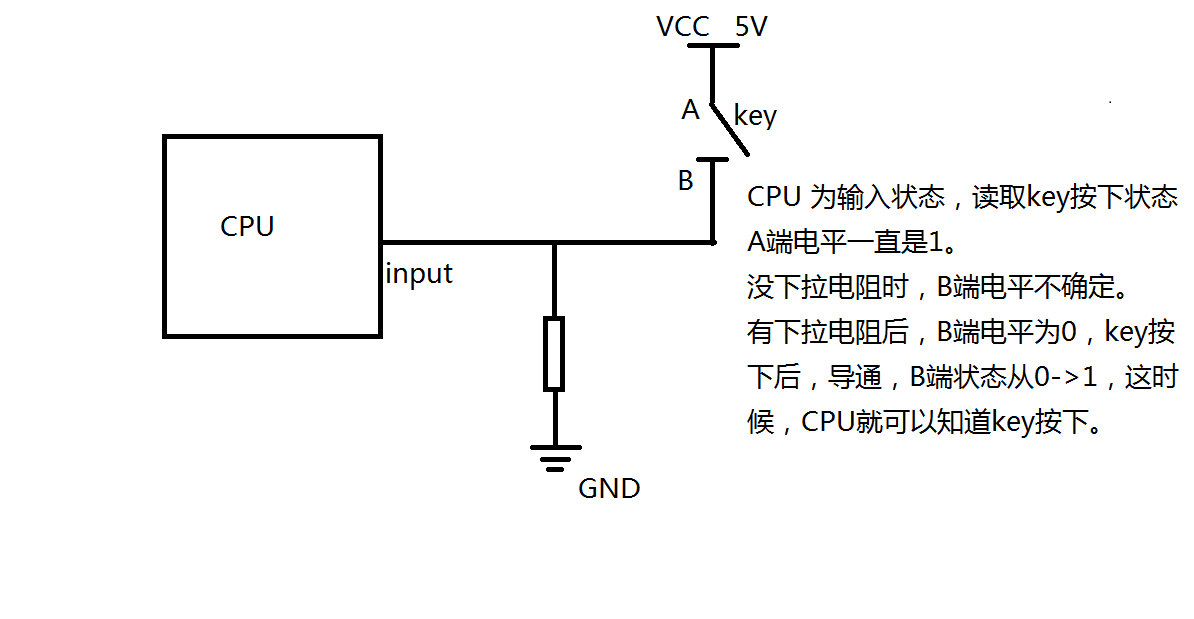

输入原本为高则需要接地拉至低。同样,如果没有这个电阻,不断开的时候原本的高电平输入就直接接地了,不仅会短路还让我们无法确定电压。

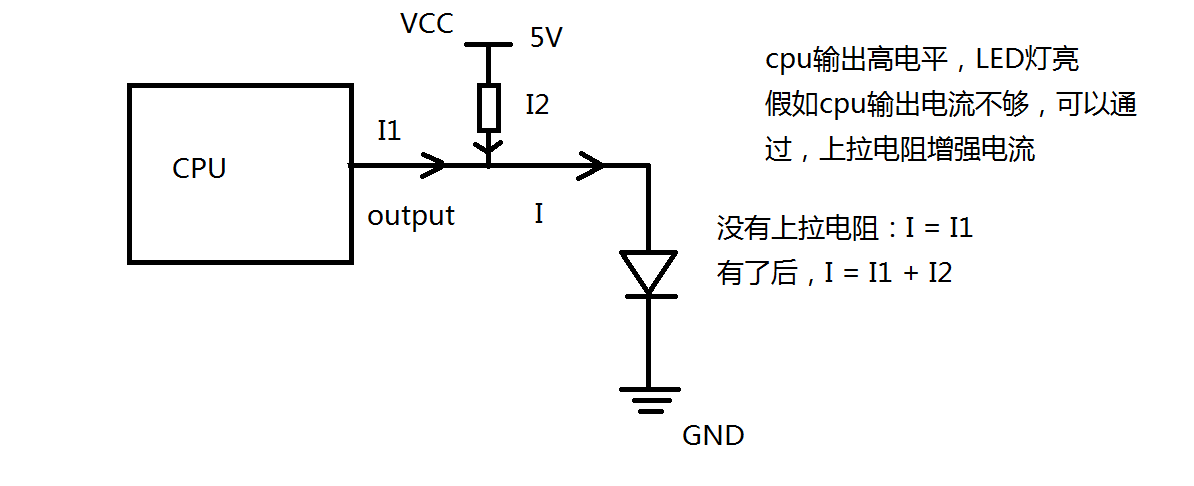

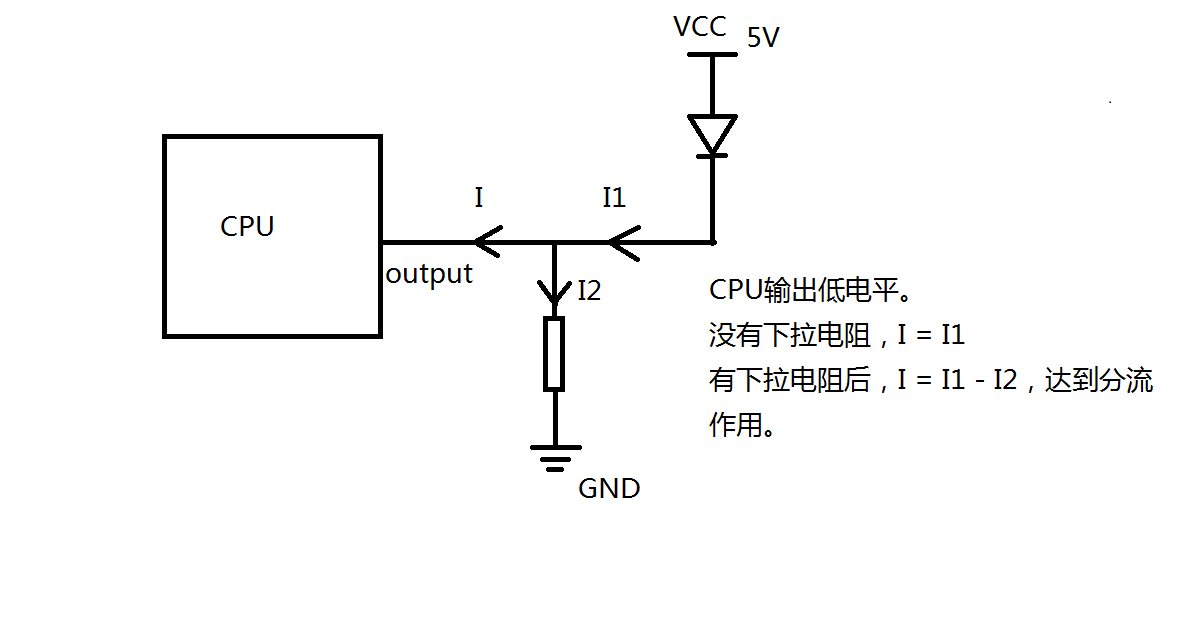

对于输出,输出高电平时,接上拉电阻可以补充电流,增强扇出能力。但是也不能太小,太小有可能超出下游电流容限。输出低电平时,接下拉电阻可以分流,太小分流太多。

浙公网安备 33010602011771号

浙公网安备 33010602011771号