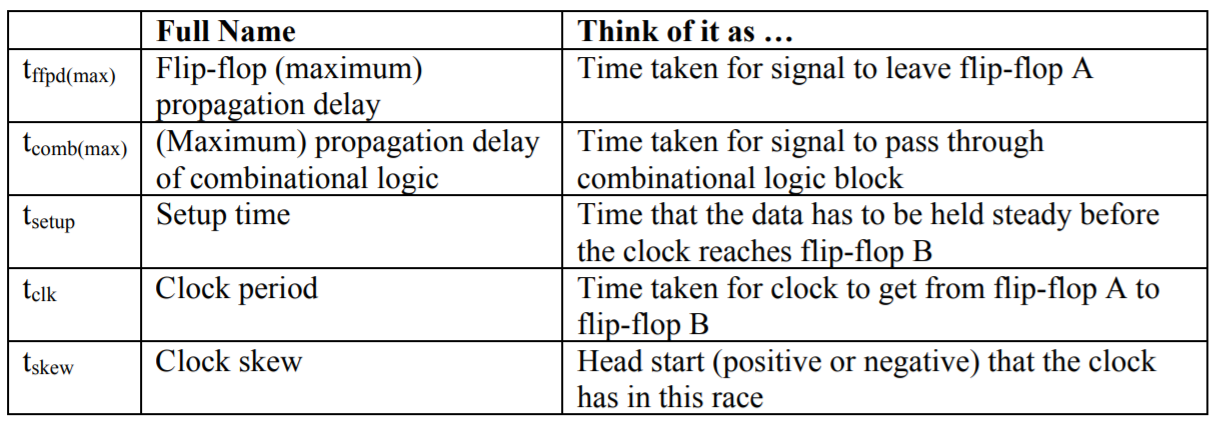

数字电路设计之STA

静态时序分析Static Timing Analysis

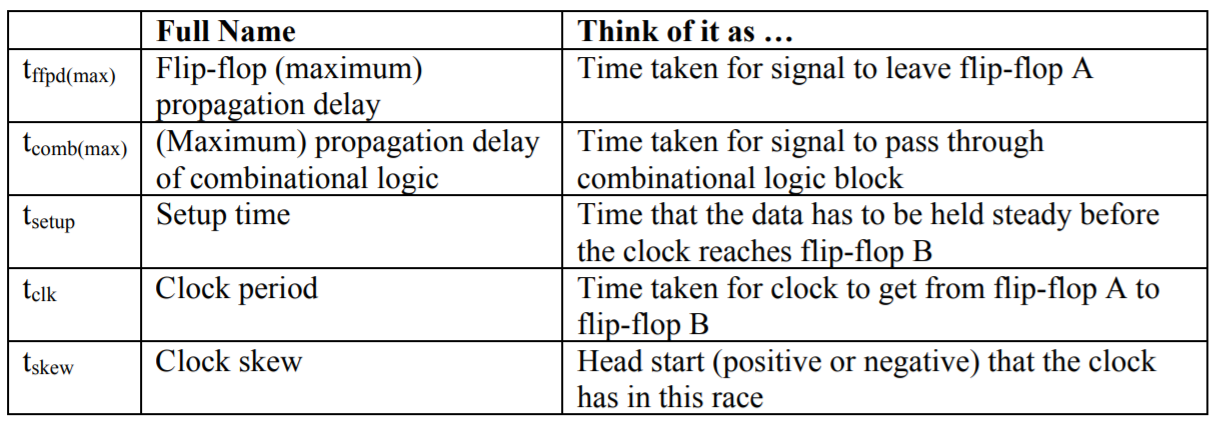

不管是建立时间还是保持时间,都是FF B(接收端)的器件特性所决定的,我们要做的是保证设计能满足元件的特性要求,也就是Setup Time Constraint和Hold Time Constraint.

1. Setup Time Constraint

Setup time = minimum amount of time the data signal should be held steady before the clock edge so that the data can be reliably sampled.

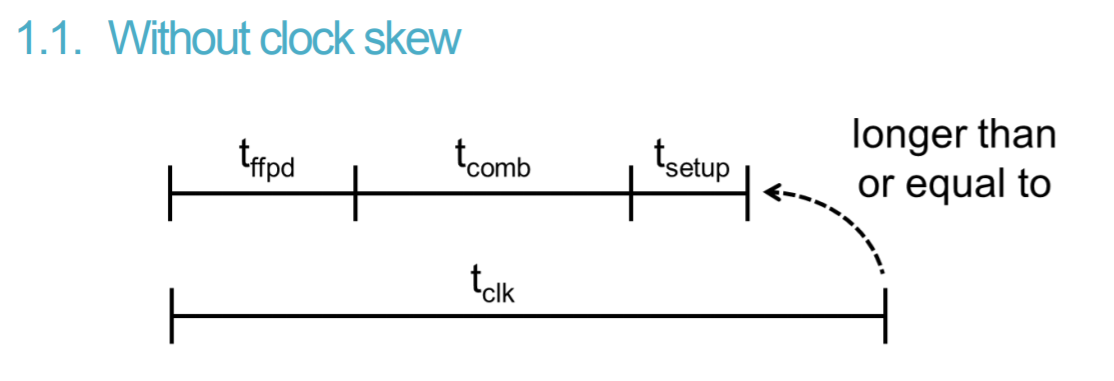

Satisfying the setup time constraint = preparing the data (using combinational logic) in time so that the prepared data is steady for the specified setup time before the clock gets to the receiving flip-flop.

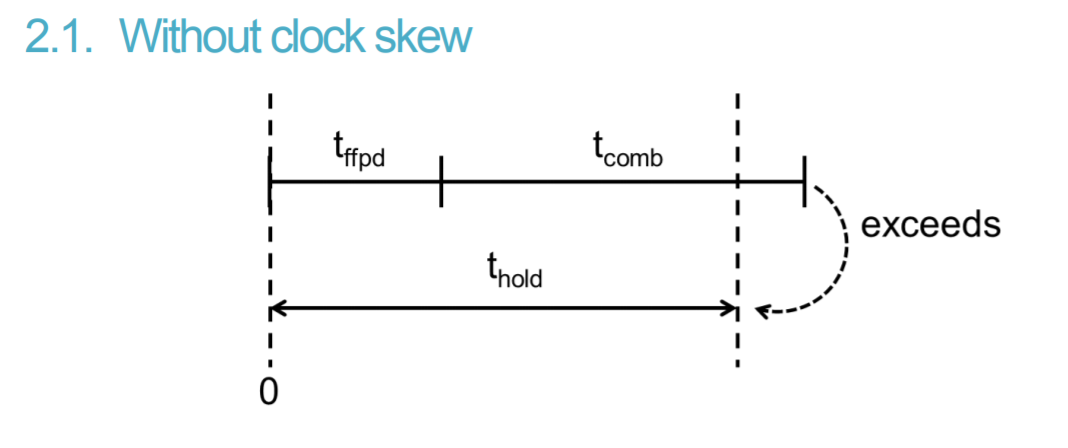

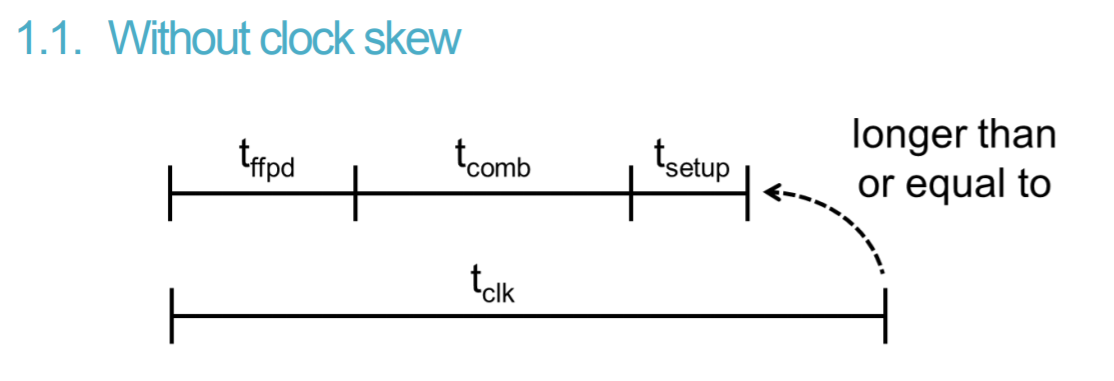

为了保证数据传输的成功,信号的最晚建立时间和下一个时钟有效沿到达时间的差值.在考虑建立时间约束的时候,我们应该考虑最差的情况,也就是数据最慢而时钟最快,假如此时能满足建立时间约束条件,那么我们的设计就是合理的.如下图:

tffpd(max) + tcomb(max) + tsetup ≤ tclk

值得注意的是,加入clock skew不一定就会让上面的不等式紧张,有可能skew是正的,就是说让tclk更长.

Clock skew could arise because of various reasons, usually to do with imperfections of the real world.

Some examples:

§ Clock distribution wire length

§ Temperature variations

§ Material imperfections

§ Direction of clock distribution (whether in the direction of data flow or opposite in direction)

最后一点很有意思,时钟的走线和数据的走线相同或者相反,相同带来更宽松的时序,而相反会导致紧张.

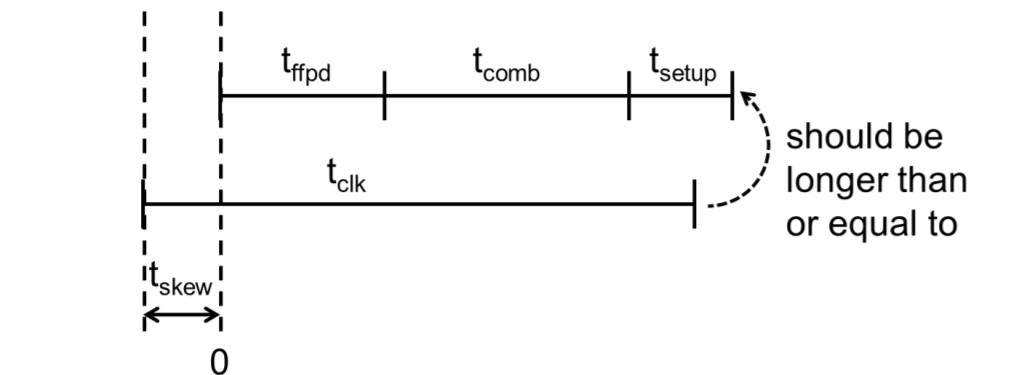

以下是具体的说明: 以下所有的skew都是绝对值,没有正负,skew项前面的+/-代表了它对时序的影响,下面的tclk是接收ff的时钟

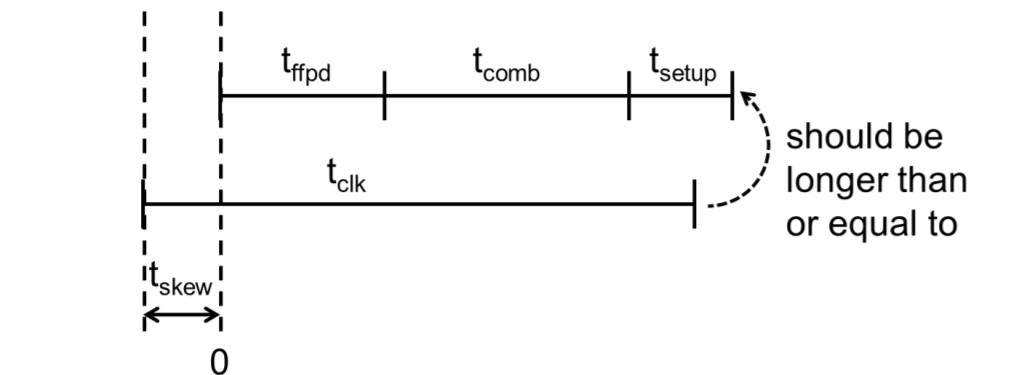

Sending flip-flop receives clock after receiving flip-flop

If the clock reaches flip-flop A after flip-flop B, then the clock is given a head start, and the data now has to move really quickly if the setup time constraint is still to be satisfied.

tffpd(max) + tcomb(max) + tsetup ≤ tclk-tskew

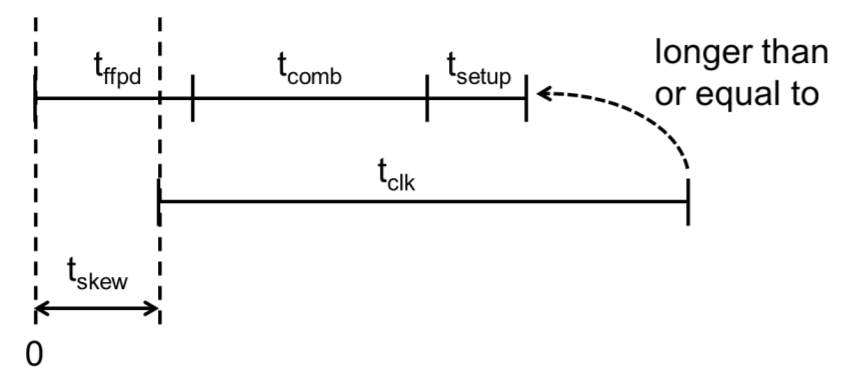

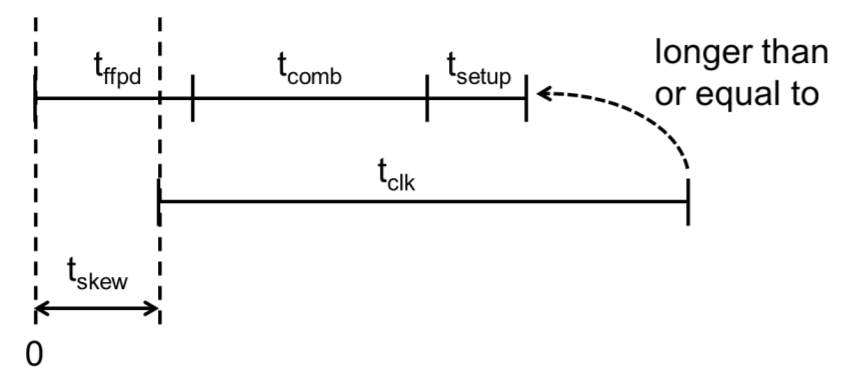

Receiving flip-flop receives clock after sending flip-flop

When the clock is skewed such that the clock signal reaches flip-flop B after flip-flop A, it means that for every clock cycle, the clock is handicapped. The clock signal starts later by tskew.

tffpd(max) + tcomb(max) + tsetup ≤ tclk+tskew

2. Hold Time Constraint

Hold time = minimum amount of time that the data signal has to be held steady after the clock edge so that the data can be reliably sampled.

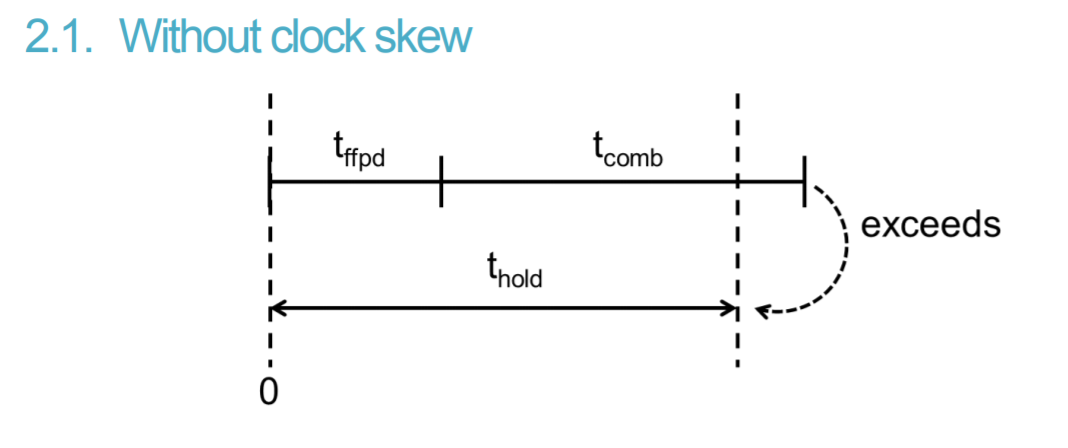

Satisfying the hold time constraint = data must stay valid for the specified hold time after the clock edge

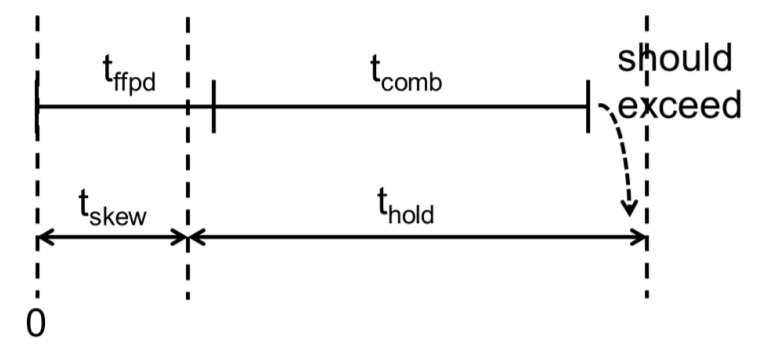

这里要做出一些解释,表格中的contaminated实际上可以理解为下一个数据,设为d1,当前数据为d0,我们需要把d0从FF A 传递给FF B,假如这个d0,B还没有收到,B的输入已经变成了d1,那么可以判定传输失败.所以下图的tffpd(min)右端点表示A的D口数据已经变成d1了,tcomb(min)则表示B的输入Q端口也变成d1了,此时thold已经结束,代表b已经收到了d0,可以接收d1,传输符合要求.和上图略有不同,上图下方时间是FF B的时钟轴,而这个图是FF B需要的保持时间的示意图.

tffpd(min) + tcomb(min) ≥ thold

当我们考虑skew的时候.同样只考虑skew的大小,没有考虑正负.

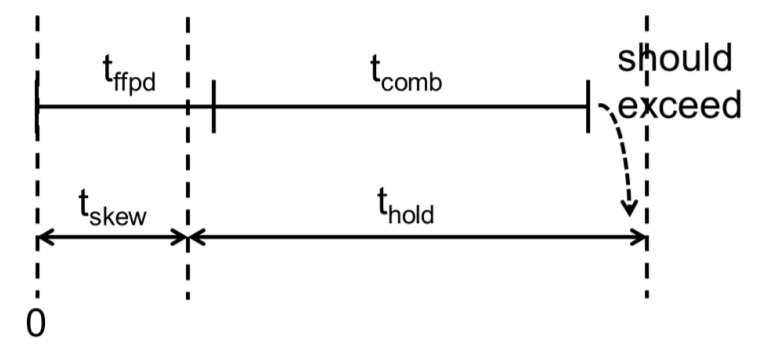

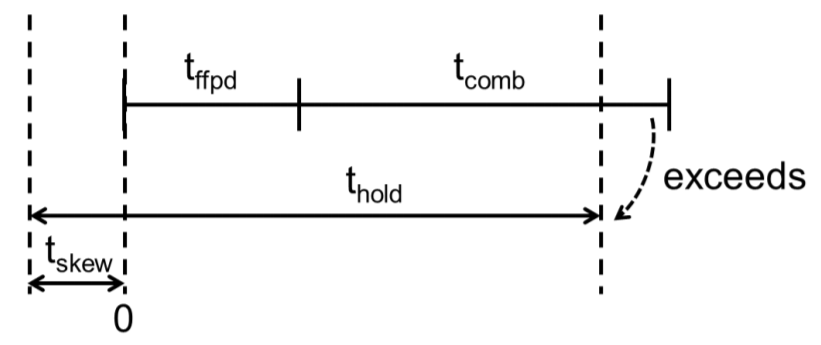

Receiving flip-flop receives clock after sending flip-flop

When the clock reaches flip-flop B after flip-flop A, this means that the time required to pass the baton is lengthened, and the data signal has to be held steady for a longer time.

这个时候可以想想,时钟到达B的时刻更晚,因此保持时间也会相应地右移来保证B能正确取得数据,但是图上的should exceed如何理解呢?很简单,上面这个时间轴右端点表示下一拍数据更新时刻,这个时刻应该晚于hold time的要求,这就是should exceed的意思.

tffpd(min) + tcomb(min) ≥ thold+tskew

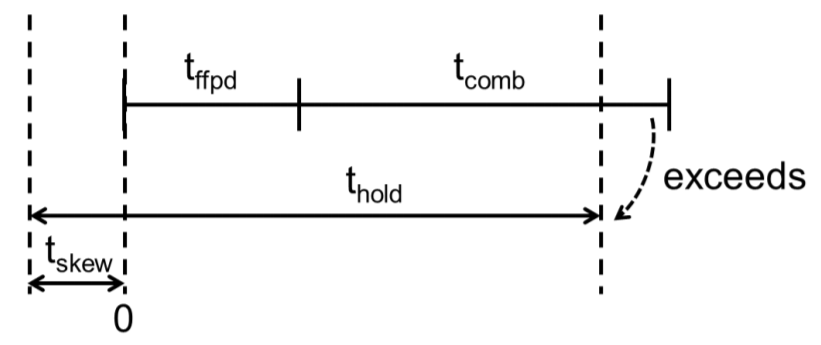

Sending flip-flop receives clock after receiving flip-flop

If the clock reaches flip-flop A after flip-flop B, then the time required to pass the baton is shortened (the requirement is relaxed), since tffpd and tcomb start counting only when the clock reaches flip-flop A.

tffpd(min) + tcomb(min) ≥ thold+tskew

这个相对容易理解,b的始终更快,那么对保持时间的要求相应降低.

相对来说,建立时间理解比较难一点,因为这个图画的没有那么容易理解.

可以看到时钟的skew对建立和保持时间的影响完全相反,而且,更慢的频率或者说更长的周期能让建立时间余量增加,却不能影响保持时间的余量.保持时间仅仅与元器件延迟,走线延迟以及时钟skew有关.

------------恢复内容开始------------

静态时序分析Static Timing Analysis

不管是建立时间还是保持时间,都是FF B(接收端)的器件特性所决定的,我们要做的是保证设计能满足元件的特性要求,也就是Setup Time Constraint和Hold Time Constraint.

1. Setup Time Constraint

Setup time = minimum amount of time the data signal should be held steady before the clock edge so that the data can be reliably sampled.

Satisfying the setup time constraint = preparing the data (using combinational logic) in time so that the prepared data is steady for the specified setup time before the clock gets to the receiving flip-flop.

为了保证数据传输的成功,信号的最晚建立时间和下一个时钟有效沿到达时间的差值.在考虑建立时间约束的时候,我们应该考虑最差的情况,也就是数据最慢而时钟最快,假如此时能满足建立时间约束条件,那么我们的设计就是合理的.如下图:

tffpd(max) + tcomb(max) + tsetup ≤ tclk

值得注意的是,加入clock skew不一定就会让上面的不等式紧张,有可能skew是正的,就是说让tclk更长.

Clock skew could arise because of various reasons, usually to do with imperfections of the real world.

Some examples:

§ Clock distribution wire length

§ Temperature variations

§ Material imperfections

§ Direction of clock distribution (whether in the direction of data flow or opposite in direction)

最后一点很有意思,时钟的走线和数据的走线相同或者相反,相同带来更宽松的时序,而相反会导致紧张.

以下是具体的说明: 以下所有的skew都是绝对值,没有正负,skew项前面的+/-代表了它对时序的影响,下面的tclk是接收ff的时钟

Sending flip-flop receives clock after receiving flip-flop

If the clock reaches flip-flop A after flip-flop B, then the clock is given a head start, and the data now has to move really quickly if the setup time constraint is still to be satisfied.

tffpd(max) + tcomb(max) + tsetup ≤ tclk-tskew

Receiving flip-flop receives clock after sending flip-flop

When the clock is skewed such that the clock signal reaches flip-flop B after flip-flop A, it means that for every clock cycle, the clock is handicapped. The clock signal starts later by tskew.

tffpd(max) + tcomb(max) + tsetup ≤ tclk+tskew

2. Hold Time Constraint

Hold time = minimum amount of time that the data signal has to be held steady after the clock edge so that the data can be reliably sampled.

Satisfying the hold time constraint = data must stay valid for the specified hold time after the clock edge

这里要做出一些解释,表格中的contaminated实际上可以理解为下一个数据,设为d1,当前数据为d0,我们需要把d0从FF A 传递给FF B,假如这个d0,B还没有收到,B的输入已经变成了d1,那么可以判定传输失败.所以下图的tffpd(min)右端点表示A的D口数据已经变成d1了,tcomb(min)则表示B的输入Q端口也变成d1了,此时thold已经结束,代表b已经收到了d0,可以接收d1,传输符合要求.和上图略有不同,上图下方时间是FF B的时钟轴,而这个图是FF B需要的保持时间的示意图.

tffpd(min) + tcomb(min) ≥ thold

当我们考虑skew的时候.同样只考虑skew的大小,没有考虑正负.

Receiving flip-flop receives clock after sending flip-flop

When the clock reaches flip-flop B after flip-flop A, this means that the time required to pass the baton is lengthened, and the data signal has to be held steady for a longer time.

这个时候可以想想,时钟到达B的时刻更晚,因此保持时间也会相应地右移来保证B能正确取得数据,但是图上的should exceed如何理解呢?很简单,上面这个时间轴右端点表示下一拍数据更新时刻,这个时刻应该晚于hold time的要求,这就是should exceed的意思.

tffpd(min) + tcomb(min) ≥ thold+tskew

Sending flip-flop receives clock after receiving flip-flop

If the clock reaches flip-flop A after flip-flop B, then the time required to pass the baton is shortened (the requirement is relaxed), since tffpd and tcomb start counting only when the clock reaches flip-flop A.

tffpd(min) + tcomb(min) ≥ thold+tskew

这个相对容易理解,b的始终更快,那么对保持时间的要求相应降低.

相对来说,建立时间理解比较难一点,因为这个图画的没有那么容易理解.

可以看到时钟的skew对建立和保持时间的影响完全相反,而且,更慢的频率或者说更长的周期能让建立时间余量增加,却不能影响保持时间的余量.保持时间仅仅与元器件延迟,走线延迟以及时钟skew有关.

余量,Slack。

那怎么修呢?

直接看公式

tffpd(max) + tcomb(max) + tsetup ≤ tclk +/- tskew

那么不满足的时候,也就是说,左边比右边大,那么就减少左边的因素,增大右边的因素。

换用更快的FF,缩小ffpd,减少组合逻辑延迟(插流水),或者移后面寄存器的时钟。

浙公网安备 33010602011771号

浙公网安备 33010602011771号