数字电路-亚稳态机制

亚稳态产生的环境很多,最典型的比如跨时钟域信号传递,具体来说比如开关,视频图像输入,网络数据传输.

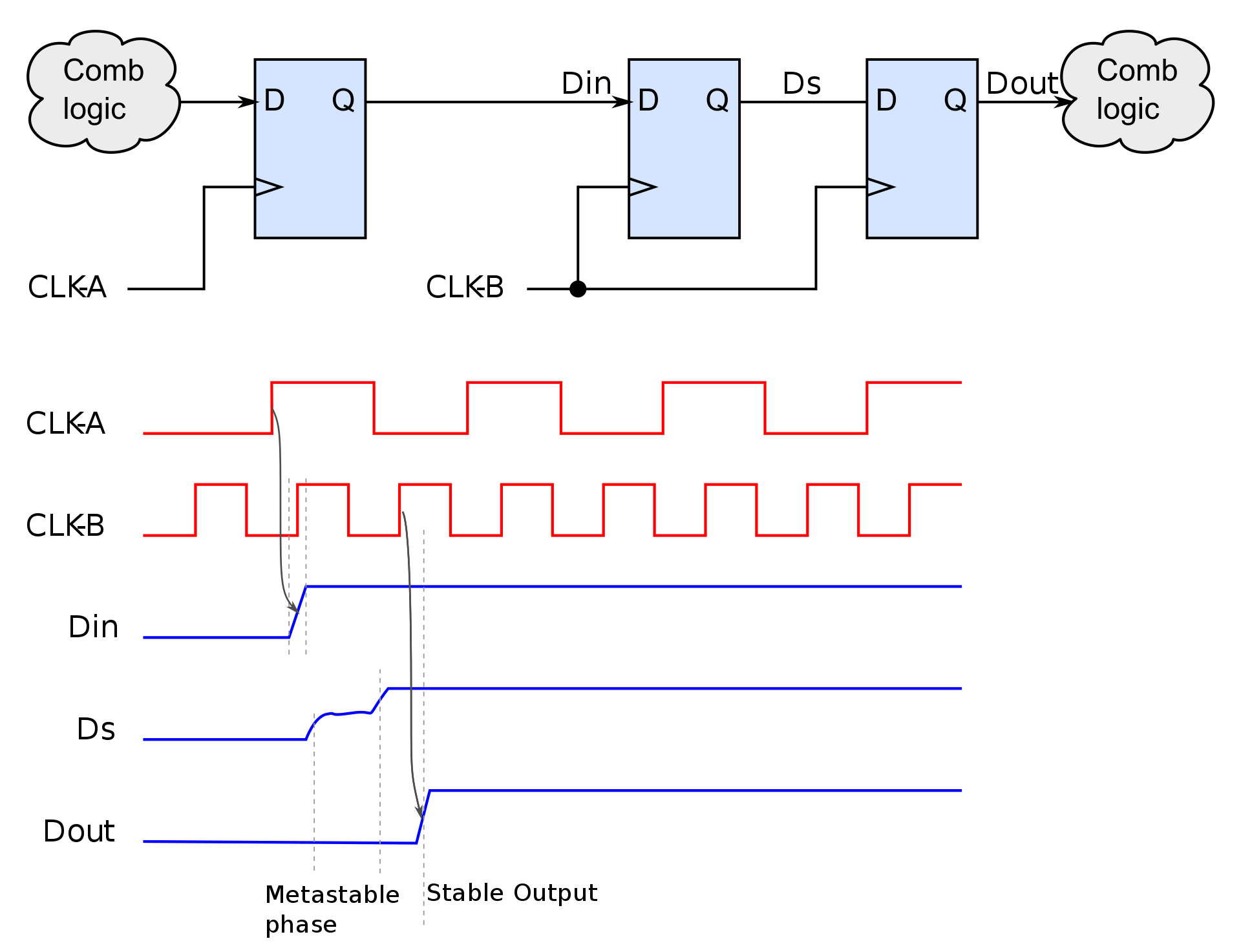

一图胜千言,网上狗屁不通互相抄袭的文章太多,维基百科这张图基本能解释一半了.

图里就是典型的单比特跨时钟域产生的亚稳态处理方式,通过两级寄存器获得正确的信号电平.

因为真实的信号有上升和下降沿,如果在后一个时钟域的有效沿来临时,与之对应的输入数据Din建立时间或者保持时间不满足,那么这个寄存器(称之为寄存器1号)的输出Ds就是难以预测的未定值.

从T0到未定值结束的持续时间我们叫做resolution time.我们把这个时钟上升沿时刻记为T0.

因为1号的未定输出Ds变化在T0之后,所以2号寄存器并不会在T0时刻取到未定值.那么假如在T0之后的下一个上升沿,命名为T1,来临之前,1号的输出Ds能够稳定,那么2号就能得到稳定的输入并且产生稳定的输出Dout.

注意,只是稳定的信号,并非正确的信号,因为亚稳态稳定后的信号是随机的.等到T1的时候,1号的输入再次取样,之后T1才会有正确的输出.

假若在T1上升沿来临之时,1号的输出还在不稳定状态,那么这个不稳定状态将会延续,也就是说Dout也会变成不稳定状态.在这种情况下,亚稳态就会向后传递,传递的后果取决于系统的健壮性.

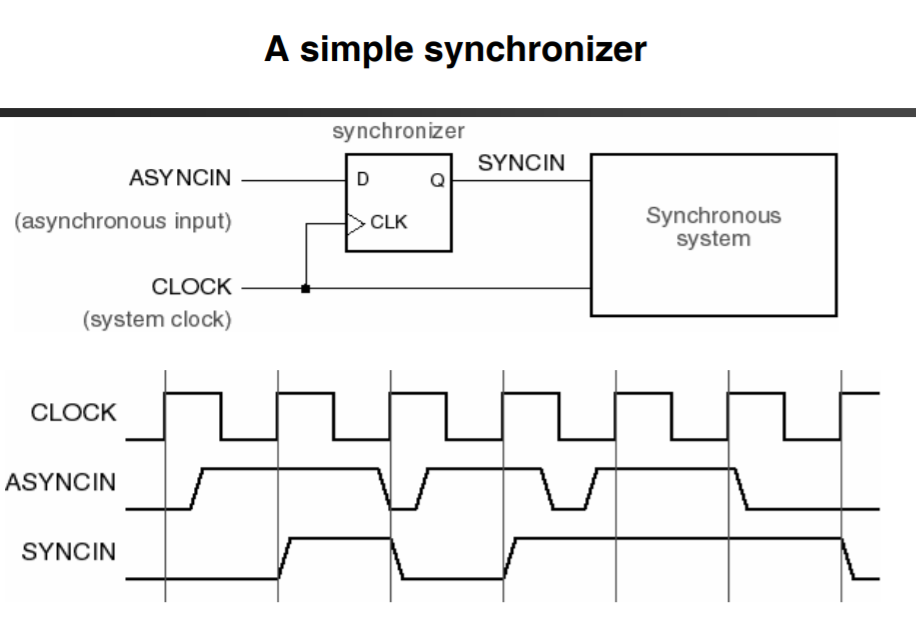

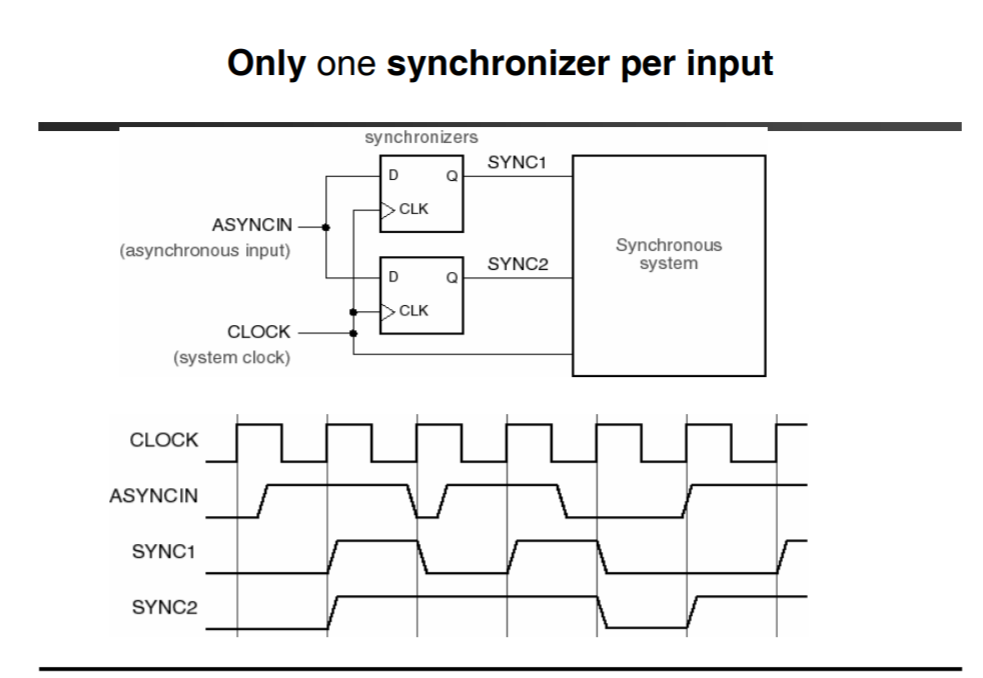

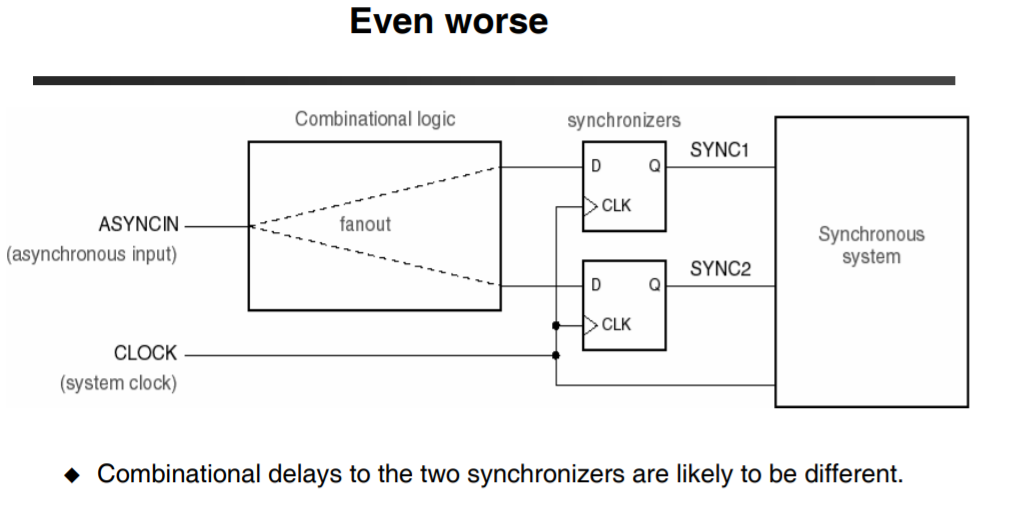

具体来看,我们有以下几幅图(来自帝国理工课件)

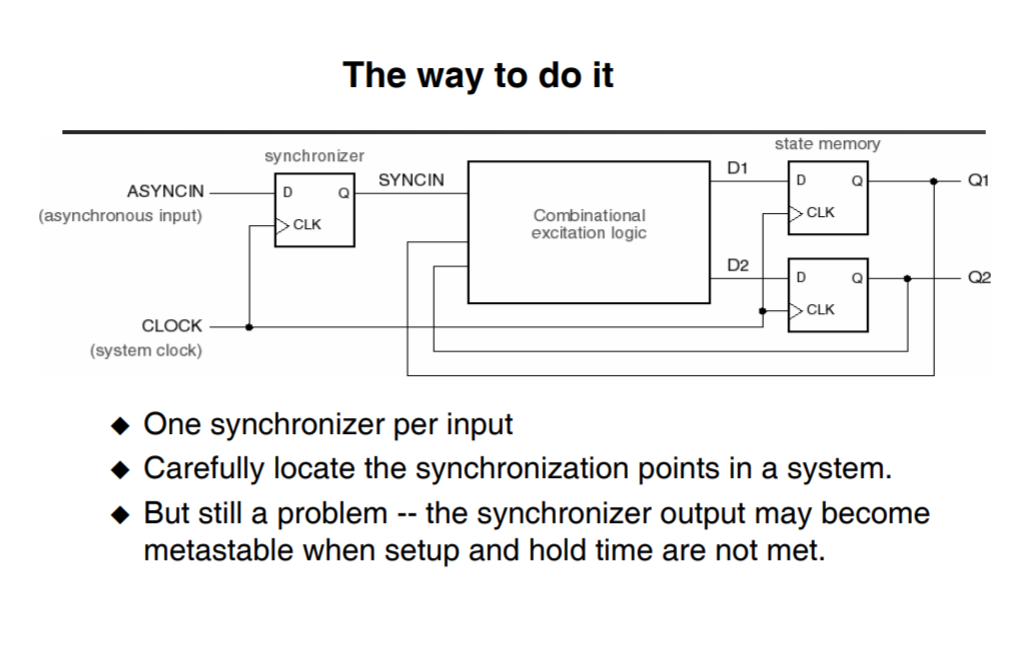

左边是仅仅用了一级同步,这一级的输出SYNCIN很有可能出现亚稳态,而右边是两个并行的一级同步,可以发现,尽管没有出现亚稳态,因为信号ASYNCIN的skew不同或者亚稳态恢复结果随机,,两级同步触发器的输出出现了不一样,而这明显与设计意图不符.左下直接说明了这一点.而右下的图展示了正确的做法,这样消除了skew的影响,但是亚稳态的问题还是没有解决.不稳定的信号直接接组合逻辑会导致组合逻辑的输出也会变成不稳定.其实话说到这里解决方法也很明显了,就是把可能出现亚稳态的输出信号再接到一个触发器上.

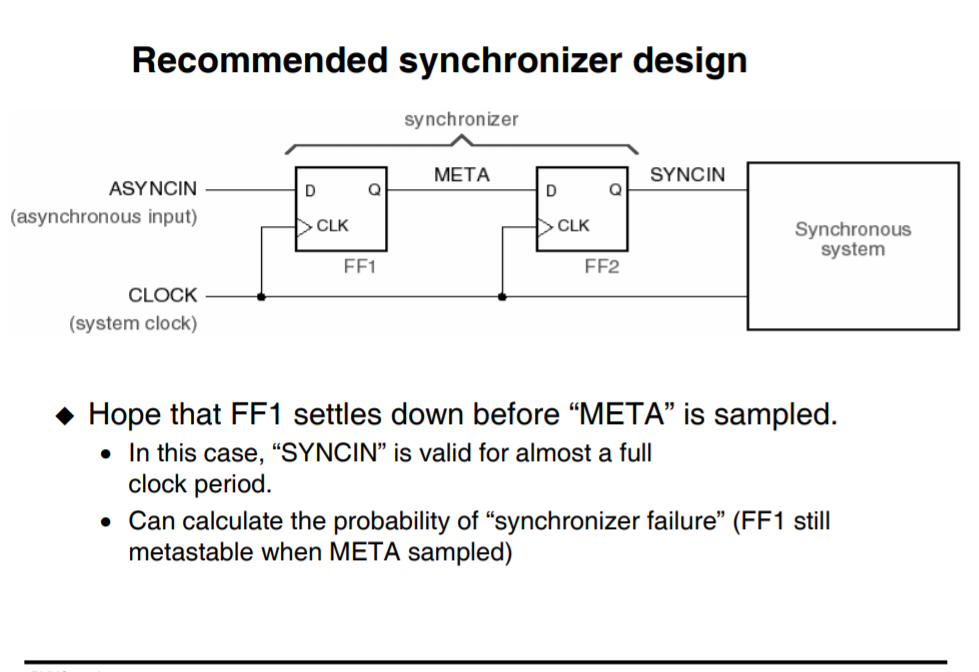

下图是正确的做法,和维基的图基本类似.

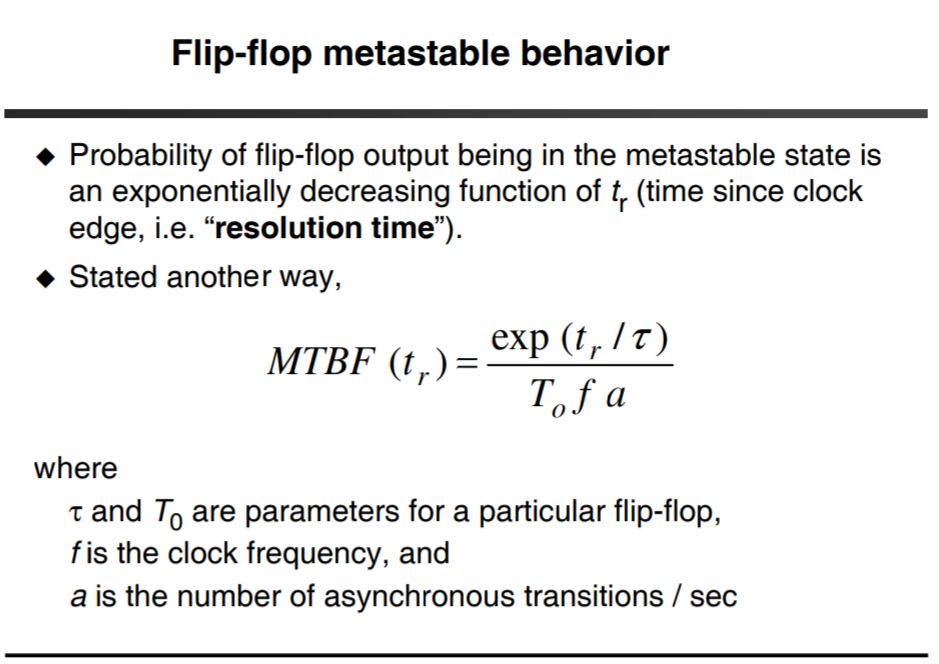

但是这里同样也指出了之前提出的问题,假如resolution时间比一个周期还长,META被采样的时候,FF1的输出还没有稳定,怎么办?出现这种情况的概率很小,但是存在,这个概率是可以计算的.MTBF是mean time between failure的缩写,可以看到, 触发器输出处于亚稳态的概率是tr的指数递减函数.注意,在这个公式里,tr是不引起系统采样错误的最长亚稳态持续时间,a其实就是异步输入的频率,并且可以看到,这个时间和元器件本身也是相关的.

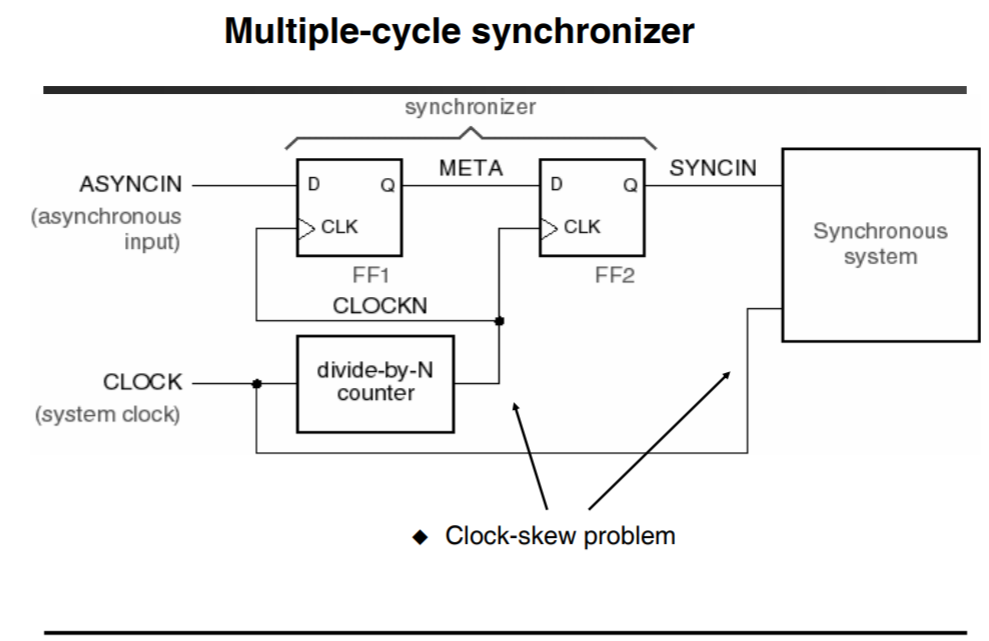

更快的时钟频率会带来更短的MTBF,为了得到更长的MTBF,我们可以等待几个时钟周期来得到更长的resolution time,只要没有握手信号.

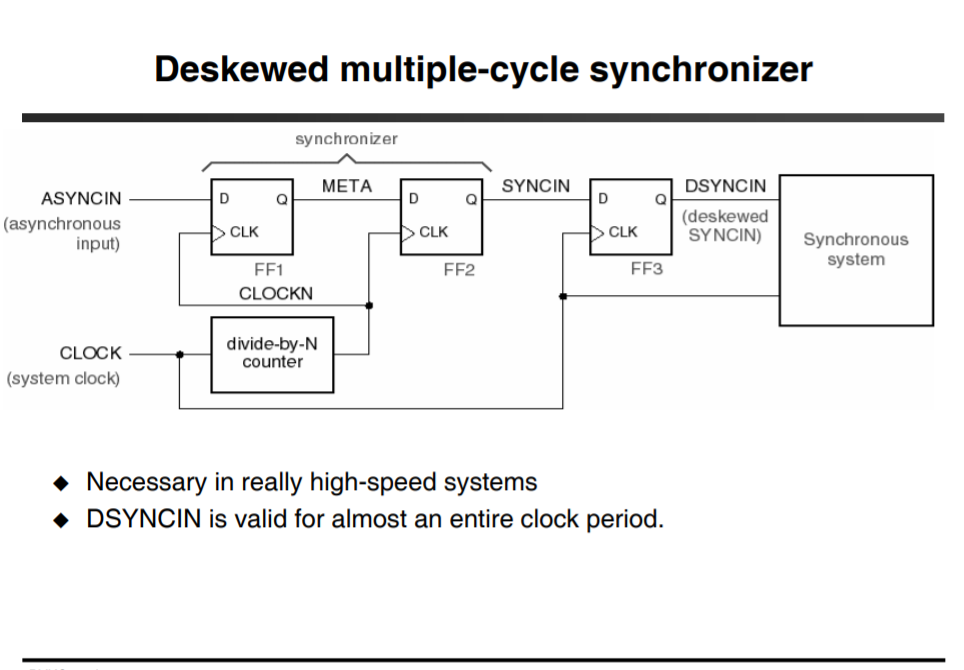

在上文的两级触发设计中还有两个clock skew的问题,第一个如左下所示,这样会使SCYCIN和发往synchronous system的时钟出现skew,解决方法如右图,清晰明了,不在赘述.

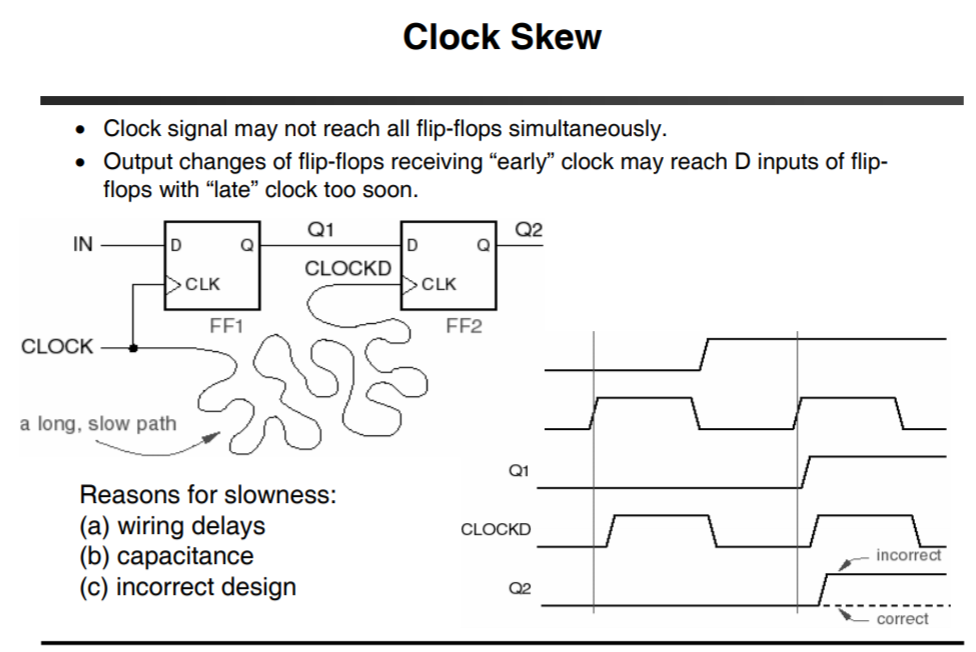

左下图是两级触发设计中,两个触发器之间的skew问题,原因也列了,线路延迟,电容充放(应该算惯性延迟),不正确的设计.右下图是时钟延迟计算,这个在STA中也经常遇到

tffpd(min)是ff传输延迟,后面那个comb是组合逻辑延迟.大于0证明设计还行,接近0表示很紧张,小于0就得插寄存器啦.

同步电路不会出现亚稳态,如果出现了,那其实是设计为接受同步信号的电路收到了异步信号导致动作异常.

最后一句话总结一下,单bit多级寄存器只能防止亚稳态的传递,无法防止逻辑错误的产生,逻辑错误产生需要靠逻辑设计来消除或者规避影响。

浙公网安备 33010602011771号

浙公网安备 33010602011771号