运放,运放

在FPGA高速采集中,除了外部的AD芯片之外,最重要的是运放,因为必须将微小信号放大后才能进入AD,转换出数字信号。

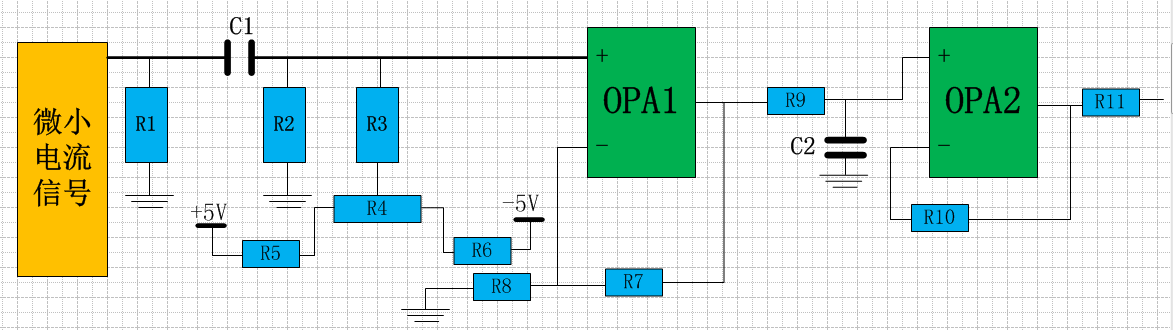

运放设计如上图,外部输入微小电流信号,通过电阻R1取电,转换为电压,请注意R1阻值,以与信号源进行阻抗匹配。

C1和R2组成高通滤波器,滤除不需要的高频信号。

电位器R4和电阻R3、R5、R6组成直流偏置调零电路。

R7和R8组成负反馈电路,进行信号放大。

OPA1输出的放大信号经过R9和C2组成的低通滤波电路进入OPA2。

R10与运放组成跟随电路,并通过R10滤除部分高频杂质。

R11为OPA2输出电阻。

设计中全部使用同相输入。由于运放在增益增大时,直流偏置也会增大,所以使用电位器进行调零(要考虑温度对电位器的影响,选用合适的电位器)。

至此,计算合适的阻值和容值,由OPA1和OPA2组成带通滤波放大器,对微弱信号放大,进入AD芯片进行AD转换,FPGA才能够得到正确的采样数据,发挥FPGA的作用。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间