流行的FPGA的上电复位

在实际设计中,由于外部阻容复位时间短,可能无法使FPGA内部复位到理想的状态,所以今天介绍一下网上流行的复位逻辑。

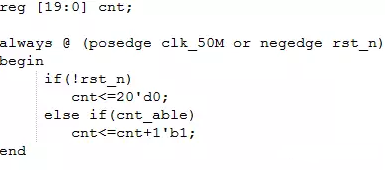

在基于verilog的FPGA设计中,我们常常可以看到以下形式的进程:

信号rst_n用来对进程中所用变量的初始化,这个复位信号是十分重要的,如果没有复位,会导致一些寄存器的初始值变得未知,如果此时FPGA就开始工作的话,极易导致错误。

那么,这个复位信号来自何处?难道我们做好的系统,每次上电后都要手动按一下reset按钮么?

答案是否定的!这个复位信号其实是由特定的程序来产生的,系统每次上电,都会由该程序产生一个复位信号,从而避免了手动复位。

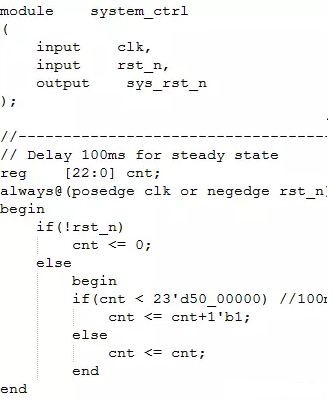

复位的方案很多,下面介绍一个简单方案。

clk:50M时钟输入

rst_n:异步复位输入

sys_rst_n:系统全局同步复位信号

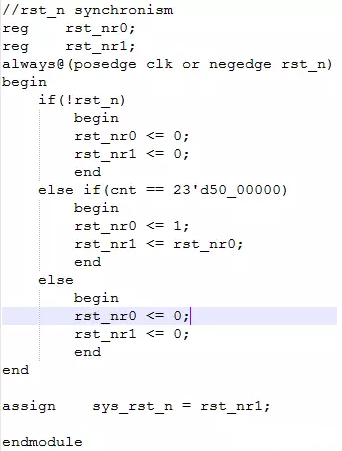

第一个进程用来延时,当上电后,延时100ms,以保证FPGA内部达到稳定状态;此时sys_rst_n始终为0,也就是系统时钟处于复位状态中;2.当100ms延时结束后,sys_rst_n与系统时钟同步释放,即sys_rst_n拉高,复位结束,系统开始正常工作。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间