浅谈乘法器的用法

在做项目的过程中,经常遇到乘法计算,乘法器的设计就尤为重要。乘法器决定了最终电路功能能否实现,资源使用量多少以及时序性能优劣等。

乘法计算中,通常会使用 “*” 或者设计乘法器实现。

设计乘法器时,通常使用加法树乘法器,实现流程图如下:

如上图a[3:0]与b[3:0]乘法器设计,与分布式算法类似,a*b乘法计算设计如下:a*b[0]<<0 + a*b[1]<<1 + a*b[2]<<2 + a*b[3]<<3,通过移位和加法运算实现最终功能。结构框图如上。

设计中,上述逻辑存在大量组合逻辑,延时大,当时序要求不高的情况下,可以使用,当时序要求很高时,此电路会产生时序违规。要想提高电路时序性能,需要在x、y、z三处选一处、两处或者三处加入触发器流水逻辑,提高电路时序性能,但其结果会使输出延迟几个时钟周期,设计时应该考虑这一情况。

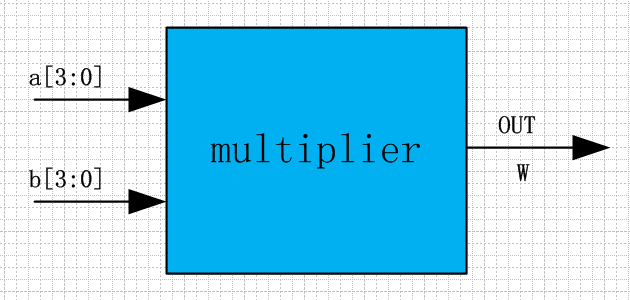

当使用 “*” 做乘法运算时,一般综合工具都会直接调用FPGA片上集成的硬核乘法器,而不再使用逻辑单元搭建乘法器。设计结构图如下:

上图为利用FPGA片上乘法器实现最终乘法。为了提高时序性能,可在w处加入寄存器流水线。

上述设计速度明显优于第一种设计,但会消耗大量的片上硬核乘法器。

上述两种设计各有其优势,在使用中请根据实际设计电路采用合理的方案。

在前述文章中,设计FFT和IFFT,乘法设计采用第二种方案,提高电路速度。如果采用第一种方案,将会增加流水线程度,增大FFT以及IFFT的计算周期。

而在简单和低速的乘法计算中使用第一种方案是一种比较良好的选择。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间