SERDES高速系统(一)

在目前主流厂商的高端FPGA 中都集成了SERDES(串并收发单元)硬核,如Altera的Stratix IV GX器件族内部集成的SERDES单通道支持600Mbit/s到8.5Gbit/s数据熟率,而Stratix IV系列器件族还集成支持150Mbit/s到1.6Mbit/s的高速差分信号接口,并增强了其动态相位调整(DPA,Dynamic Phase Alignment)特性;Xilinx的Virtex II Pro内嵌的SERDES单通道支持622Mbit/s到3.125Mbit/s的数据速率,而Virtex II Pro X内嵌的SERDES单通道支持2.488Gbit/s到10.3125Gbit/s的数据速率;Lattice的高端SC系列FPGA内嵌的SERDES单通道支持622Mbit/s到3.4Gbit/s的数据速率,而其多款可编程系统级芯片FPSC(FPSC,Field Programmable System Chip)内嵌的不同性能的SERDES单通道支持400Mbit/s到10.709Gbit/s的数据速率。

在FPGA中内嵌诸如SERDES的硬核,可以大大地扩张FPGA的数据吞吐量,节约功耗,提高性能,使FPGA在高速系统设计中扮演着日益重要的角色。

在阐述SERDES基础概念的基础上,讨论Stratix IV GX的SERDES与DPA结构,通过对典型高速系统设计举例和对高速PGB设计注意事项的介绍,引领读者进入高速系统设计的世界。

SERDES的基础概念

这里将介绍SERDES的基本概念,并介绍SERDES相关的专有名词:眼图(Eye-diagram)、眼图模板、抖动(Jitter)、容忍度(tolerance)、功耗(Power Consumption)、预加重(Pre-emphasis)、均衡(Equalization)、8B/10B编码等。

SERDES的概念

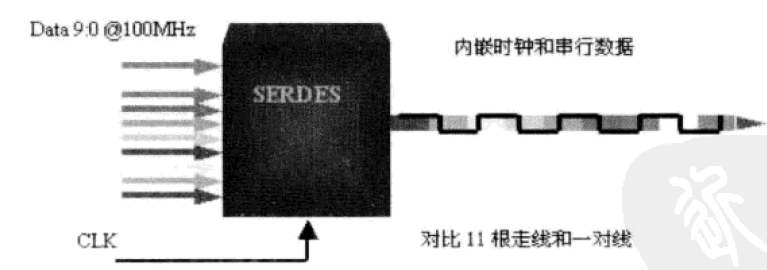

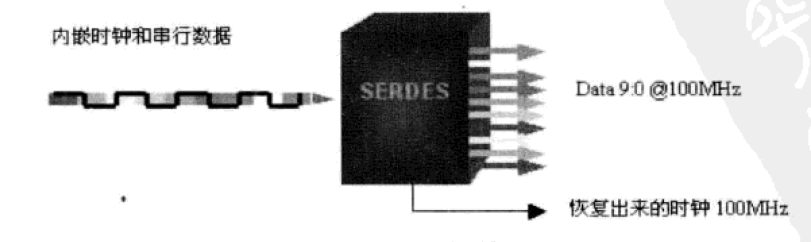

SERDES是SERializer和DESerializer的英文缩写,即串行收发器。顾名思义,它由两部分构成:发端是串行发送单元SERializer,用高速时钟调制编码数据流;接端为串行接收单元DESerializer,其主要作用是从数据流中恢复出时钟信号,并解调还原数据,根据其功能,接收单元还有一个名称叫CDR( Clockand data Recovery,时钟数据恢复器)或CRU( Clock RecoveryUnit,时钟恢复单元)。如图,所示为10根数据线的串行传输和解串行接收示意图,10 根100MHZ的信号线入SERDES器件产生串行码流,时钟也调制到码流内,反过来通过它恢复并行的数据和时钟。SERDES技术的应用很好地解决了高速系统数据传输的瓶颈(特别是背板传输应用),节约了单板面积,提高了系统的稳定性,是高速系统设计的强有力支撑。

10:1SERDES功能示意图

眼图与眼图模板

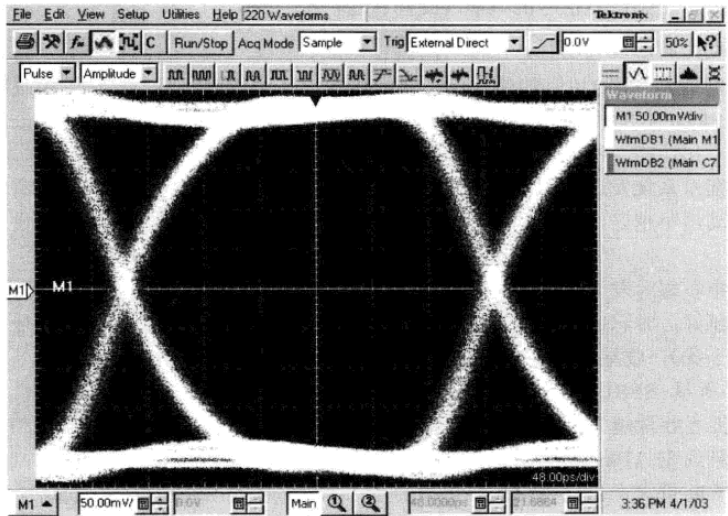

SERDES的最重要的两个参数指标是传输速率和传输长度,即在符合误码率要求的以何种传输速率可以传输多长距离。其形象的评价方法是利用眼图,眼图的高和宽反映了信号的传输质量,如图所示为Altera Stratix IV GX器件眼图实例。

AlteraStratix IV GX器件眼图实例

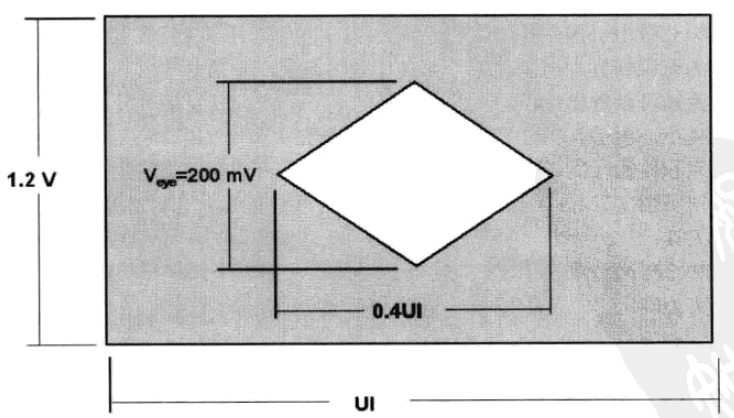

眼图模板是用于对比眼图质量的参考系,常见的眼图模版有两种:菱形模版和六边形模版。如图所示为菱形眼图模版示意。

菱形眼图模版示意

其中,众轴是眼图的高度,单位是Mv,用以表示正确接收的差分信号的幅度,和接收端可正确恢复信号的电平需求直接相关;横轴是眼图的宽度,单位是UI或ps,用以表示无码间干扰的接收时间,和接收端分辨两个相邻码元的能力直接相关。UI,Unit Interval的缩写,即1bit数据周期的对应时间,例如对于1Gbit/s的眼图1UI是1ns。评价眼图的标准是眼的张开的程度要大,并且眼线要清晰。眼线清晰说明整个系统抖动小,准确度高;眼图的张开程度大,说明接收的信号幅度大,时间抖动小,这样对接收端的幅度和时间上的容忍度要求就更低,正确恢复信号的概率就更高。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间