单端IO标准

单端标准

常用的单端IO标准是LVTTL和LVCMOS。

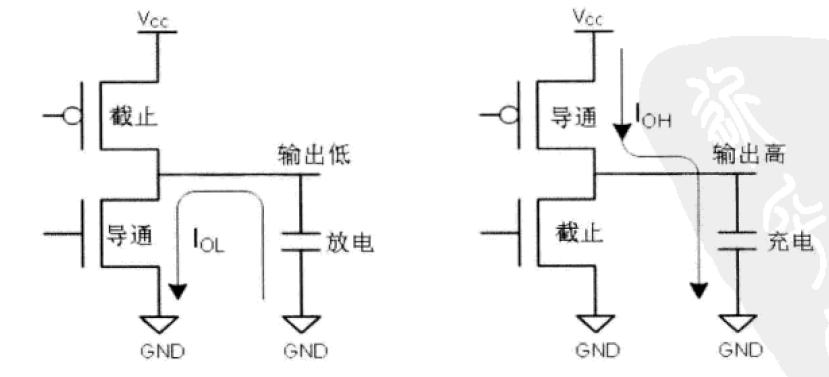

目前业界绝大部分FPGA/CPLD器件的LVCOMS的IO是由CMOS推挽(push-pull)驱动器构成的,这种结构是上面的PMOS管和下面的NMOS管组成的。当PMOS关闭,NMOS打开时,驱动器输出低电平;相反,当NMOS关闭,PMOS打开时,驱动器输出高电平。

CMOS驱动器在从输出由高到低的转换过程中,把PMOS关闭,同时把NMOS打开,这样,输出信号线与参考地平面及负载输入构成的等效电容处于放电状态,直到输出为低。CMOS驱动器在从输出低到高的转换过程中,把NMOS关闭,同时把PMOS打开。这样输出信号线与参考地平面及负载输入构成的等效电容处于充电状态,直到输出为高。LVCMOS输出的结构特点如下图:

这样输出驱动器的结构可以支持轨到轨(rail-to-rail)的输出,也就是说,可以从0~VCC,所以它的摆幅最大,相应的噪声容限也较大。

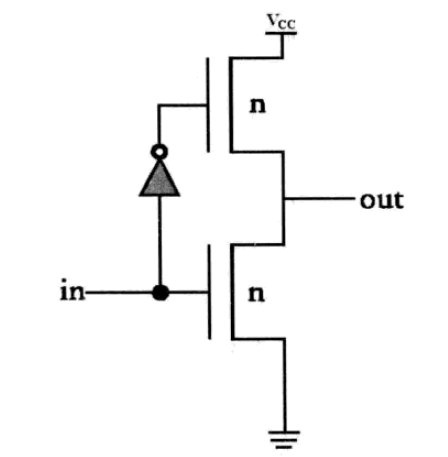

也有些MOS工艺的器件中,为了实现类似TTL图腾柱(totem-pole)结构的输出电平,上拉和下拉都采用NMOS管来实现,如下图,它的摆幅与LVCMOS相比有所降低,因此翻转速度要高一点,噪声容限没有那么大。

LVCMOS和LVTTL的电平阈值如下图。在电路中,要求输出高电平等于VOH,输出低电平等于VOL,要求输入能接收高于VIH的高电平信号,能接收低于VIL的低电平信号。

总的来说,LVTTL/LVCMOS驱动器的特点是静态电流非常小,因此其静态功耗非常低。驱动器的输出摆幅较大,翻转过程中的瞬态电流比较大,这种瞬时的大电流必然会给系统引入噪声,对系统的可靠性造成一定的影响。LVTTL/LVCMOS驱动器的动态功耗随着时钟频率的增加而呈指数增加,所以不适合应用在高速的电路中。一般来说,时钟频率在150MHz以上就很少采用这种驱动器作为输入输出了。

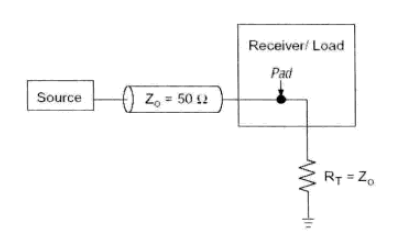

在设计LVTTL/LVCMOS的信号走线时,如果PCB走线长到需要被作为传输线来考虑,用户就应该根据自己的需要选择合适的匹配方式。

匹配的根本要求是保持信号在传输线上的阻抗连续,而防止信号在传输线上来回反射,造成接收端信号反射和振铃,影响信号的正确接收。

为了满足传输线的阻抗连续,有许多方法,各种方法的使用场合并不一样,需要用户自己选择。

具体匹配方案,请参考FPGA极客空间微信公众号,《阻抗匹配处理方式》一文。

不管是哪种匹配方式,为了保证匹配的效果,在PCB设计时,需要做到源端串阻尽量靠近驱动器管脚,而末端匹配电阻尽量靠近接收端管脚,从而尽量减小由于匹配电阻造成的短线影响信号质量。如果在一些特殊的情况下,不方便将终端电阻放置在靠近管脚的地方,也可以采用飞过(fly-by)的方式加电阻。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

浙公网安备 33010602011771号

浙公网安备 33010602011771号