全差分运放阻抗匹配计算(四)

最近在使用全差分运放AD8132对高频和低频信号进行处理过程中,一度对全差分运放再度陌生,在对芯片资料进行详细阅读分析以及参考网络博客的过程中,逐渐揭开了全差分运放的神秘面纱。

全差分放大器 (FDA):即指输入和输出都是差分信号的运放,其优点为能提供更低的噪声,较大的输出电压摆幅和共模抑制比,可较好地抑制谐波失真的偶数阶项等。

在使用中,单端信号输入差分信号输出。

AD8132建议电阻值和噪声性能,从上表可以看出,增益越大,带宽降低,噪声升高。

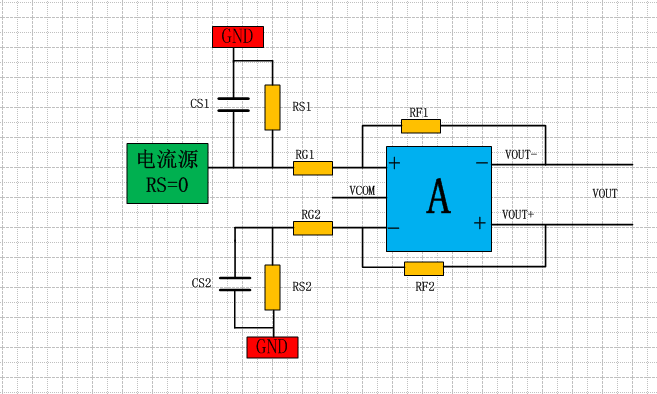

在项目设计中,输入信号源为电流源,为了能将电流转换为电压,并且能够提高电压,而且要限制电压范围,满足带宽以及噪声的情况下,输入阻抗必须增大。

如上图,电流源内阻为0,为了将电流转换为电压,并且提高输入电压,RF及RG设置在K级别(RG=RF),为了限制电压范围,使用RS进行分流,为了同时满足高频信号以及低频信号,加入电容CS。通过截止频率F0=1/2*PI*R*C,得到低通滤波器的电容值。

当信号为低频时,电容相当于断路,此时可以把电路等效为纯电阻电路,算出阻值限制输出电压范围。

当信号为高频时,选择合适的电容值,某些高频信号通过电容到地,此时可以将电容理解为分压电容,对输入的高频信号进行限压。

为了满足全差分运放输入的完全对称,运放输入的另一端也必须做出相应的匹配,如上图。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间