Verilog中的UDP

概述

Verilog HDL语言提供了一种扩展基元的方法,允许用户自己定义元件(User Defined Primitives,UDP)。通过UDP,可以把一块组合逻辑电路或者时序逻辑电路封装在一个UDP内,并把这个UDP作为一个基本的元件来使用。需要注意的是,UDP不能综合,只能用于仿真。

UDP的定义与调用

UDP定义的语法和模块定义类似,但由于UDP和模块同属于同级设计,因此,UDP定义不能出现在模块之内。UDP定义使用由关键词primitive和endprimitive封装起来的一段代码,这段代码定义了该UDP的功能。这种功能的定义是通过表来实现的,即在这段代码中有一段处于 关键词table和endtable之间的表,用户可以通过设置该表来规定UDP的功能。

UDP的定义格式如下:

primitive<元件名称>(<输出端口名>,<输入端口名1>,输入端口名1>...输入端口名n>);

输出端口类型声明(output);

输入端口类型声明(input);

输出端口寄存器 变量说明(reg);

元件初始状态说明(initial);

table

<table 表项1>;

<table 表项2>;

......

<table 表项n>;

endtable

endprimitive

与Verilog HDL中的模块相比,UDP具有以下特点:

(1)UDP的输出端口只能有一个,且必须位于端口列表的第一项。只有输出端口能定义为REG类型。

(2)UDP的输入端口可有多个,一般时序电路UDP的输入端口最多9个,组合电路UDP的输入端口可多至10个。

(3)所有端口变量的位宽必须是1比特。

(4)在table表项中,只能出现0,1,x这三种状态,z将被认为是x状态。

根据UDP包含的基本逻辑功能,可以将UDP分为组合电路UDP、时序电路UDP及混合电路UDP,这几类UDP的差别主要体现在table表项的描述上。

UDP的调用和verilog HDL中模块的调用方法相似,通过位置映射。其语法格式如下:

UDP名 例化名(连接端口1信号名,连接端口2信号名,连接端口3信号名,...);

UDP定义的全加器

组合逻辑电路的功能列表类似真值表,规定了不同的输入值和对应的输出值,表中每一行的形式是"output ,input1,input2...",排列顺序与端口列表中的顺序相同。组合电路UDP的输入端口可多至10个。如果某个输入,输出组合没有定义输出,那么就把这种情况的输出置位x。

3选1多路选择器

?代表不必关心相应变量的具体值。

UDP原语中可以使用的值

UDP还可以描述具有电平触发和边沿触发特性的时序电路。时序电路拥有内部状态序列,其内部状态必须用寄存器变量进行建模,该寄存器的值就是时序电路的的当前状态,它的下一个状态是由放在基本功能列表中的状态转换表决定的,而且寄存器的下一个状态就是这个时序电路UDP的输出值。所以时序电路UDP由两部分组成——状态寄存器和状态列表,定义时序电路UDP的工作也分为两部分——初始化状态寄存器和描述状态列表。

在时序电路的UDP描述中,01、0x、x1代表着信号的上升沿。

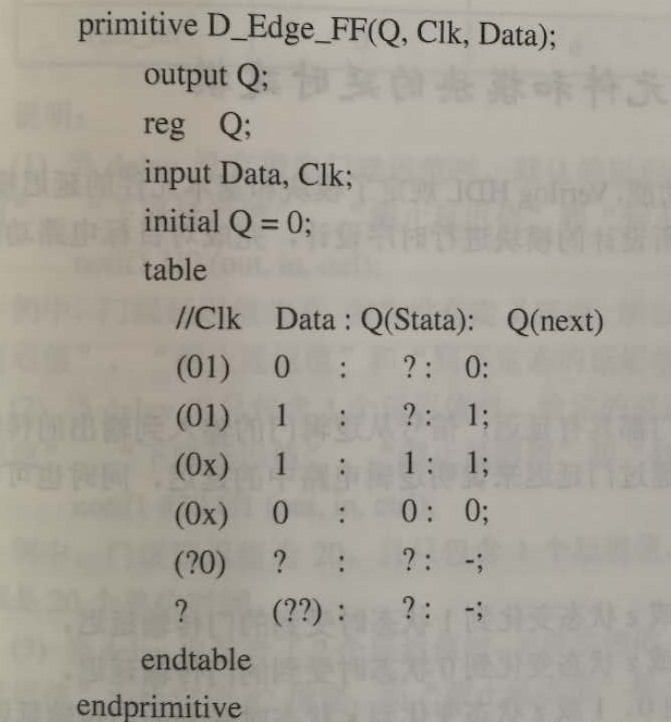

通过verilog hdl语言给出D触发器的UDP描述

表项(01)表示从0转换到1,表项(0x)表示从0转换到x,表项(?0)表示从任意值转换到0,表项(??)表示任意转换。对于未定义的转换,输出默认为x,假定D_Edge_FF为UDP定义,则它现在就能够像基本门一样在模块中使用。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

浙公网安备 33010602011771号

浙公网安备 33010602011771号