FPGA前世今生(二)

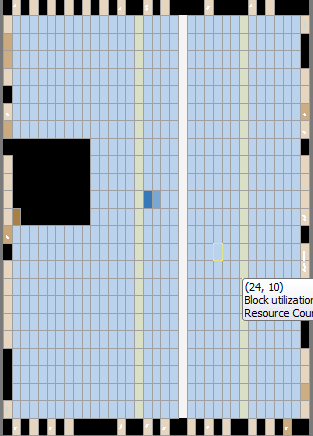

上期我们介绍了关于FPGA内部最基本的结构,在quartus下可以看到整体的结构。

这是在平面规划图下看到的结构,其中蓝色的小格代表一个LAB。四周边上浅棕色的小格代表IO口。

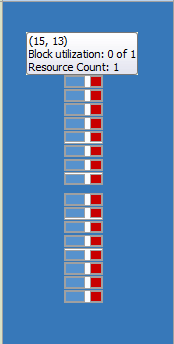

这是一个LAB的内部结构,其中蓝色小格和红色小格就是一个LE,一个LAB有16个LE组成。

从上图可以看到,一个LE包含一个4输入的LUT,一个进位逻辑和一个输出寄存器。

接下来我们介绍一下FPGA与外部通信的接口,IO口。FPGA内部有丰富的资源,一个很重要的资源就是可编程输入输出单元(IOB)。是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配要求, FPGA内的I/O按组分类,每组都能够独立地支持不同的I/O标准。

通过软件的灵活配置,可适配不同的电气标准与I/O物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。目前,I/O口的频率也越来越高,一些高端的FPGA通过DDR寄存器技术可以支持高达2Gbps的数据速率。

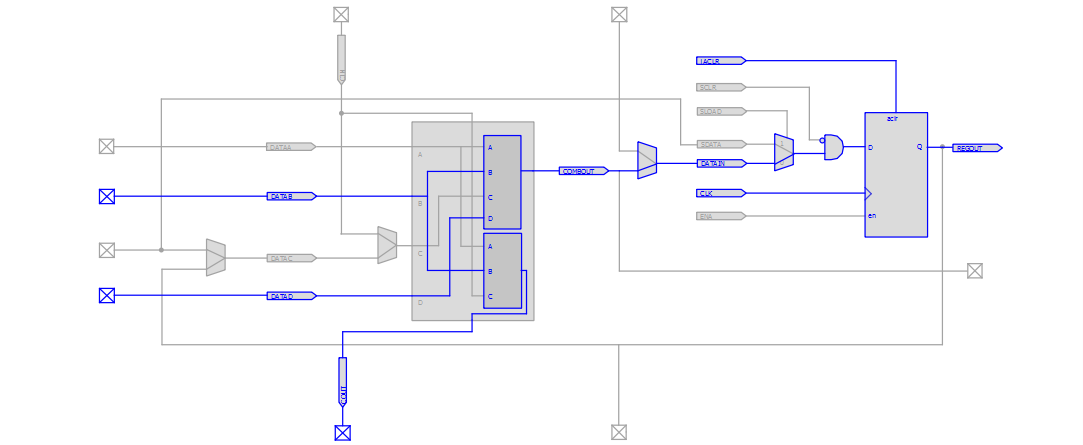

在QUARTUS下我们可以看到IO口的DDR寄存器。

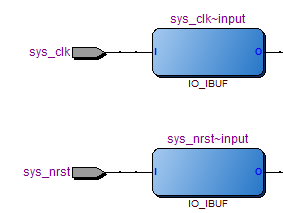

外部输入信号可以通过IOB模块的存储单元输入到FPGA的内部,也可以直接输入FPGA 内部。FPGA内部有输入、输出缓冲,可以提高信号的驱动力。

如上图我们可以看到,IO_IBUF是输入缓冲,加载在系统时钟和系统复位输入引脚上,提高这两个信号的负载能力。在ALTERA FPGA内部,对于系统时钟的输入缓冲是系统自己加入的。当使用普通IO口时,这个缓冲需要人为加入。当外部输入信号经过IOB模块的存储单元输入到FPGA内部时,其保持时间(Hold Time)的要求可以降低,通常默认为0。

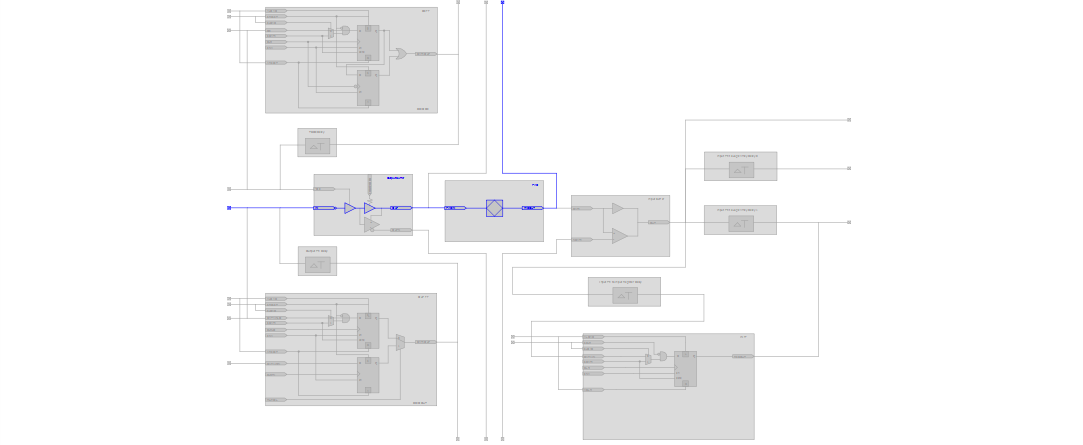

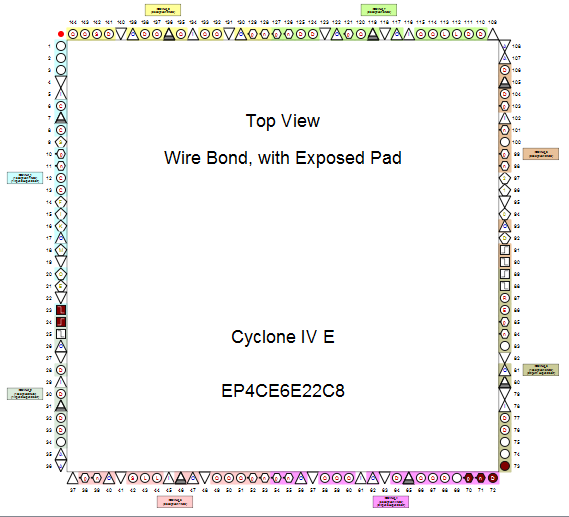

为了便于管理和适应多种电器标准,FPGA的IOB被划分为若干个组(bank),每个bank的接口标准由其接口电压VCCO决定,一个bank只能有一种VCCO,但不同bank的VCCO可以不同。只有相同电气标准的端口才能连接在一起,VCCO电压相同是接口标准的基本条件。

如上图,通常IOB分为8个BANK,每个BANK都可以独立的支持不同的电气标准。

版权所有权归卿萃科技,转载请注明出处

作者:卿萃科技ALIFPGA

原文地址:卿萃科技FPGA极客空间 微信公众号

扫描二维码关注卿萃科技FPGA极客空间