第一章 计算机系统概述

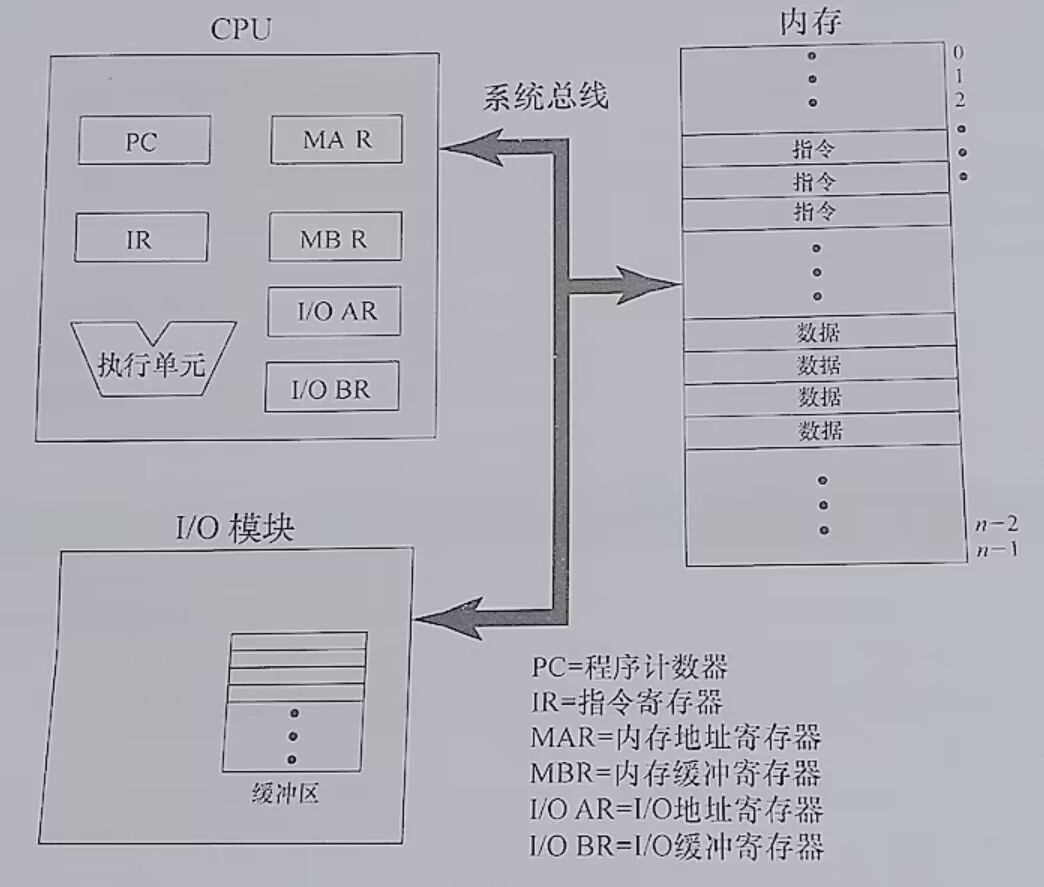

一. 基本组成

1. 计算机包含四个主要的结构:

-

处理器:控制计算机的操作,并执行数据处理的功能。当只有一个处理器时,被称为中央处理单元(cpu)

-

内存:存储数据和程序。这种存储通常易失,关机时内存数据会丢失。磁盘存储器中的数据即使计算机系统关闭也会被保留。内存称为主存,硬盘为辅存

-

I/O模块:在计算机和外部环境之间交换数据。外部环境有:辅存(如磁盘)、通信设备、终端

-

系统总线:提供处理器、主存、I/O模块之间的通信

2. 处理器的一个功能是与内存交换数据

它通常使用两个内部寄存器:

- 内存地址寄存器MAR。指定下一条读/写程序的内存地址

- 内存缓冲寄存器MBR(也叫MDR)。存放将写入内存/从内存读取的数据

3. 内存由一组顺序编号的、有地址定义的单元的组成

每个单元都包含一个二进制数,代表一条指令或数据。

4. I/O模块

I/O模块在外部设备与处理器、内存之间传输数据。它有一个内部缓冲区,用于临时存储传输前的数据

二. 微处理器

微处理器是部署在单个芯片上的处理器。

如今微处理器发展成了多处理器。每个芯片(称为插槽,Socket)上包含多个处理器(称为核心,Core)

三. 指令的执行

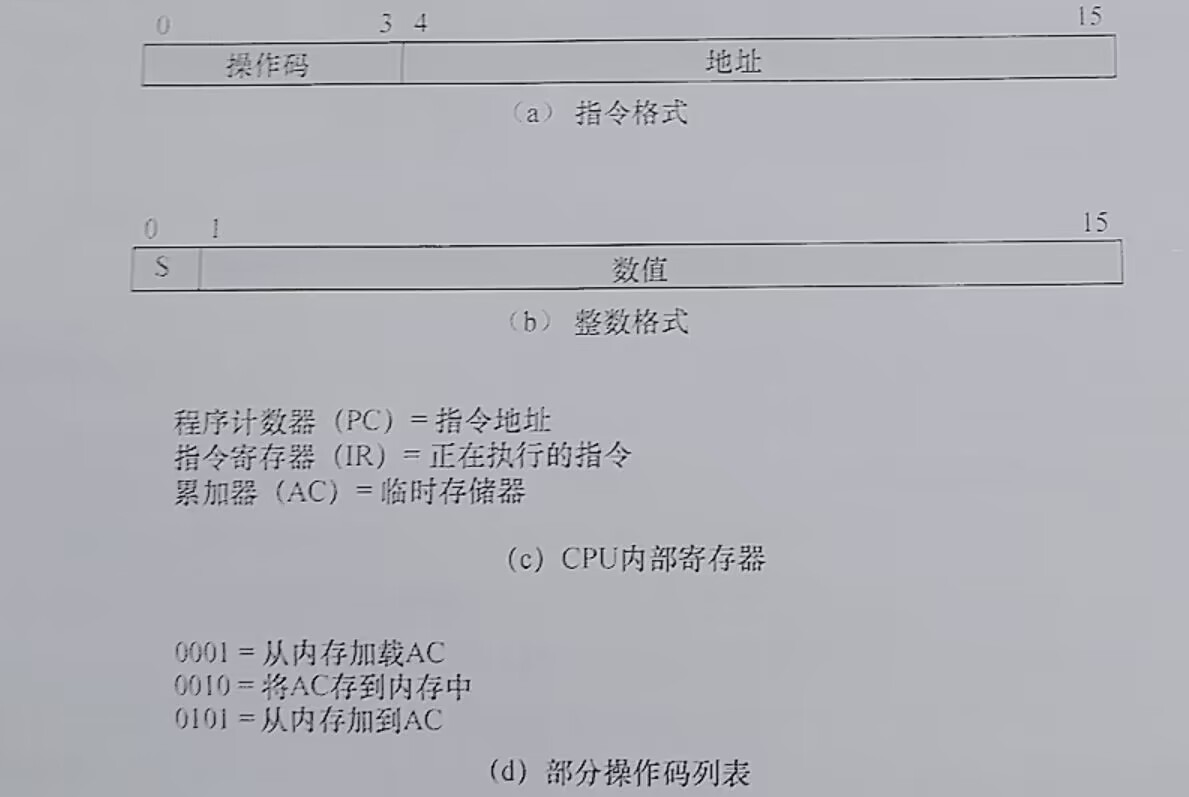

1. 处理器执行的程序由一组保存在存储器中的指令组成。

指令的执行分为两步:

- 处理器每次从存储器中读取一条指令

- 执行指令

程序的执行就是重复的读取和执行指令的过程

一条指令的处理过程称为一个指令周期(取值阶段+执行阶段)

2. 指令周期全过程

-

每个指令周期开始时,处理器从内存中读取一条指令。

-

程序计数器PC(保存下一次需读取的指令地址)累加,以便顺序获取下一条指令的地址

-

读取的指令存放在处理器的指令寄存器IR中。

-

指令中包含用于指定处理器将要执行操作的信息,处理器解释该指令并执行对应的操作

四. 中断

中断就是CPU停下当前的工作任务,去处理其他事情,处理完后回来继续执行刚才的任务

通常大多数I/O设备都比处理器要慢很多。比如处理器向打印机传送数据,则每次写操作完成后处理器必须暂停使用直至打印机完成打印操作。这期间处理器将一直处于空闲状态,这段时间非常长,对处理器的使用造成极大浪费。

中断流程

- 中断请求:外部设备准备就绪(准备从处理器接收更多数据)时,该设备的I/O模块给处理器发送中断请求信号

- 中断响应:处理器暂停当前程序的执行

- 保护现场:标出该中断的产生点

- 中断处理:调用一个程序服务于该I/O设备,这个程序叫中断处理程序

- 恢复现场:在对该设备的服务响应完成后,恢复原有程序的执行。

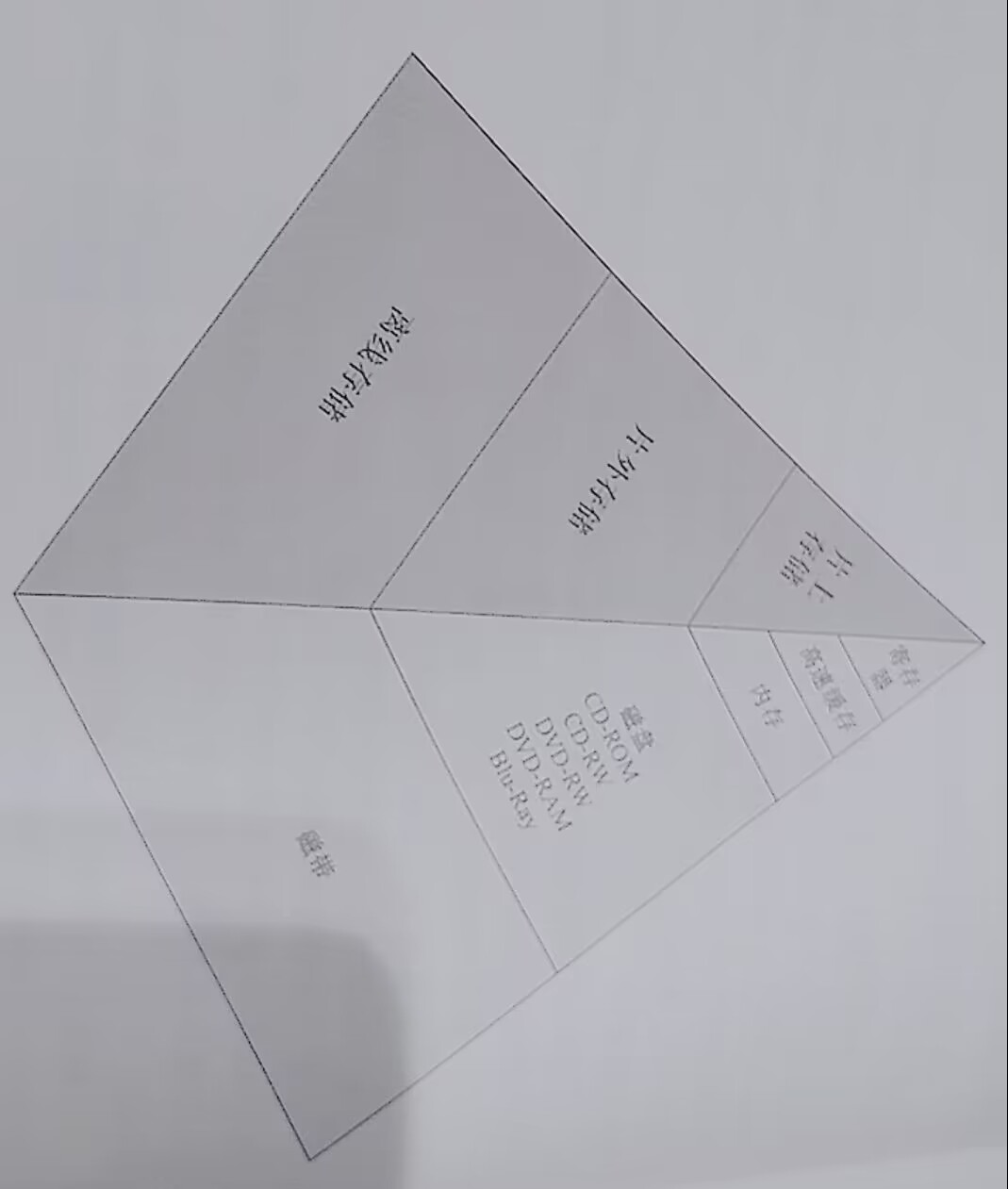

五. 分级存储体系

存储器往往需要权衡三个因素:容量、访问时间、成本

- 存储时间时间越快,单位(每比特位)成本越高

- 容量越大,单位(每比特位)成本越低

- 容量越大,存取速度越慢

1. 分级存储体系结构

随着层次下移,具有如下特征:

a. 单位成本逐层递减

b. 容量逐层递增

c. 访问时间逐层递增

d. 处理器访问存储器的频率逐层递减

特征d的有效基础是访问的局部性原理:CPU访问存储器时,无论是存取指令还是存取数据,所访问的存储单元都趋于聚集在一个较小的连续区域中

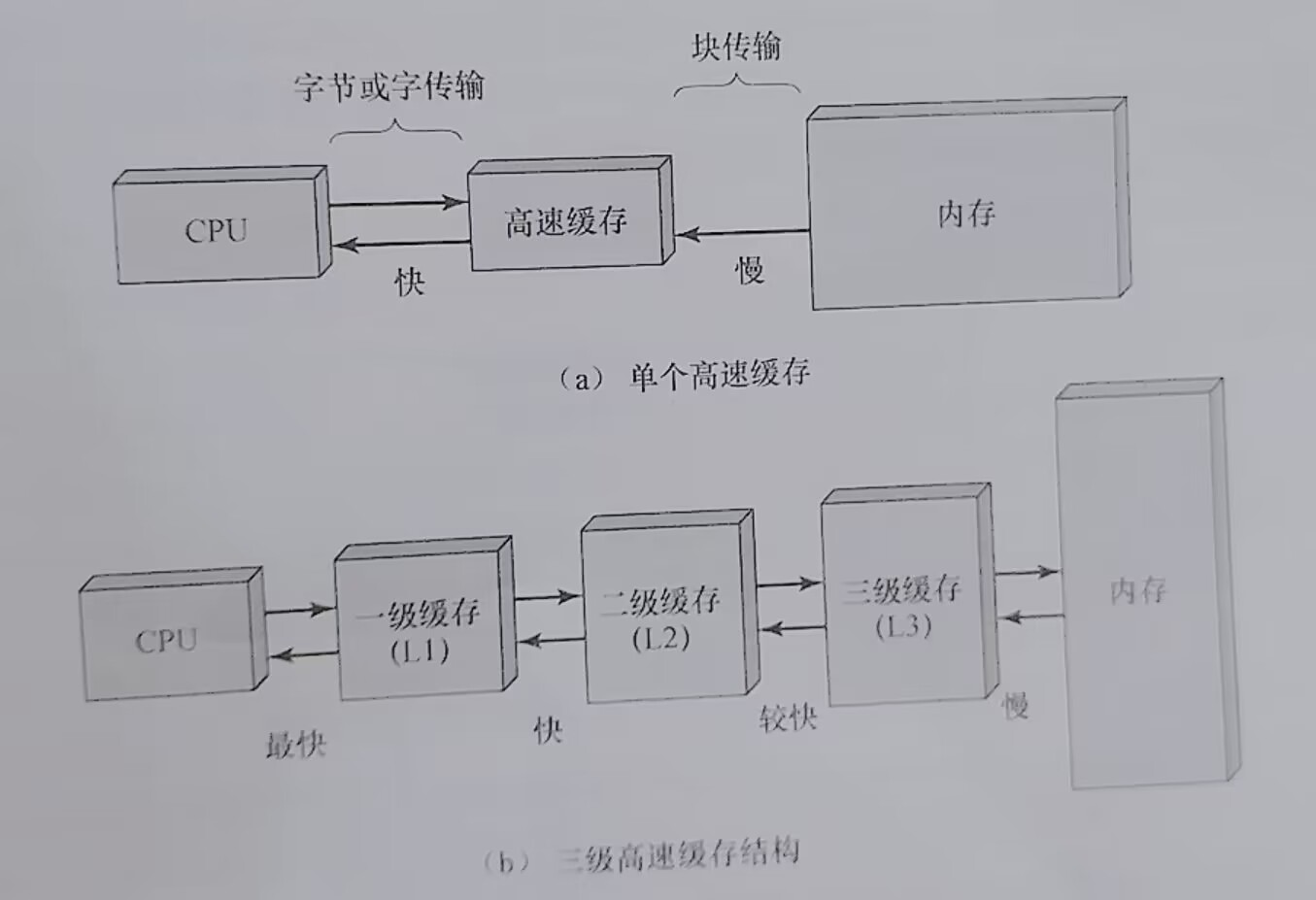

六. 高速缓存

处理器的运行速度和内存的访问速度极不匹配。解决方法是利用局部性原理在处理器和内存之间提供一个容量虽小、但速度较快的存储器,即高速缓存。

高速缓存的原理

- 高速缓存包含一部分主存数据的副本。

- 当处理器试图读取内存中的一个字节或字时,首先会检测该数据是否在高速缓存中。

- 如果在,该字节或字将从高速缓存传递给处理器,否则处理器会先将包含该字节或字的、固定大小的内存块数据读入高速缓存,然后再将该字节或字从高速缓存交给处理器。

- 由于存在数据访问的局部性现象,当一个数据块被载入高速缓存以满足一次存储访问需求后,可能会继续多次访问该数据块,以获取位于该块的其他字节信息

七. 直接内存访问

当处理器正在执行程序时并遇到一条与I/O相关的指令时,它通过给相应的I/O模块发命令来执行这条指令。

I/O模块执行请求的动作并设置I/O状态寄存器中相应的位,不执行其他操作来通知处理器,不会中断处理器的执行。

因此处理器在执行I/O指令后,需要周期性地检测I/O模块的状态,以确定I/O操作是否已经完成

直接内存访问(Direct Memory Access)DMA

当需要移动大量数据时,我们可以让I/O设备与计算机内存进行直接数据交换。而CPU则可以去忙别的事情。这种将CPU的介入减少的I/O模式称为直接内存访问。

- DMA工作模式:

- 处理器尝试读或写一块数据,产生一条命令,向DMA发送如下信息:

- 是否请求读或写操作

- 需要访问的I/O设备地址

- 读/写数据的内存起始地址

- 读/写数据的长度(字数)

- 处理器把读/写操作委托给DMA模块,由该模块处理相关操作,之后处理器继续其他的工作。

- DMA直接与存储器交互(不通过处理器),传输整个数据块,每次传递一个字的内容

- 传输完成后,DMA模块向处理器发送中断信号。因此,只有在传输的开始和结束这两个时间点,处理器才会参与相关处理工作。

八. 多处理器和多核组织结构

一般情况下计算机被视为一台顺序执行的机器。处理器按顺序一条一条地执行机器指令来完成程序的执行。

但在微操作级别,同一时间会产生多个控制信号。指令流水线技术在一定程度上可以重叠取指和执行操作的执行。这都是并行执行的例子

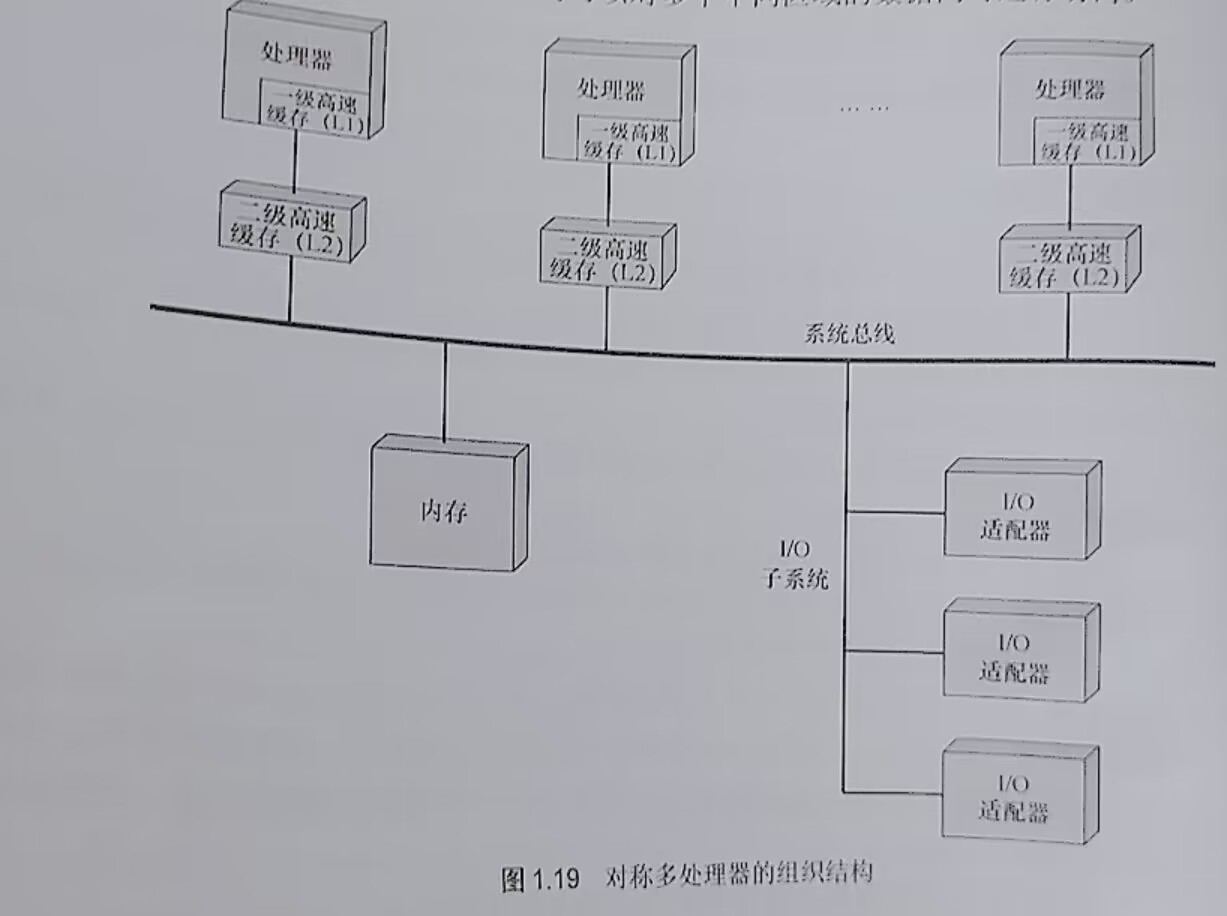

1. 对称多处理器SMP

- 具有两个或两个以上性能相当的处理器

- 处理器共享内存和I/O设备,通过总线或其他内部连接方式互连

- 整个系统由操作系统进行控制

2. 多核计算机

多核计算机也称为单芯片多处理器,是指在一块硅上组装两个或多个处理器(核)

每个核包含组成一个独立处理器的所有组件。

浙公网安备 33010602011771号

浙公网安备 33010602011771号