STM32数据手册分析-以STM32F103C8T6为例

特点

- Modified Havard架构

"Modified Harvard" 架构是一种计算机体系结构,它结合了哈佛架构和冯·诺依曼架构的特点。它具有以下主要特点: 1. 分离的指令存储器和数据存储器:与哈佛架构一样,Modified Harvard 架构也将指令和数据存储在不同的存储空间中。这样可以实现并行访问,提高系统性能。 2. 共享的存储器地址空间:与纯粹的哈佛架构不同,Modified Harvard 架构将指令存储器和数据存储器映射到一个统一的地址空间中。这样可以保证指令和数据都能访问整个存储空间。 3. 允许指令和数据共访问:在某些情况下,Modified Harvard 架构允许指令存储器和数据存储器共享访问,比如访问存储在指令存储器中的常量数据。这增加了系统的灵活性。 4. 兼容冯·诺依曼架构:Modified Harvard 架构保留了一些冯·诺依曼架构的特点,如使用统一的地址空间以及允许指令和数据共访问等。这使得它可以很好地兼容冯·诺依曼体系结构的软件和编程模型。 总的来说,Modified Harvard 架构试图在性能、灵活性和兼容性之间达到一种平衡。ARM Cortex-M 系列处理器就采用了这种修改过的哈佛架构,非常适合嵌入式系统的设计需求。 - 32bit

32位单片机的数据总线、地址总线和ALU都是32位宽度。 - 主频 72Mhz

- 1.25DMIPS/MHz

-

DMIPS (Dhrystone MIPS)是一种基准测试,用于测量微控制器的整数计算性能。它是基于Dhrystone基准测试程序计算出来的。 1.25 DMIPS/MHz 表示,在1 MHz的时钟频率下,该微控制器可以达到1.25 DMIPS的性能水平。 这个指标越高,意味着微控制器的整数计算性能越强。它是衡量微控制器性能的一个比较重要的参数。 ARM Cortex-M0+ 微控制器通常有 0.9 DMIPS/MHz 的性能 ARM Cortex-M4 微控制器通常有 1.25 DMIPS/MHz 的性能 ARM Cortex-M7 微控制器通常有 2.14 DMIPS/MHz 的性能 - Cortex-M3架构

性能:Cortex-M4的性能比Cortex-M3提高了20%,在相同的速度下运行,Cortex-M4的每指令周期数(CPI)更低,因此在相同的MHz下可以做更多的工作,或者在同一个应用中需要更低的主频。 浮点运算能力:Cortex-M4具有一个专用浮点运算单元(FPU),而Cortex-M3没有硬件浮点单元,因此无法直接执行浮点运算,不过可以通过软件库来实现浮点数计算。 DSP指令集:Cortex-M4支持SIMD指令集,所有指令都能在单个周期内执行,而Cortex-M3需要多个指令和多个周期才能完成的等效功能。 中断处理:Cortex-M4采用了尾链技术,使得背靠背(back-to-back)中断的响应只需要6个时钟周期,而Cortex-M3则需要大于30个周期。 - stm32对乘除法有优化

Single-cycle multiplication and hardware division - 64Kbytes的flash大小

- 20Kbytes的sram大小

- 3.3V供电 但是部分IO兼容5v的输入

引脚的I / O Level标注为FT的可以容许5V输入 - 对电源稳定性有帮助的复位设计和电源电压检测

POR(Power On Reset,上电复位): 当STM32芯片的电源(VDD)从0开始上升时,在VDD电压上升到规定的阈值(不同型号STM32可能存在差异,比如在一些资料中提到典型值在1.7 - 1.9V左右 )之前,POR会保持芯片处于复位状态,防止芯片在电源不稳定、未达到正常工作电压时就开始运行程序造成不可预期的错误等。当VDD越过这个阈值后,经过一小段时间(复位滞后时间 一般几个毫秒,例如2.5ms常见),芯片结束复位状态并从复位向量地址开始执行指令。 PDR(Power Down Reset,掉电复位): 当VDD电压从正常工作电压开始下降,下降到特定阈值(例如典型值为1.6 - 1.8V左右 ,比POR阈值略低,如有的资料提到POR阈值 - PDR阈值 = 40mV)之后,STM32内部会产生复位信号,进行掉电复位操作。它的目的是在电源逐渐失去的过程中尽可能使芯片处于相对有序的状态而不是处于混乱的中间态等情况。 PVD(Programmable Voltage Detector,可编程电压检测器) : 可以通过编程配置来监视供电电压。 当检测到供电电压下降到所编程设定的阈值以下时,会产生一个中断信号(连接到外部中断线EXTI16)通知软件系统,以便软件可以执行紧急处理操作(如保存关键数据等) 。 当供电电压又恢复到给定的阈值以上时(上升阈值和下降阈值存在差值,防止在阈值附近波动频繁触发中断 ,有迟滞参数),也会产生一个中断,通知软件供电恢复。 它的配置参数包括设置检测的电压阈值等级、中断触发模式(上升沿、下降沿、双边沿触发等)等。 - 内部8Mhz高速晶振RC振荡器,40khz低速时钟源

工厂校准 (Factory-trimmed): 出厂时,STM32 的内部 RC 振荡器已经过工厂校准,可以提供非常精确的 8 MHz 时钟频率。 不需要额外的外部元件或校准步骤。 稳定性: 内部 RC 振荡器的频率稳定性比外部晶振要好。 它可以在宽范围的工作电压和温度条件下保持稳定的频率。 低功耗: 内部 RC 振荡器的功耗非常低,比外部晶振要节省功耗。 这使其非常适合于电池供电的嵌入式应用。 快速启动: 内部 RC 振荡器可以快速启动,在上电后很快就能达到稳定的频率输出。 这对于需要快速启动的应用场合非常有用。 - 低功耗有三种模式

Sleep(睡眠)模式: 内核停止运行,但外设(如定时器、串口等)仍可工作。 唤醒速度较快,通常在几个微秒到几十微秒之间。 电流消耗相对较低,但仍高于 Stop 和 Standby 模式。 例如,在系统暂时不需要进行大量计算,但仍需要周期性地检测外部事件或接收数据时,可以使用 Sleep 模式。 Stop(停机)模式: 内核停止,大多数时钟也被关闭,只有少数内部低速时钟源保持运行。 功耗进一步降低,比 Sleep 模式更低。 唤醒时间相对较长,一般在几十微秒到几百微秒。 可以通过外部中断、RTC 闹钟事件等唤醒。 比如,系统在较长时间内不需要运行,但需要在特定事件发生时快速唤醒,可选择 Stop 模式。 Standby(待机)模式: 几乎所有的时钟都被关闭,仅保留备份域的少量电路工作。 功耗极低,是三种模式中功耗最低的。 唤醒时间最长,通常需要几毫秒甚至更长。 可以通过外部复位引脚、RTC 闹钟事件、IWDG(独立看门狗)复位等唤醒。 当系统需要长时间处于超低功耗状态,且对唤醒时间要求不高时,Standby 模式是合适的选择。 - 2x 12-bit, 1 µs A/D converters,一个adc有8个通道,一共16个通道,注意有一个通道是可以连接到内部的温度传感器的,可以反应CPU的温度

- 七通道的DMA

DMA

– 7-channel DMA controller

– Peripherals supported: timers, ADC, SPIs,I2Cs and USARTs

- 80个IO都支持快速模式且都容忍5V的输入

Up to 80 fast I/O ports all mappable on 16external interrupt vectors and almost all5 V-tolerant- 支持Jtag和SWD调试

引脚数量: JTAG 接口通常需要较多的引脚,一般包括 TCK(测试时钟)、TMS(测试模式选择)、TDI(测试数据输入)、TDO(测试数据输出)和 TRST(测试复位,可选)。 SWD 接口只需要两根线,分别是 SWCLK(串行时钟线)和 SWDIO(串行数据线)。 调试速度: 在一些情况下,JTAG 的调试速度可能相对较慢。 SWD 通常能提供较高的调试速度,尤其在对速度要求较高的应用中表现更优。 占用资源: 由于引脚数量较多,JTAG 会占用更多的微控制器引脚资源。 SWD 因为引脚少,对引脚资源的占用相对较少,这在引脚资源紧张的情况下是一个显著的优势。 兼容性: JTAG 是一种较为传统和通用的调试接口,被广泛支持。 虽然 SWD 相对较新,但大多数现代的调试工具和微控制器也都支持。 例如,在一个小型的嵌入式系统中,如果微控制器的引脚资源有限,为了节省引脚并实现高效调试,开发者可能会优先选择 SWD 接口。 而在一些对兼容性要求极高,或者使用的调试工具只支持 JTAG 的情况下,则会选择 JTAG 接口。 - 具有CRC16计算单元

- 具有96bit的专属ID

- 封装为LQFP48,带引脚尺寸约10*10mm

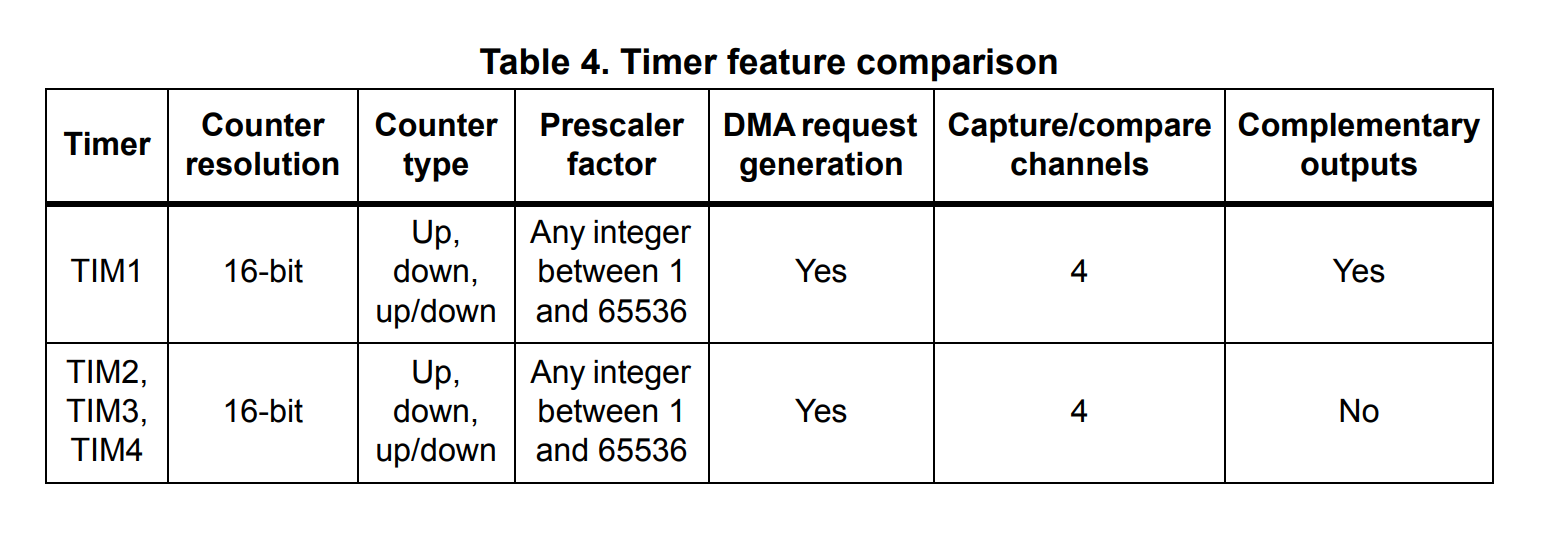

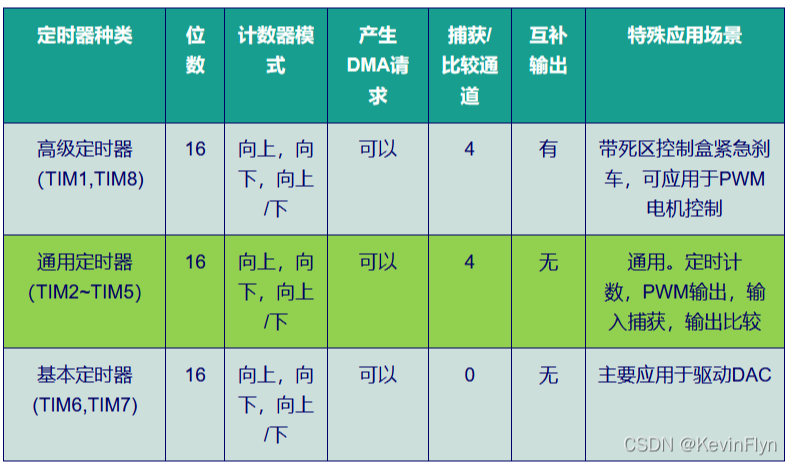

- 一个高级定时器,三个通用定时器,两个看门狗定时器,一个systick定时器

独立看门狗(IWDG)是 12 位的递减计数器

窗口看门狗(WWDG)是 7 位的递减计数器

而 SysTick 定时器是 24 位的递减计数器。2xIIC(可用于系统管理总线SMBUS,电源管理总线PMBUS)

3xUSART

2xSPI

1xCAN(2.0B)

1xUSB2.0(full speed)

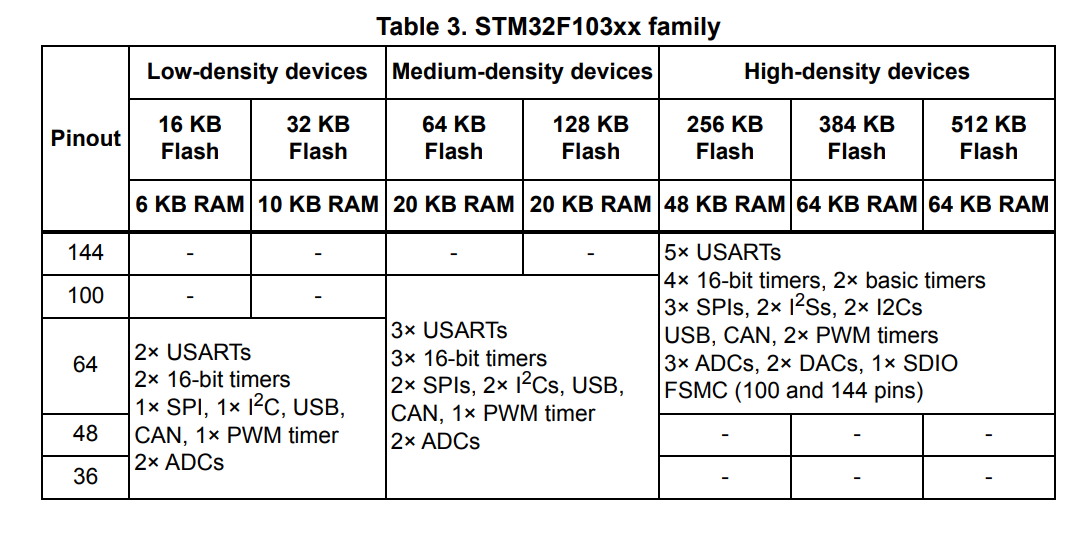

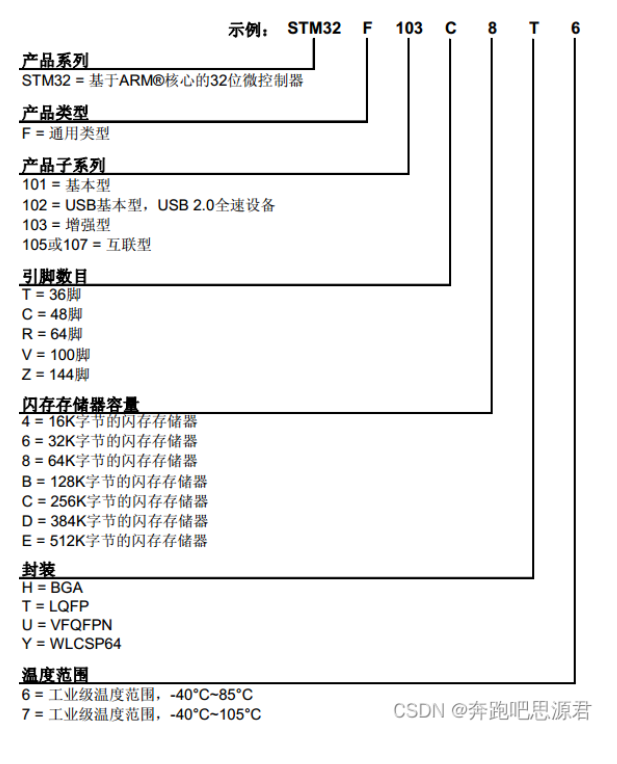

系列说明(family)

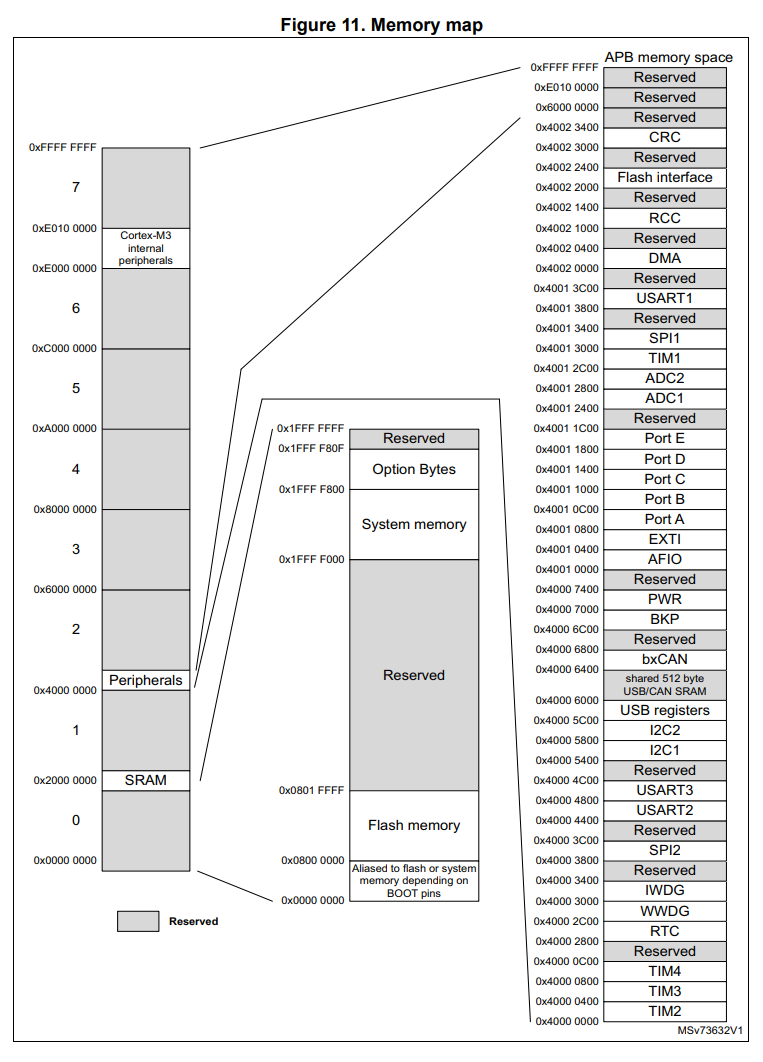

地址空间(Memory mapping)

映射后从底部0x0000 0000到0xFFFF FFFF依次为:

- 0x0000 0000 - 0x2000 0000-1

- 0x0000 0000 - 0x0800 0000-1 系统存储器,包含厂家固化的一小段bootloader,可以进行串口的下载,不可更改

- 0x0800 0000 - 0x0802 0000-1 片上Flash区域,前半段用于包含用户编程的程序,后半段一般是空白,并被置为0xFF,MDK中可以指定每次烧录时候是全片擦除函数选区擦除

- 0x2000 0000 - 0x2000 5000-1 SRAM地址(20KB的大小)20*1024 = 20480 (bytes),因此结束地址0x20000000 + 0x5000 - 1 = 0x20004FFF

- 0x4000 0000 - 0x4002 3400-1 外设寄存器地址

- 0xE000 0000 - 0xE010 0000-1 cortex-M3内核地址

- 其他地址:保留

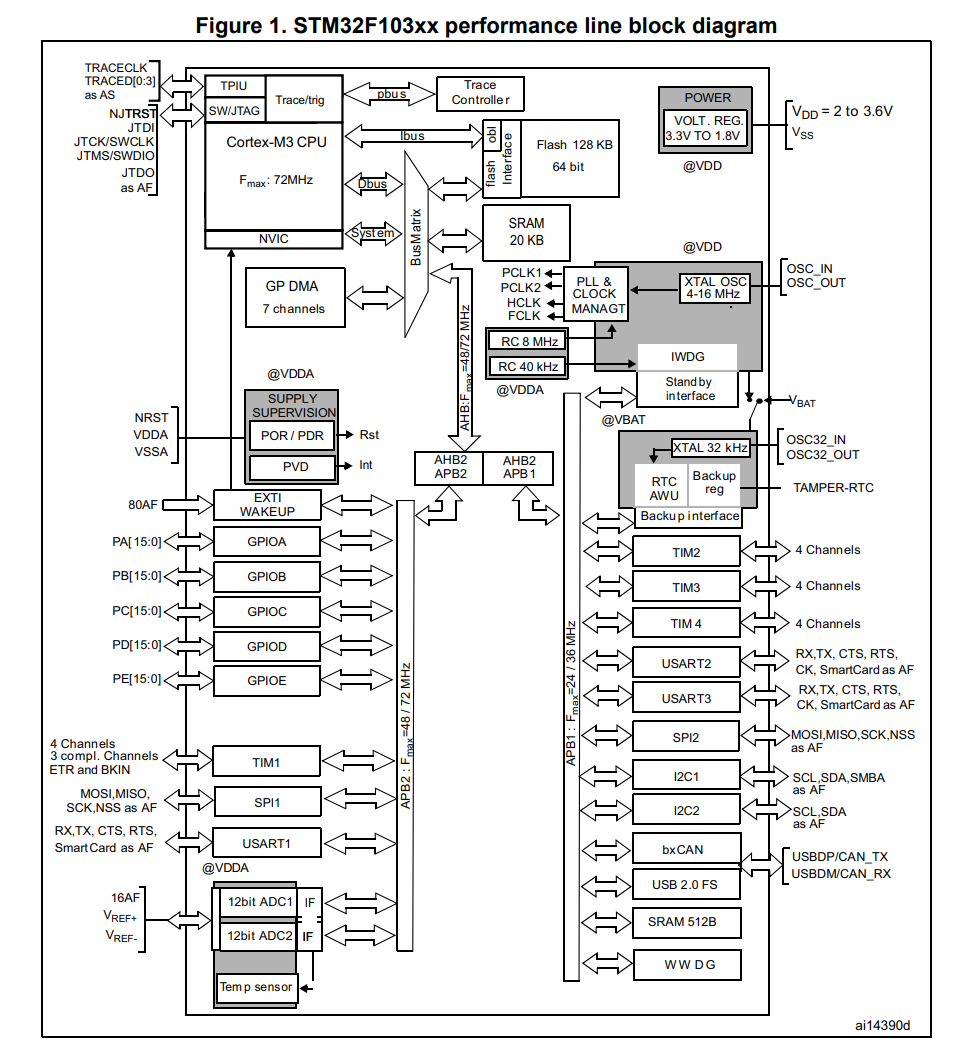

功能线框图

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具