T触发器,JK触发器的verilog实现

实现的话主要是根据特征方程

module JK_FF( clk, rst_n, J, K, Q ); input clk; input rst_n; input J; input K; output reg Q; always@(posedge clk or negedge rst_n) begin if(!rst_n) Q<=1'b0; else Q<=(J&~Q)|(~K&Q); end /*查找表 always@(posedge clk) case({J,K}) 2'b00:Q<=Q; 2'b01:Q<=1'b0; 2'b10:Q<=1'b0; 2'b11:Q<=~Q; endcase */ endmodule

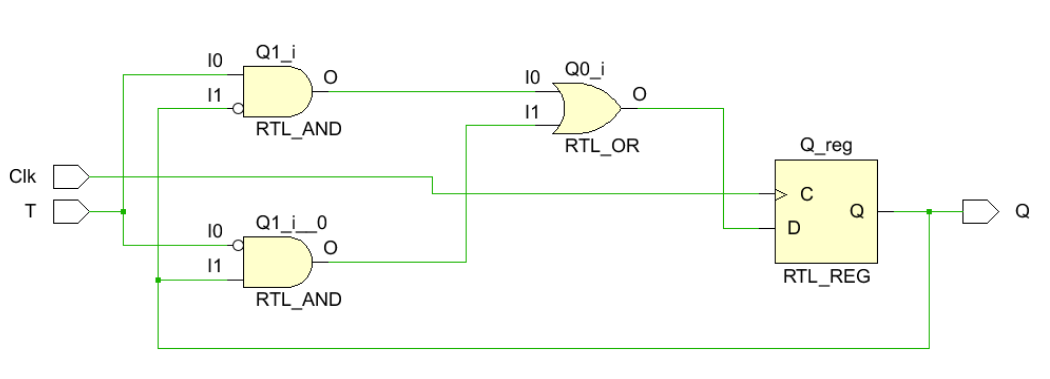

module T_FF( clk, rst_n, T, Q ); input clk; input rst_n; input T; output reg Q; always@(posedge clk or negedge rst_n) begin if(!rst_n) Q<=1'b0; else Q<=(T&~Q)|(~T&Q); end /*查找表 always@(posedge clk) if(T==1'b1) Q<=~Q; else Q<=Q; */ endmodule

YKJIAO

浙公网安备 33010602011771号

浙公网安备 33010602011771号