sequence_check_2bit_tb——lexin

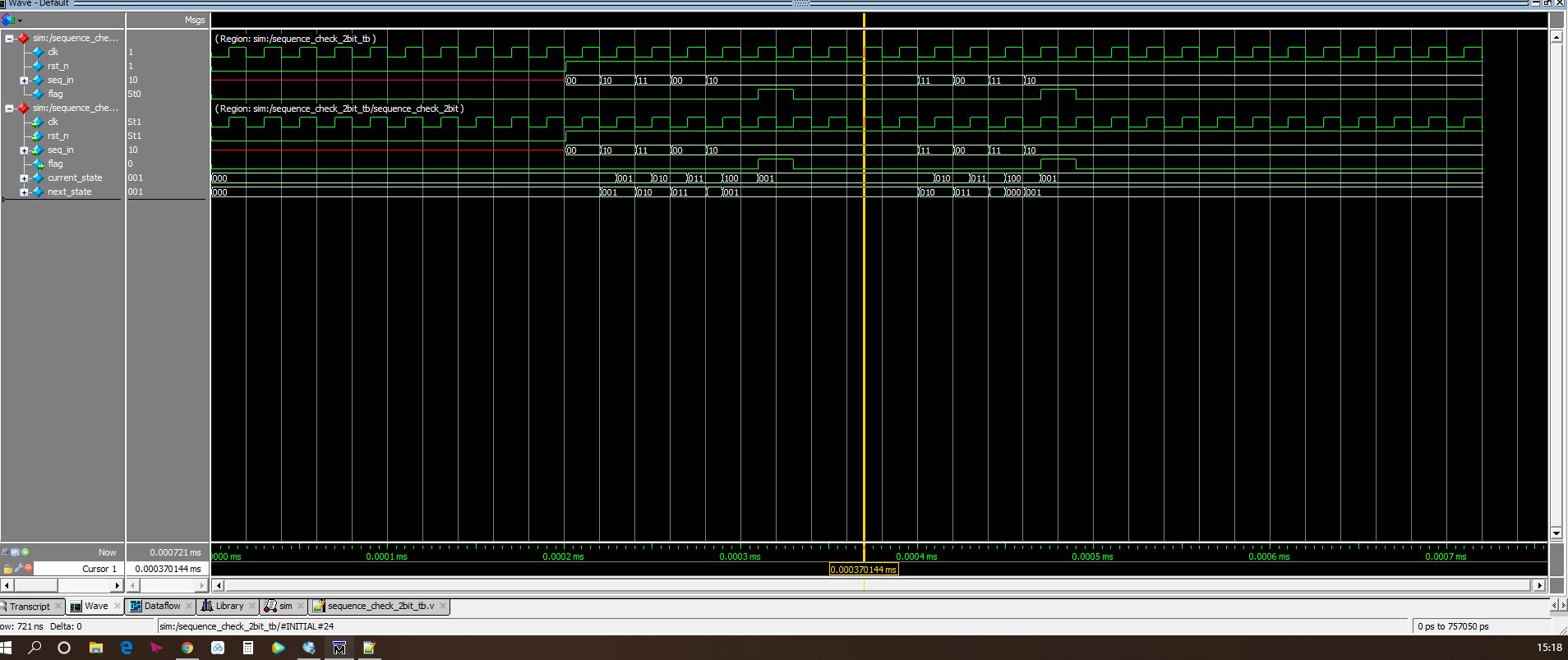

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Engineer: connor jiao // Create Date: // Design Name: // Module Name: // Function :请实现对(1011001)的2序列检测功能,模块每拍并行输入2bit, //且顺序为高位先输入,当检测到序列,输出一拍高电平脉冲。请用Verilog描述该模块。 //相当于检测10_11_00_1X // Revision 0.01 - File Created // Additional Comments: ////////////////////////////////////////////////////////////////////////////////// module sequence_check_2bit( clk, rst_n, seq_in, flag ); input clk; input rst_n; input [1:0]seq_in; output reg flag; localparam [2:0]IDLE=3'b000, S1=3'b001, S2=3'b010, S3=3'b011, S4=3'b100; reg [2:0]current_state,next_state; always@(posedge clk or negedge rst_n) begin if(!rst_n) current_state<=IDLE; else current_state<=next_state; end always@(*) begin if(!rst_n) next_state=IDLE; else begin case(current_state) IDLE:if(seq_in==2'b10) next_state=S1; else next_state=IDLE; S1:if(seq_in==2'b11) next_state=S2; else next_state=S1; S2:if(seq_in==2'b00) next_state=S3; else next_state=S2; S3:if(seq_in==2'b11||seq_in==2'b10) next_state=S4; else next_state=S3; S4:if(seq_in==2'b10) next_state=S1; else next_state=IDLE; default:next_state=IDLE; endcase end end always@(posedge clk or negedge rst_n) begin if(!rst_n) flag<=1'b0; else if(current_state==S4) flag<=1'b1; else flag<=1'b0; end endmodule

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Engineer: connor jiao // Create Date: // Design Name: // Module Name: // Function : // Revision 0.01 - File Created // Additional Comments: ////////////////////////////////////////////////////////////////////////////////// module sequence_check_2bit_tb(); reg clk; reg rst_n; reg [1:0]seq_in; wire flag; sequence_check_2bit sequence_check_2bit( .clk(clk), .rst_n(rst_n), .seq_in(seq_in), .flag(flag) ); initial clk=0; always #10 clk=~clk; initial begin rst_n=0; #201; rst_n=1; seq_in=00; #20 seq_in=10; #20 seq_in=11; #20 seq_in=00; #20 seq_in=10; #20 seq_in=10; #20 seq_in=10; #20 seq_in=10; #20 seq_in=10; #20 seq_in=10; #20 seq_in=11; #20 seq_in=00; #20 seq_in=11; #20 seq_in=10; #20 seq_in=10; #20 seq_in=10; #20 seq_in=10; #200; $stop; end endmodule

YKJIAO