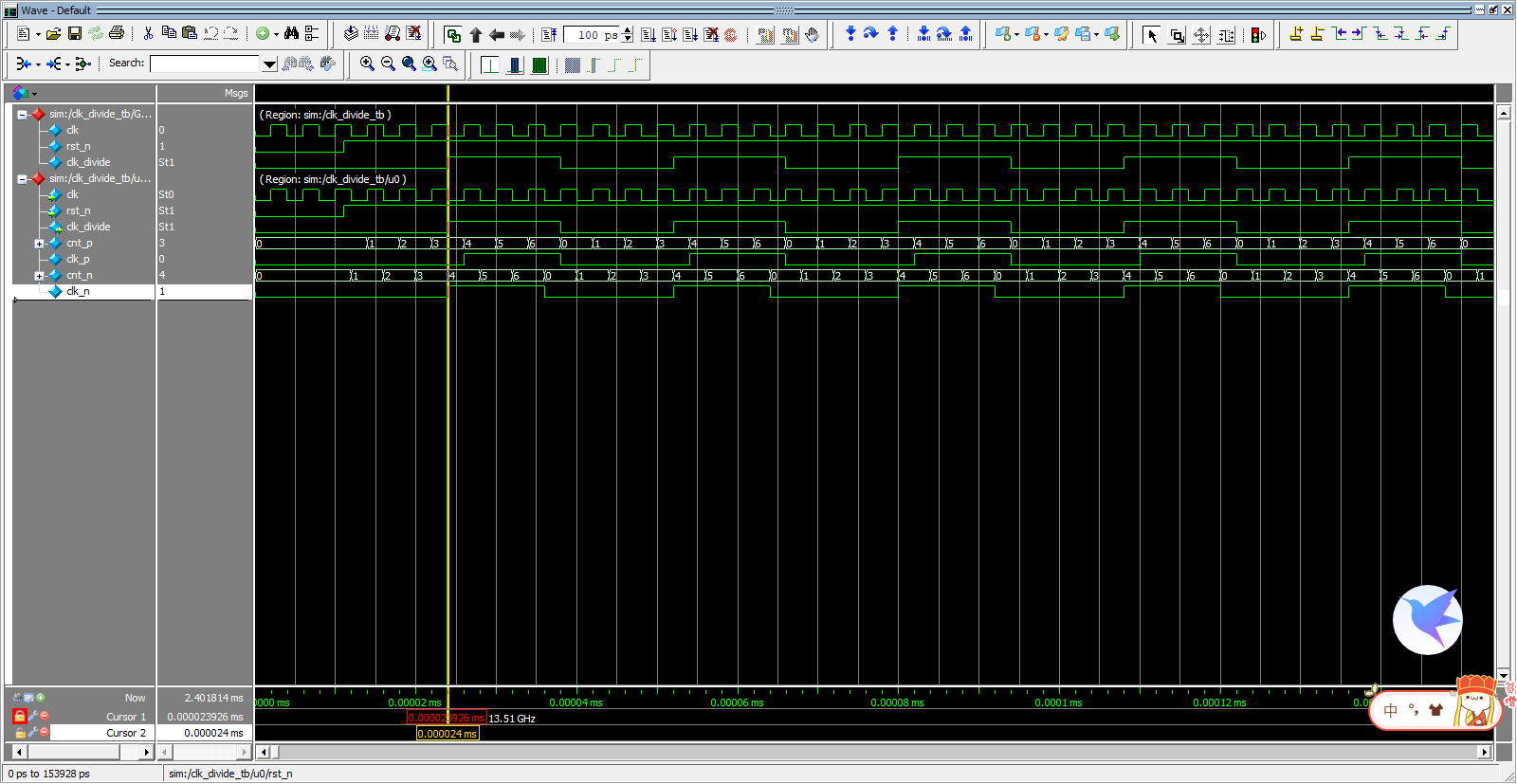

七分频

module Freq_divide ( input clk, input rst_n, output clk_divide ); //----------count the posedge--------------------- reg [2:0] cnt_p; reg clk_p; always @ (posedge clk or negedge rst_n) if(!rst_n) cnt_p <= 3'd0; else if(cnt_p == 3'd6) cnt_p <= 3'd0; else cnt_p <= cnt_p + 1'b1; always @ (posedge clk or negedge rst_n) if(!rst_n) clk_p <= 1'b0; else if((cnt_p == 3'd3) || (cnt_p == 3'd6)) clk_p <= ~ clk_p; //--------------------------------------------- //----------count the negedge------------------ reg [2:0] cnt_n; reg clk_n; always @ (negedge clk or negedge rst_n) if(!rst_n) cnt_n <= 3'd0; else if(cnt_n == 3'd6) cnt_n <= 3'd0; else cnt_n <= cnt_n + 1'b1; always @ (negedge clk or negedge rst_n) if(!rst_n) clk_n <= 1'b0; else if((cnt_n == 3'd3) || (cnt_n == 3'd6)) clk_n <= ~clk_n; //---------------------------------------------- assign clk_divide = clk_p | clk_n; endmodule

3:4变成3.5:3.5

YKJIAO

浙公网安备 33010602011771号

浙公网安备 33010602011771号