[原创]时钟分频之奇分频(5分频)

0. 简介

有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录。

1. 奇分频

其实现很简单,主要为使用两个计数模块分别计数,得到两个波形进行基本与或操作完成。直接贴出代码部分如下。

1 module div_freq( 2 iCLK, 3 iRST_n, 4 oCLK 5 ); 6 7 input wire iCLK; 8 input wire iRST_n; 9 output oCLK; 10 11 parameter N = 4'd5; 12 13 reg clk_p; 14 reg [3:0] cnt_p; 15 always @ (posedge iCLK or negedge iRST_n) begin 16 if (!iRST_n) 17 cnt_p <= 4'd0; 18 else if (cnt_p == N - 1) 19 cnt_p <= 4'd0; 20 else 21 cnt_p <= cnt_p + 1'b1; 22 end 23 always @ (posedge iCLK or negedge iRST_n) begin 24 if (!iRST_n) 25 clk_p <= 1'b0; 26 else if (cnt_p == (N - 1) / 2) 27 clk_p <= ~clk_p; 28 else if (cnt_p == N - 1) 29 clk_p <= ~clk_p; 30 else 31 clk_p <= clk_p; 32 end 33 34 35 reg clk_n; 36 reg [3:0] cnt_n; 37 always @ (negedge iCLK or negedge iRST_n) begin 38 if (!iRST_n) 39 cnt_n <= 4'd0; 40 else if (cnt_n == N - 1) 41 cnt_n <= 4'd0; 42 else 43 cnt_n <= cnt_n + 1'b1; 44 end 45 always @ (negedge iCLK or negedge iRST_n) begin 46 if (!iRST_n) 47 clk_n <= 1'b0; 48 else if (cnt_n == (N - 1) / 2) 49 clk_n <= ~clk_n; 50 else if (cnt_n == N - 1) 51 clk_n <= ~clk_n; 52 else 53 clk_n <= clk_n; 54 end 55 56 assign oCLK = clk_p | clk_n; 57 58 endmodule 59

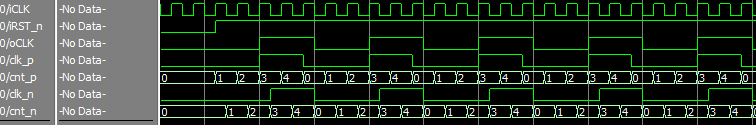

modelsim仿真结果如下图

浙公网安备 33010602011771号

浙公网安备 33010602011771号