汇编五到八章汇总

1.内存单元间接表示: [bx]

mov dl, [0]; dl ← ((ds)×16 + 0)

mov bx, 0

mov dl, [bx]; dl ← ((ds)×16 + (bx))

可以使用bx间接访问内存单元。默认,段地址在ds。

2.loop指令

(1) 语法格式

loop 标号

(2) CPU执行指令过程

① (cx) ← (cx) - 1

② 判断cx的值是否为0。 如果(cx) ≠ 0,跳转到标号处执行; 如果(cx) = 0, 执行loop后面的其它指令。

3.段前缀

mov dl, [6]; dl ← ((ds)×16 + 6)

mov ax, [bx]; ax ← ((ds)×16 + (bx))

默认情形下,无论是直接给出的偏移地址,还是通过bx间接给出的偏移地址,都是取ds的值作为段地址来计算物理地址。 可以通过增加「段前缀」改变默认状况。

一:dw=define word 即使用dw定义字型数据(数据之间以逗号分隔),dw 既可定义数据,也可以说用它开辟内存空间

db定义字节类型变量,一个字节数据占1个字节单元,读完一个,偏移量加1

dw定义字类型变量,一个字数据占2个字节单元,读完一个,偏移量加2

dd定义双字类型变量,一个双字数据占4个字节单元,读完一个,偏移量加4

二:程序取得所需空间的方法有两种,1是在加载程序的时候为程序分配,2是程序在执行的过程中向系统申请。

三:数据和指令在本质上无区别,为了让程序的入口处是我们所希望执行的指令。我们可以加标号。在程序入口前加标号,在程序结束后加上相同的标号。

标号 start 与 end start——end 除了通知编译器程序结束外,还可以通知编译器程序的入口在什么地方,

此处用 end 指令表明了程序的入口在标号 start 处,被转化为一个入口地址

四:将数据、代码、栈放在不同的段中,可以使程序结构清晰易懂,对于8086而言,可以使用多个栈,解决长度超64kb的限制问题

访问段中的数据,通过地址(段地址和偏移地址),段名即代表一个标号,代表段地址。

用伪指令 assume 将 cs、ds、ss 分别和 code、data、stack 段相连之后,CPU 也没并没有将对应的段和段寄存器相连接,因为 assume 只是伪指令

1.汇编指令: and和or

and指令:① and指令语法格式及对操作数要求与add指令同

② 可以实现将操作数指定位设置为0

or指令:① or指令语法格式及对操作数要求与add指令同

② 可以实现将操作数指定位设为1

2.汇编中的字符处理

在汇编源程序中:既可以使用诸如'a'这样的字符写法,也可以使用ASCⅡ码形式的写法。

在debug中: a命令中不支持诸如'a'这样的写法

e命令中支持诸如'a'这样的写法,也支持ASCⅡ码形式的写法

1.汇编指令中操作数的类型

常数位于cpu内部,指令缓冲器;寄存器位于cpu内部,寄存器;内存单元位于cpu外部,内存

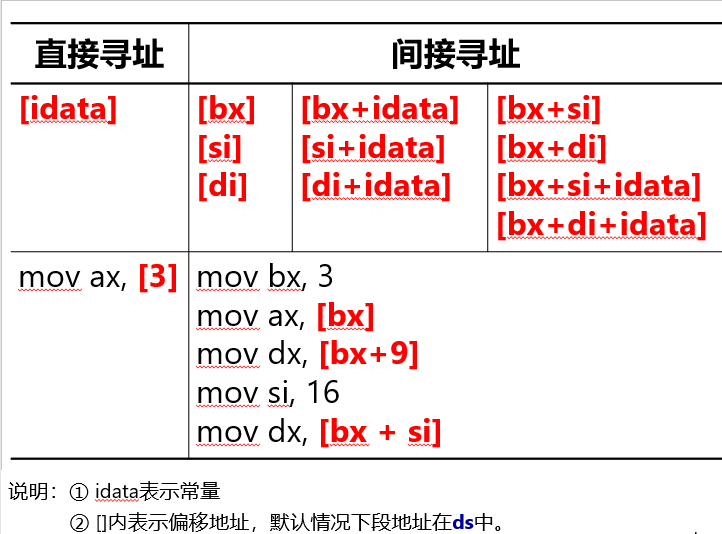

2.汇编指令中内存单元操作数的地址表示

在8086中,可用于表示内存偏移地址的寄存器只有: BX, SI, DI和BP。

这些寄存器可以单个出现在[]中,也可以以特定组合方式出现。

使用BX, SI, DI表示偏移地址时,默认段地址在DS中;

使用BP表示偏移地址时,默认段地址在SS中。

3.汇编伪指令: db, dw, dd, dup

data segment

db 1,2,3; 每个数据分配1个字节

dw 1,2 3; 每个数据分配2个字节

dd 1,2,3; 每个数据分配4个字节

data ends

data segment

db 0,0,0,0,0,0,0,0

db 8 dup(0); 预留8个字节单元,每个单元值为0

dd 8 dup(?); 预留8个字节单元,每个单元值未分配

data ends

div指令

div是除法指令,使用div作除法的时候:

除数:8位或16位,在寄存器或内存单元中

被除数:(默认)放在AX 或 DX和AX中

结果:运算 8位 16位

商 AL AX

余数 AH DX

div指令格式:

div reg

div 内存单元

dup是一个操作符,在汇编语言中同db、dw、dd 等一样,

也是由编译器识别处理的符号。

它是和db、dw、dd 等数据定义伪指令配合使用的,用来进行数据的重复

浙公网安备 33010602011771号

浙公网安备 33010602011771号