用SignalTap进行硬件仿真

写在前面:本博客为本人原创,严禁任何形式的转载!本博客只允许放在博客园(.cnblogs.com),如果您在其他网站看到这篇博文,请通过下面这个唯一的合法链接转到原文!

本博客全网唯一合法URL:http://www.cnblogs.com/acm-icpcer/p/9308649.html

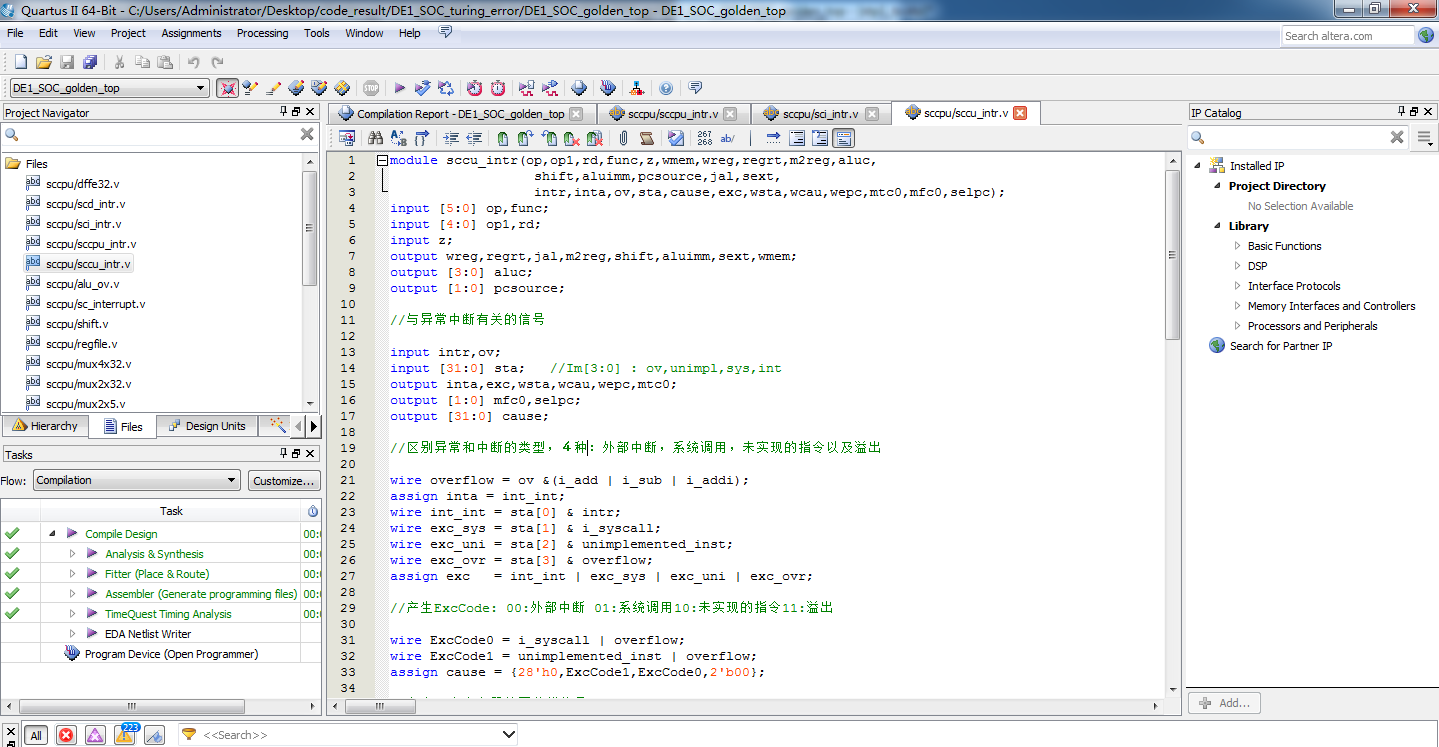

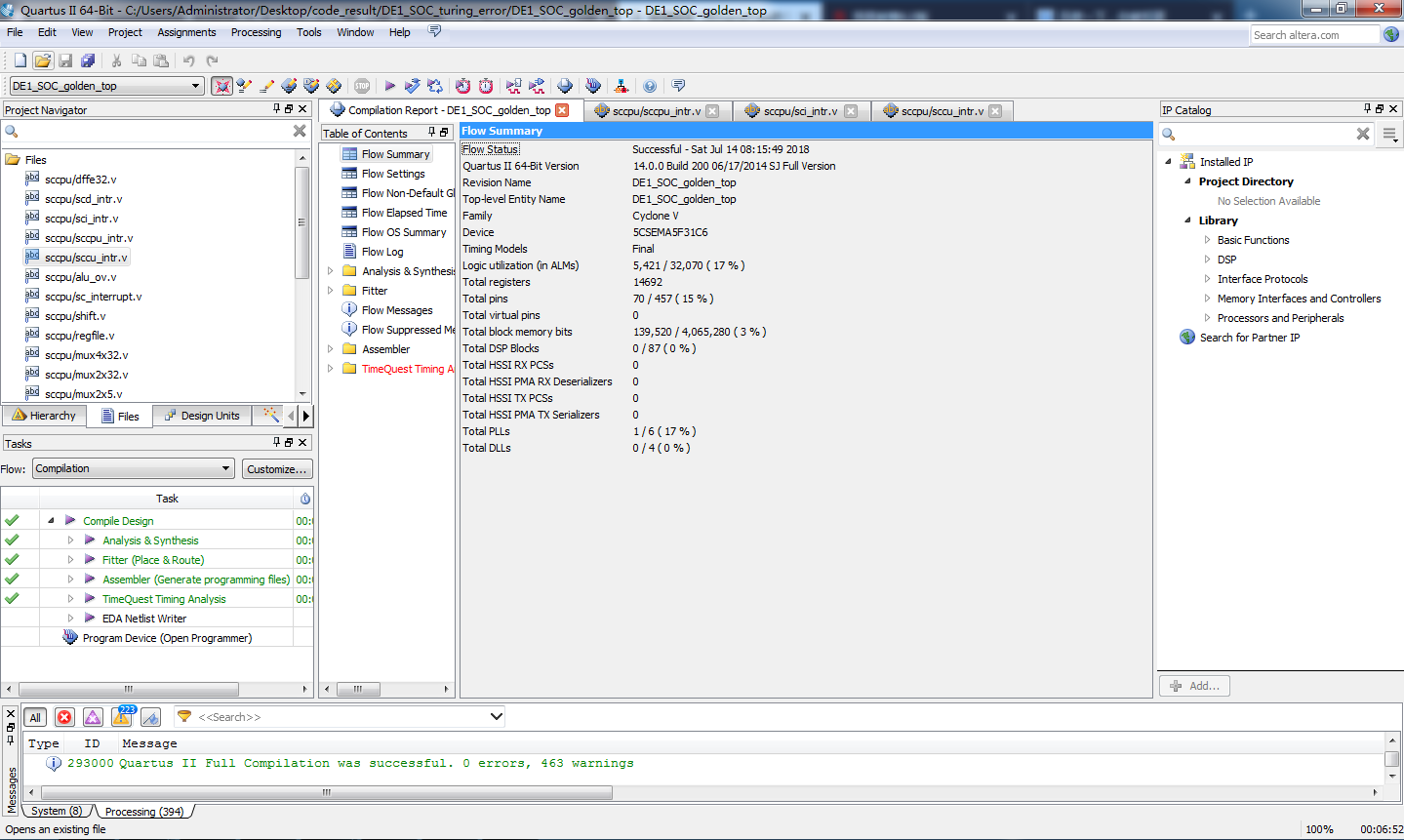

1、完成硬件编程并确保你的工程文件可以正确通过编译。我使用的Verilog HDL进行编程,硬件编程不在本文讨论范围内,可详见Verilog HDL语言实现的单周期CPU设计(全部代码及其注释)。但是我和我的同学曲教授(Prof.Qu)在此代码上进行了很大程度的修改并增加了功能,使该CPU可以应对如内部数据溢出、外部事件中断、执行了未定义的指令等异常和中断,本文的硬件仿真也是基于这个新的CPU,读者应该具备基础的关于中断和中断处理的知识。

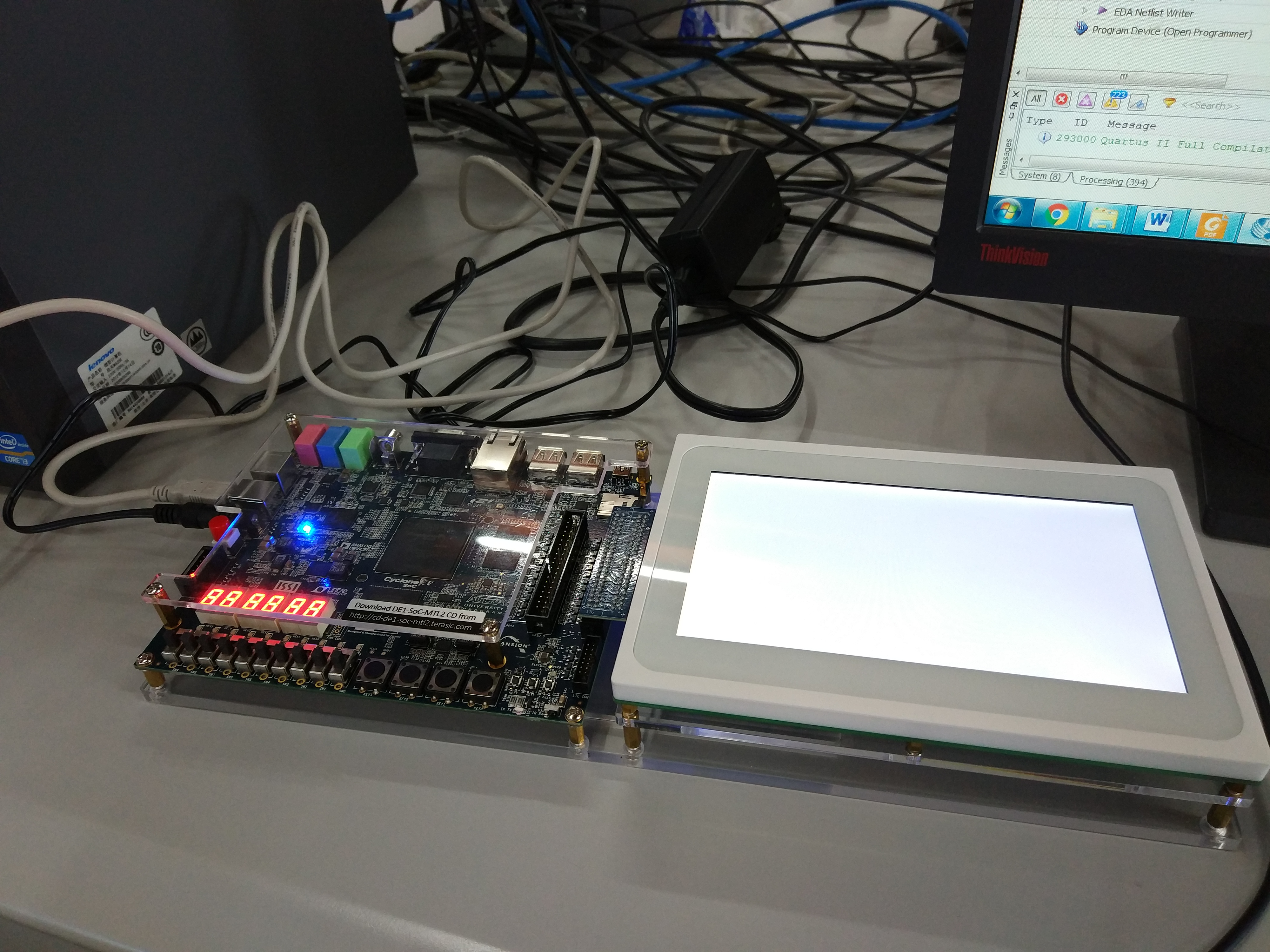

2、将开发板连接到你的计算机,只有连接了开发板才可以在其上进行硬件仿真。

我使用的开发板是Altera公司制造的DE1-SoC开发板(2970RMB的那款,板子功能很强大,跑的是Linux/CentOs操作系统,还可以打麻将。。。):

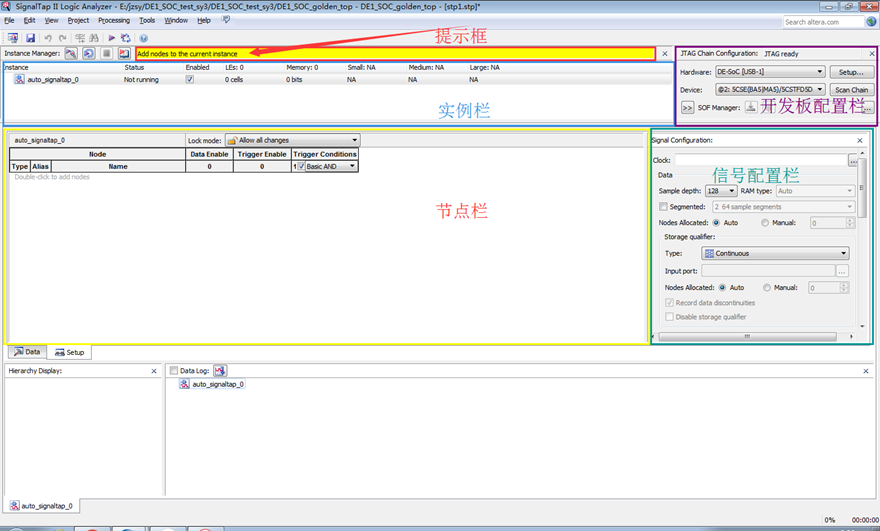

之后可以创建SignalTap硬件仿真文件:

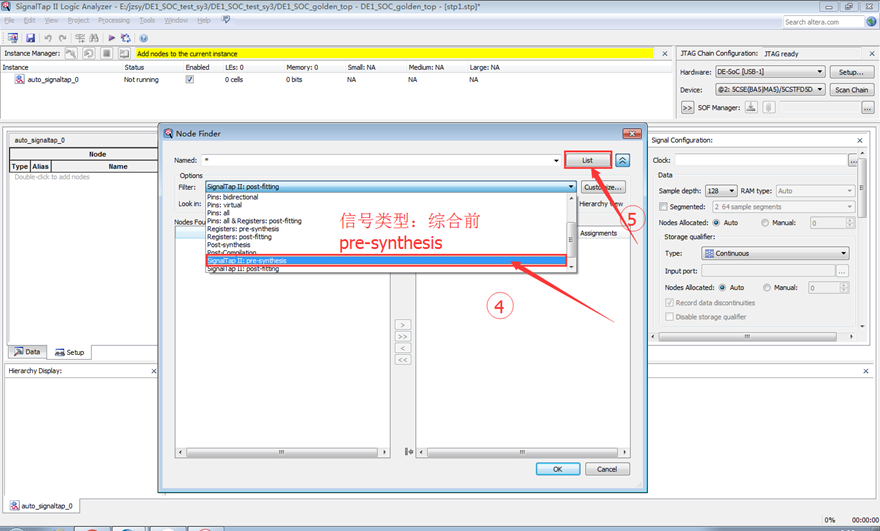

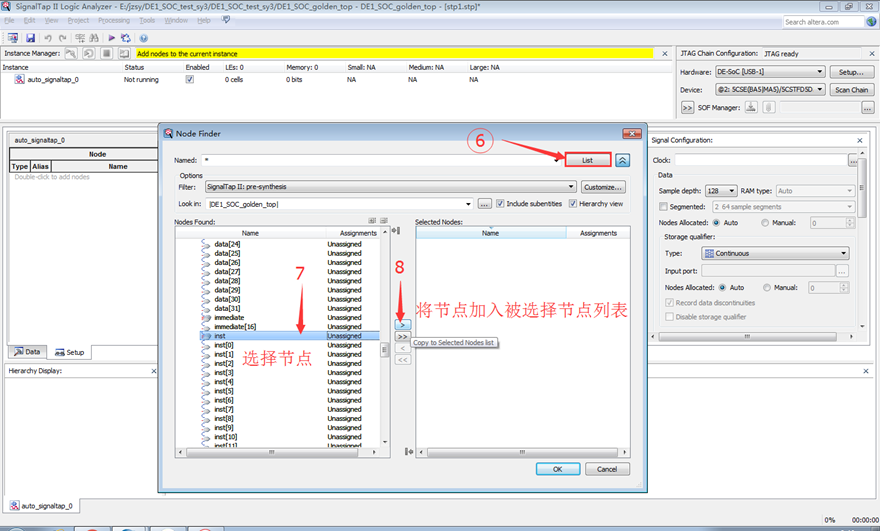

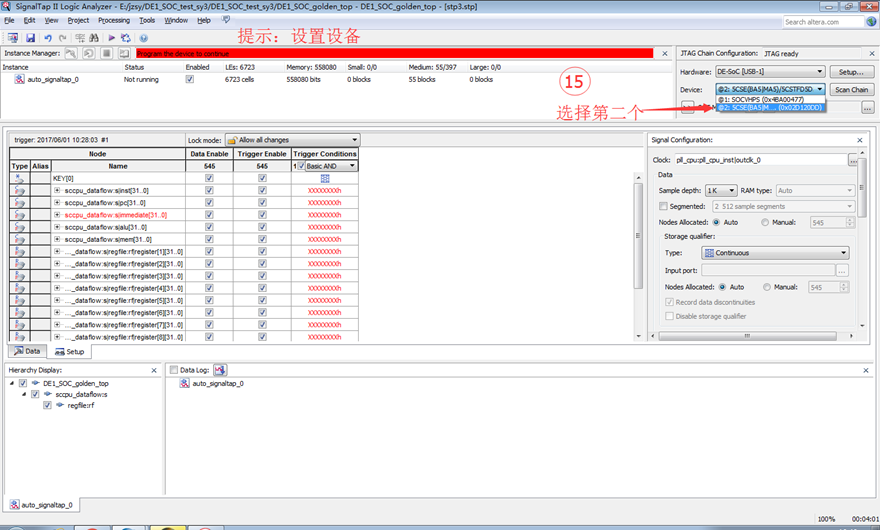

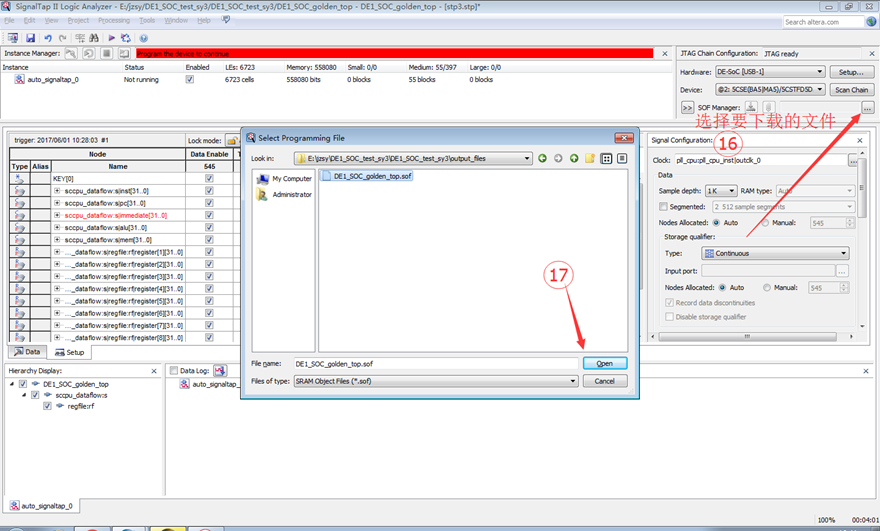

3、完成采样预备设置(即写明你感兴趣的、变化的数据值):

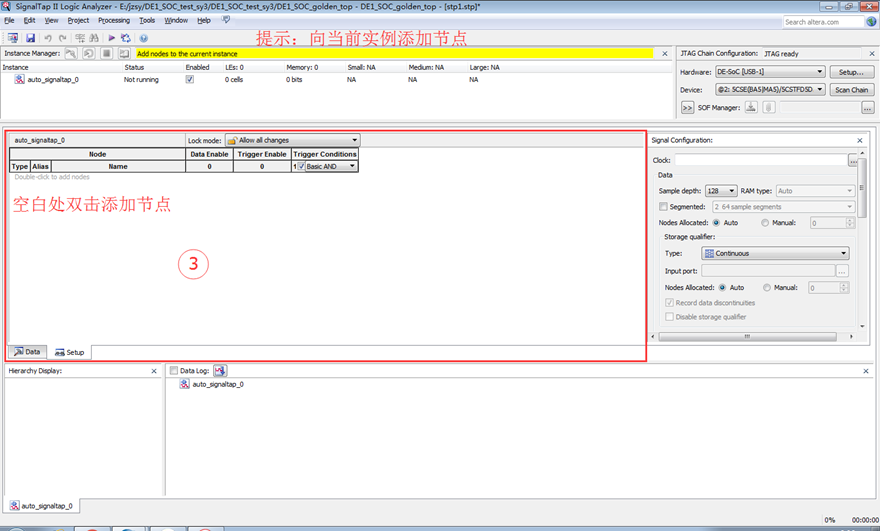

4、反复选择你感兴趣的数据:

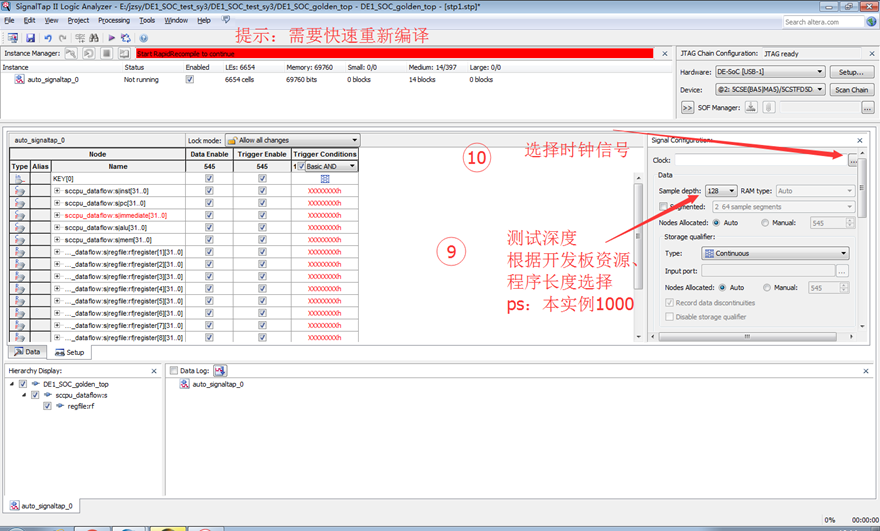

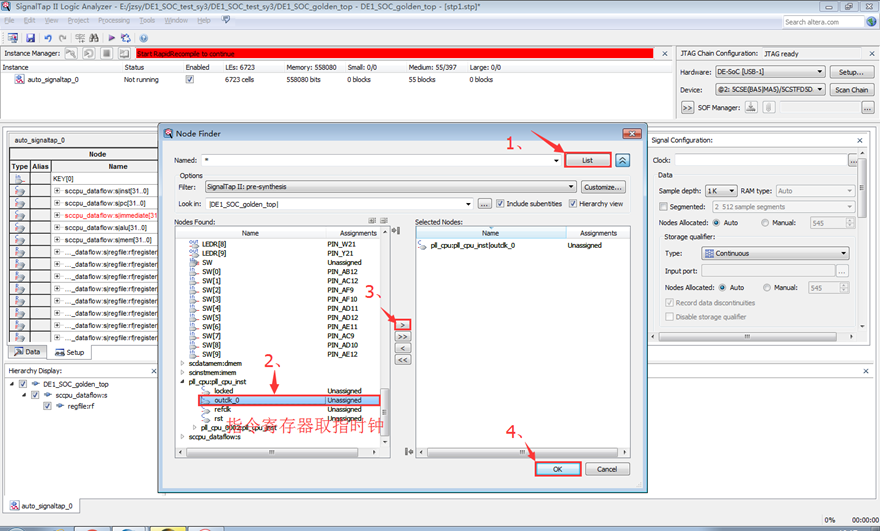

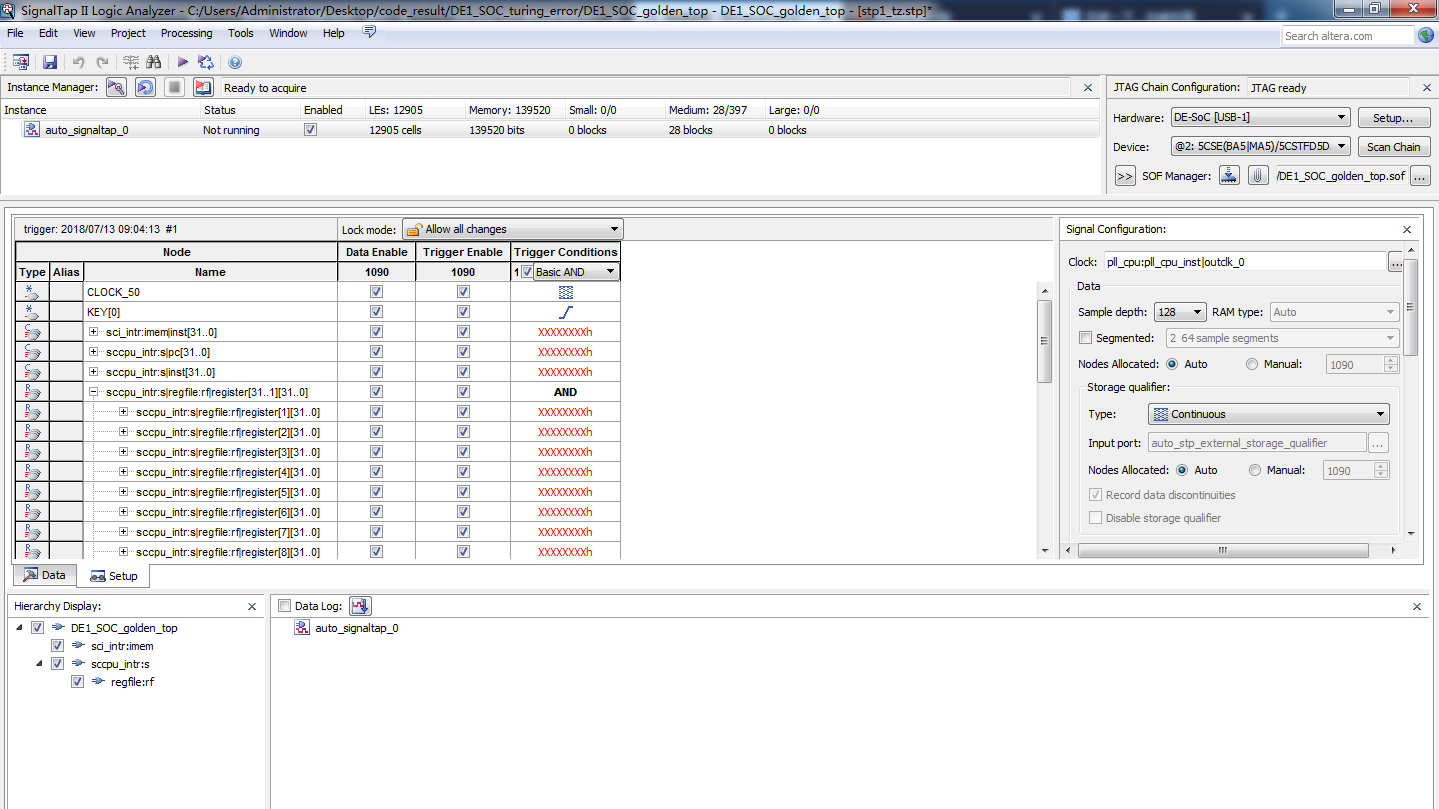

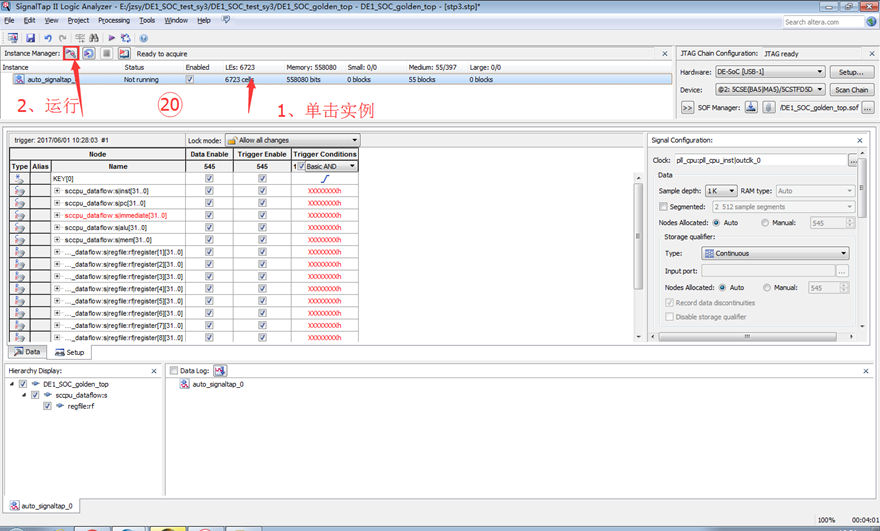

5、完成了所有的设置之后的SingalTap界面差不多就是这样:

然后点击上面的三角形(Start Compilation)进行编译。一般来说你的Verilog HDL代码可以通过编译的话那么你的SignalTap也可以通过编译,我实验室的计算机配置很古董,intel i3+4GB ddr4差不多5分钟完成一次SignalTap的编译:

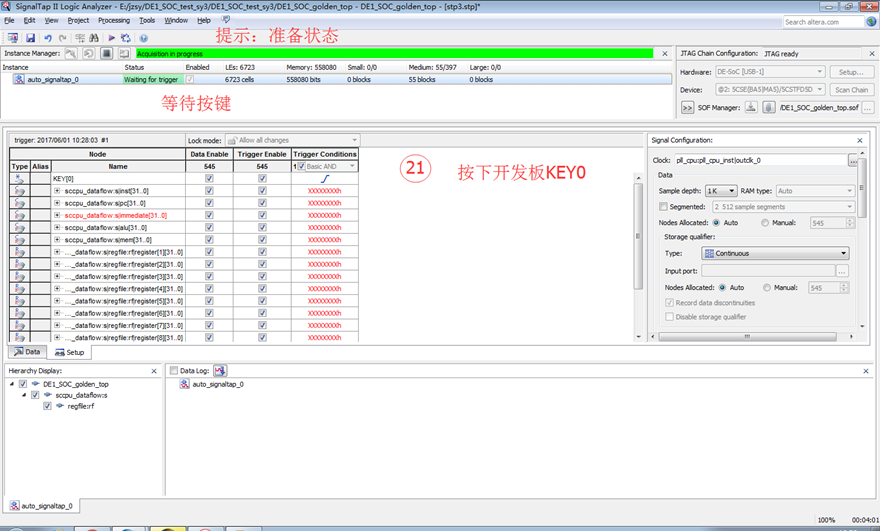

6、SignalTap通过编译之后就可以进行看仿真结果了(特别地,当你需要重新设置SignalTap文件设置或者重新选择仿真信号的时候你需要重新编译SignalTap文件):

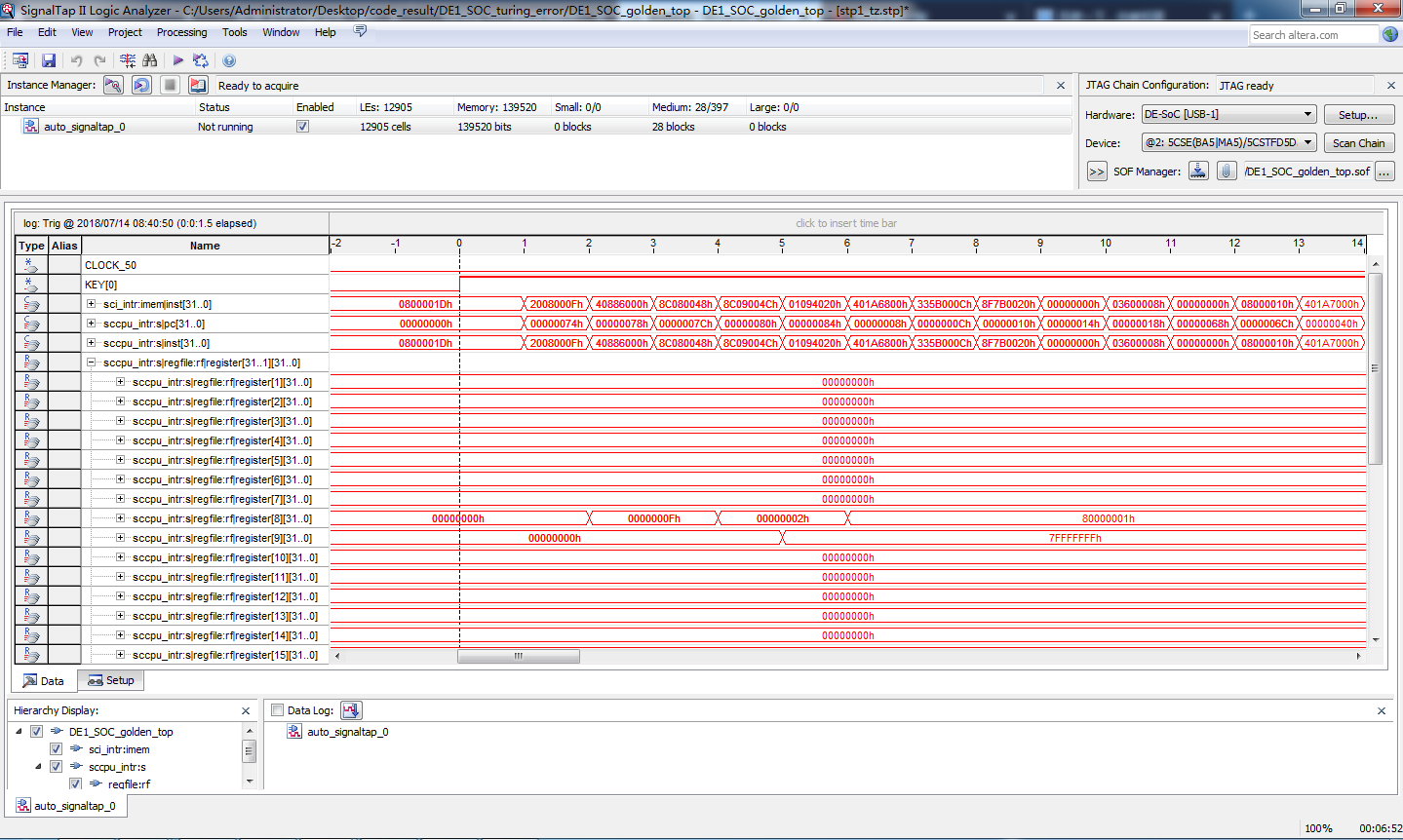

7、观察仿真图进行分析,具体分析技术细节请移步:分析SignalTap的仿真结果

8、附注(打了3天麻将的蔡总):

tz@COI HZAU

2018/7/14

浙公网安备 33010602011771号

浙公网安备 33010602011771号