微电子

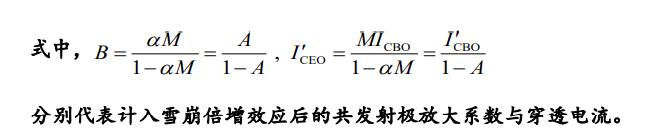

微电子

半导体器件基本方程

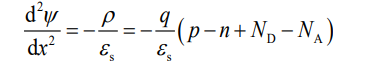

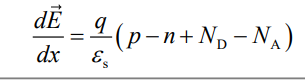

泊松方程

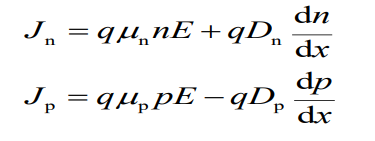

输运方程

又叫电流密度方程

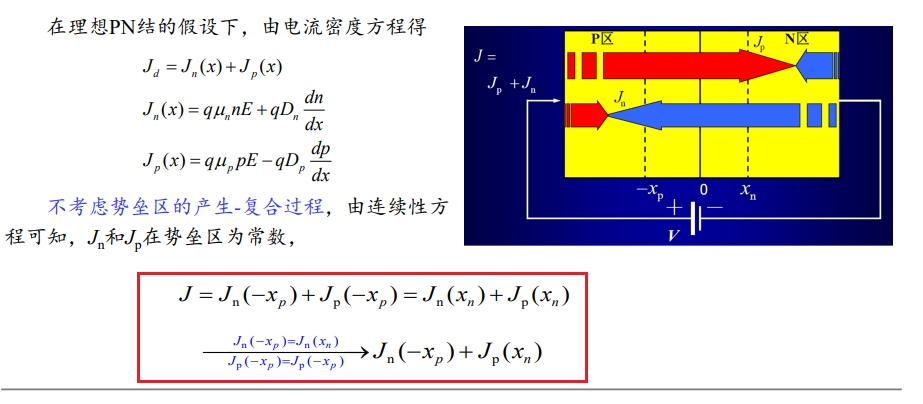

电子电流密度 Jn 和空穴电流密度 Jp 都是由漂移电流密度和扩散电流密度两部分所构成, 即

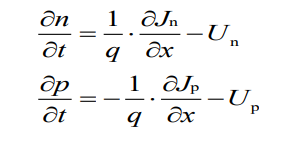

连续性方程

式中,Un 和 Up 分别代表电子和空穴的净复合率。当 U > 0 时表示净复合,当 U < 0 时表示净 产生。

所谓连续性是指载流子浓度在时空上的连续性,即:造成某体积内载流子增加的原因,一定 是载流子对该体积有净流入和载流子在该体积内有净产生。

PN结

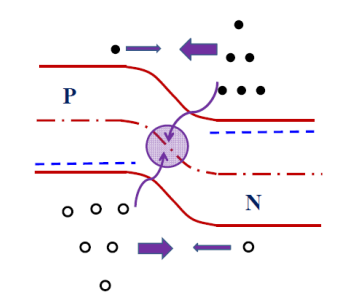

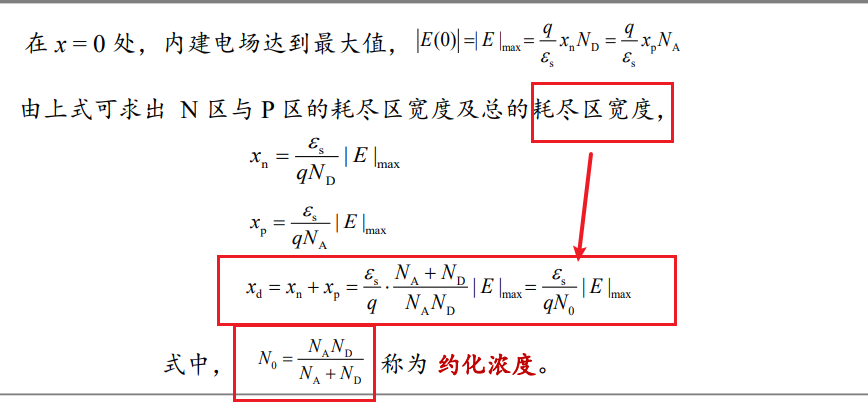

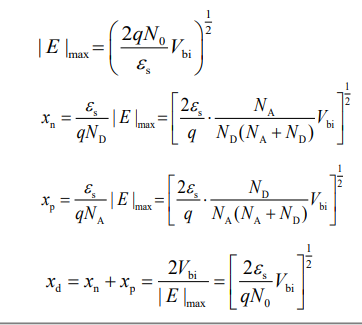

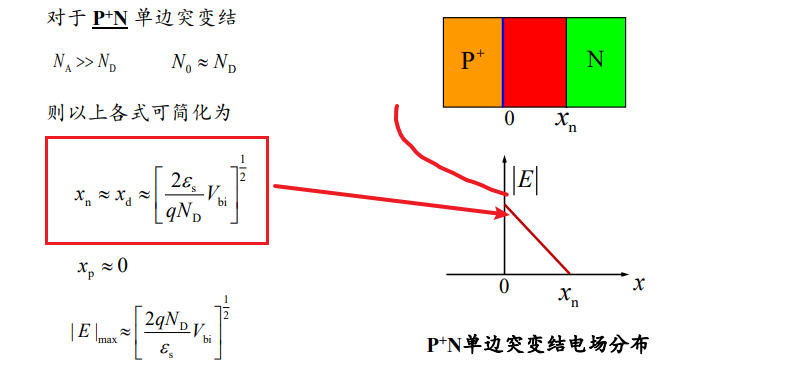

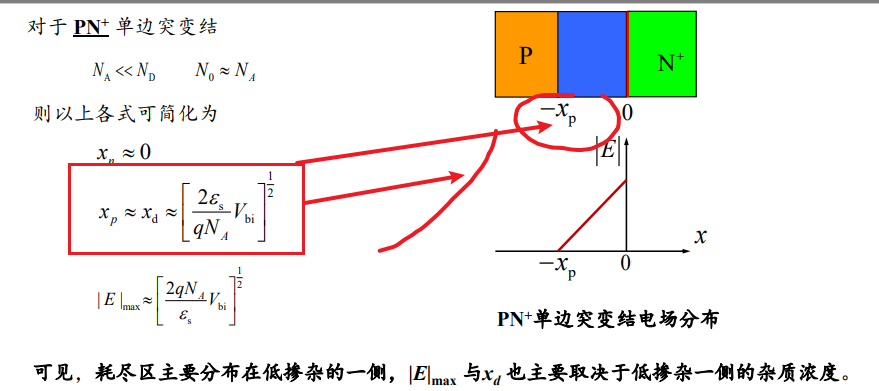

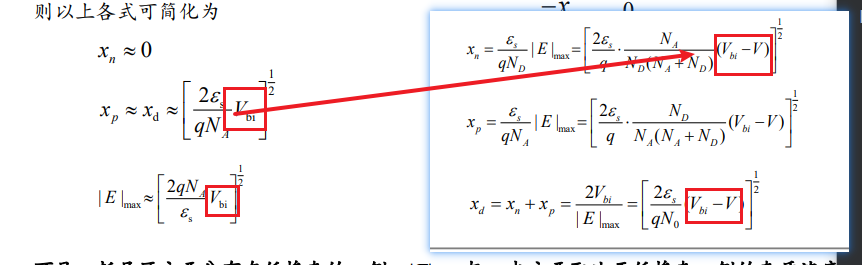

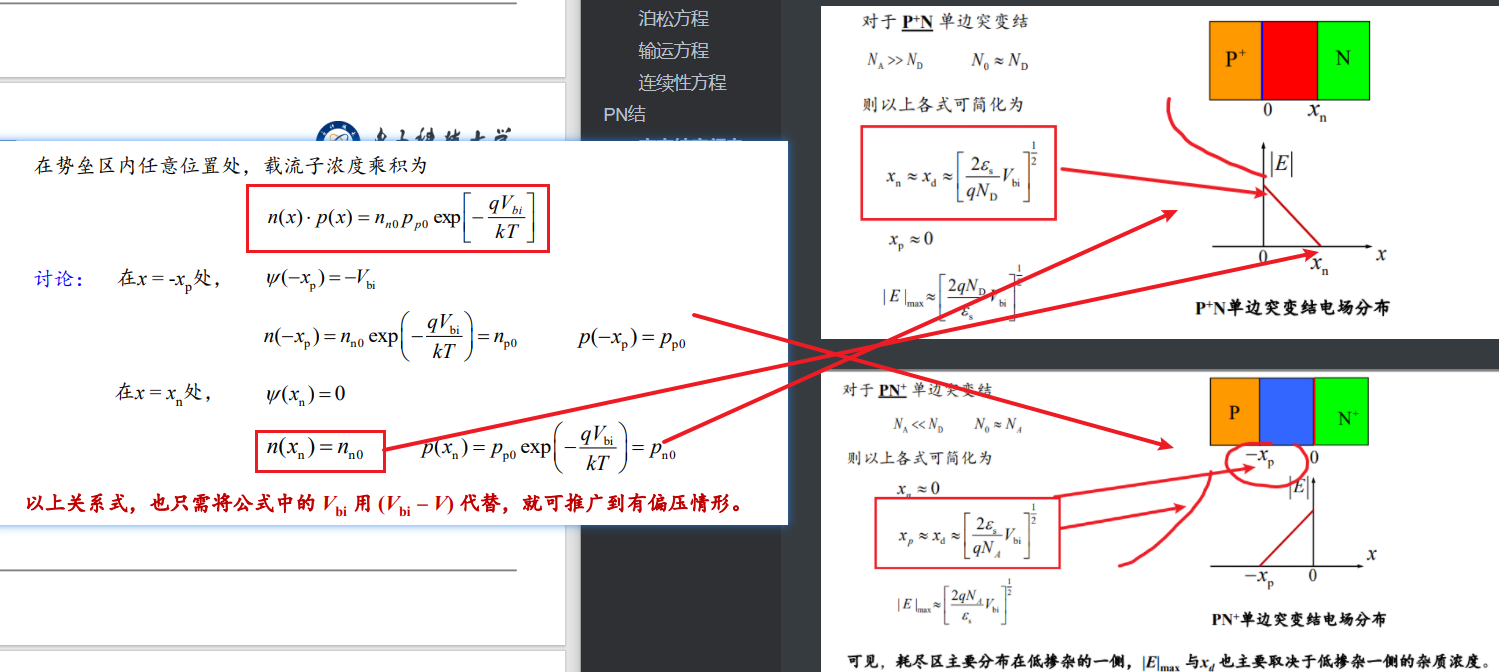

突变结空间电荷区电场分布宽度

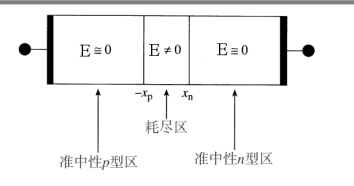

耗尽近似<

空间电荷 完全由电离杂质提供。这时空间电荷区又可称为“耗尽区”。

中性近似

假设耗尽区以外多子浓度等于电离杂质浓度

因而保持电中性。 这时这部分区域又可称为“中性区”

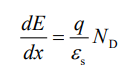

在N区耗尽区,泊松方程

内建电势

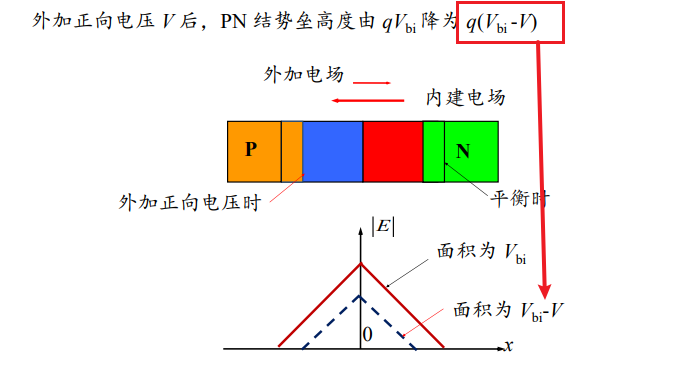

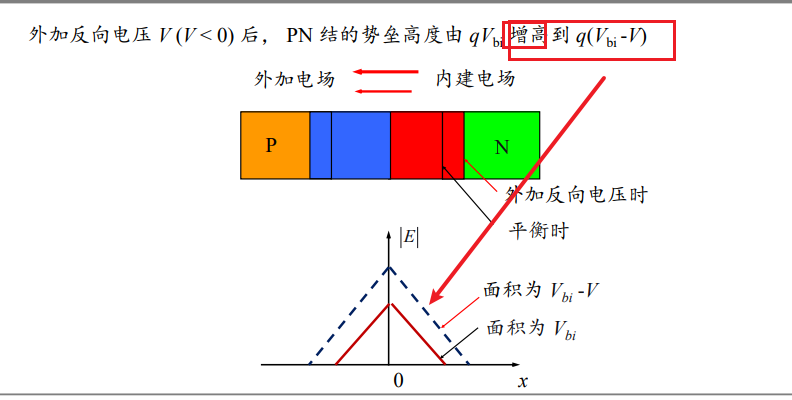

外加电压,假设外加电压全部降落到耗尽区上,则只需要将各个公式的Vbi用 (Vbi-V)代替

- 外加电压参考方向与Vbi相反,V<=Vbi

- 当V接近Vbi,会出现大电流情况,就不能忽略中性区上的压降

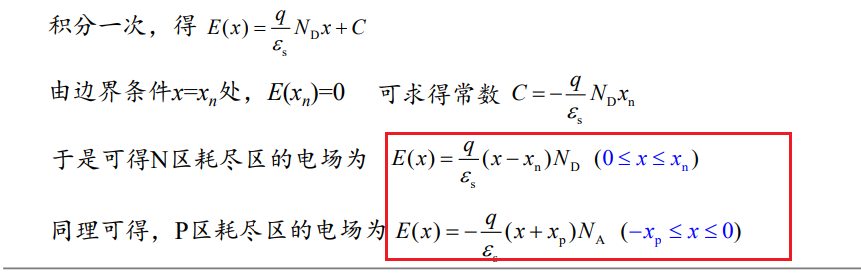

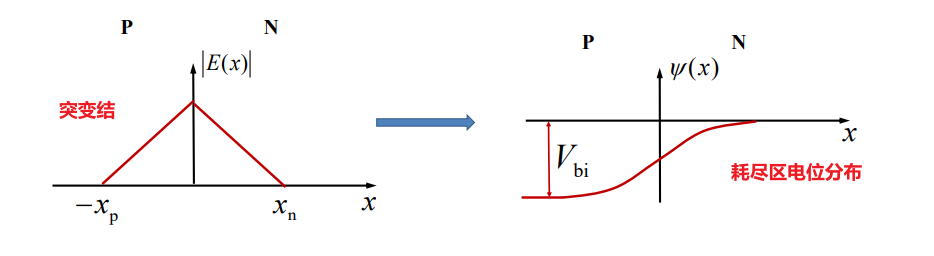

突变结电场分布

以N性中性区作为电位参考点,对E(X)做一次积分就可以求出耗尽区内电位分布

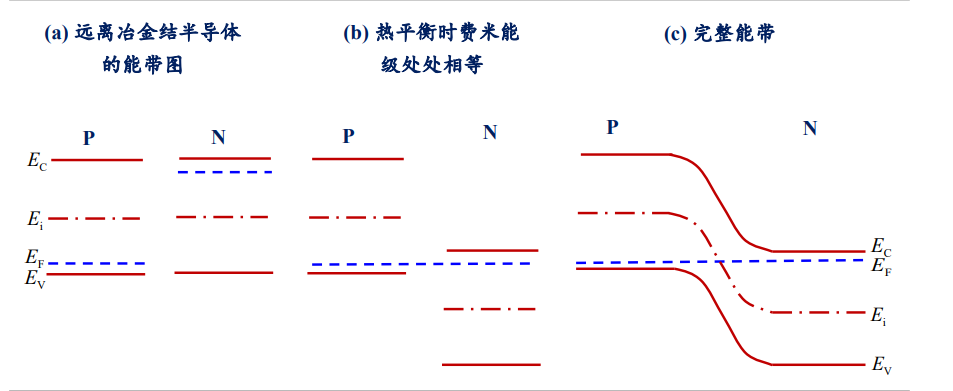

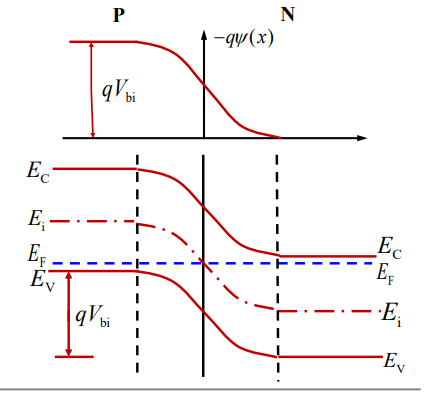

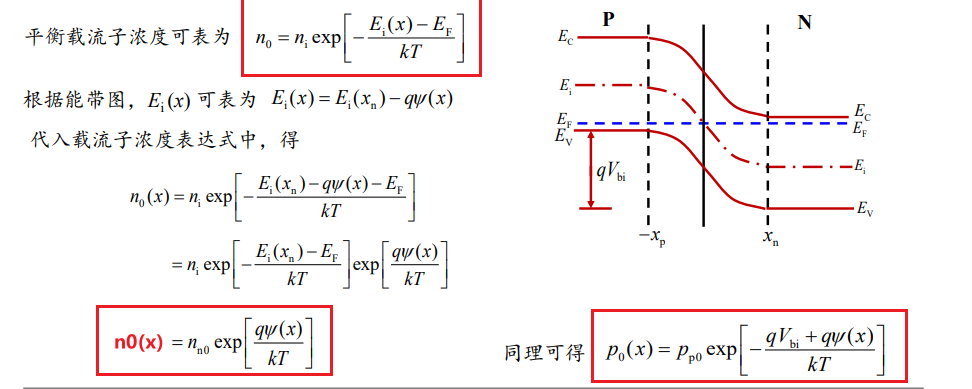

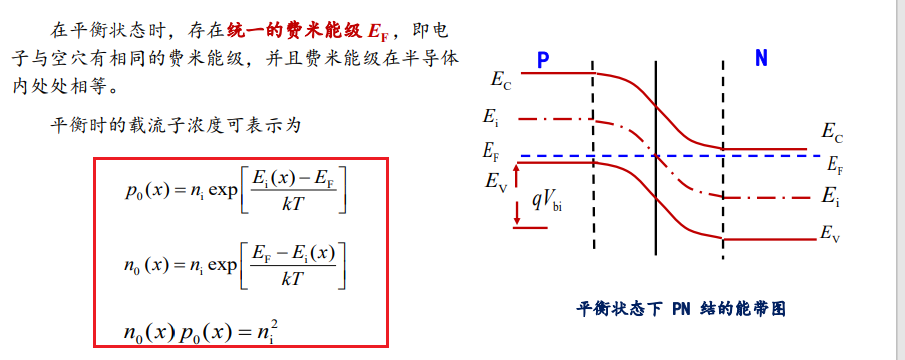

平衡状态下pn结能带图

势垒区:也是耗尽区

空穴从p区到N区也必须克服一个同样高度的势垒 qVbi

平衡pn结空间电荷区载流子分布

理想pn结假定条件

- p区和n区掺杂均匀分布,是突变结

- 电中性区宽度远大于少子扩散长度

- 冶金结为面积足够大的平面,不考虑边缘效应,载流子在pn结中一维流动

- 空间电荷宽度远小于少子扩散长度,不考虑空间电荷区产生复合作用

- p型区和n型区电阻率都足够低,外加电压全部降落在空间电荷区

- 对外加电压限制条件是,正偏工作在小注入范围,反偏电压远低于击穿电压,可以不考虑电流倍增效应

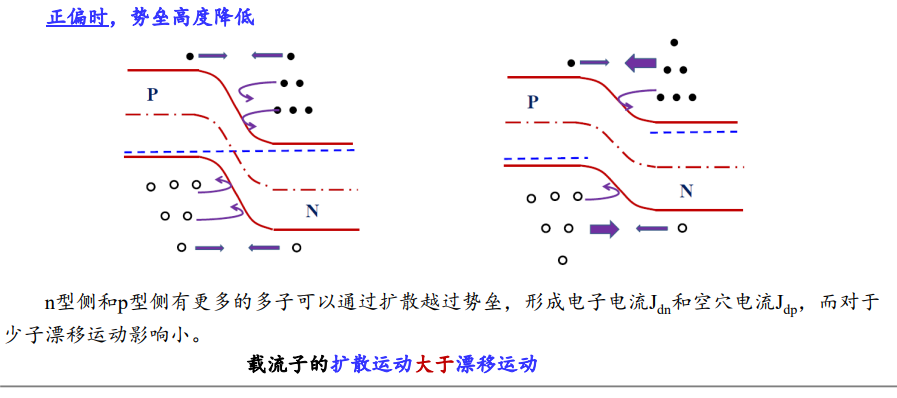

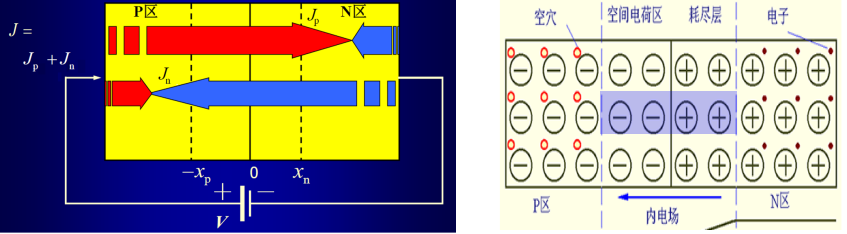

外加偏压是0,多子扩散运动与少子漂移运动达到动态平衡,扩散电流等于漂移电流

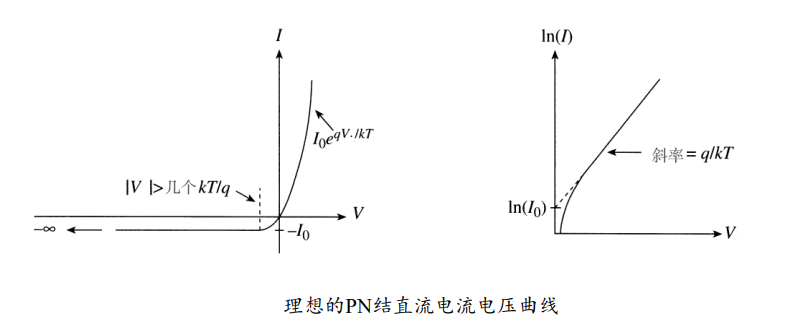

载流子扩散运动大于漂移运动

势垒随外加电压而线性下降,而载流子浓度会随能级位置指数变化

具有足够能量越过势垒电子数目会随电压指数增加,正向电流随外加电压指数关系增大

由于正向电流来源是N区电子和P区空穴,都是多子,正向电流很大

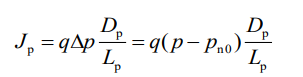

空穴电流密度 JP

电子电流密度 Jn

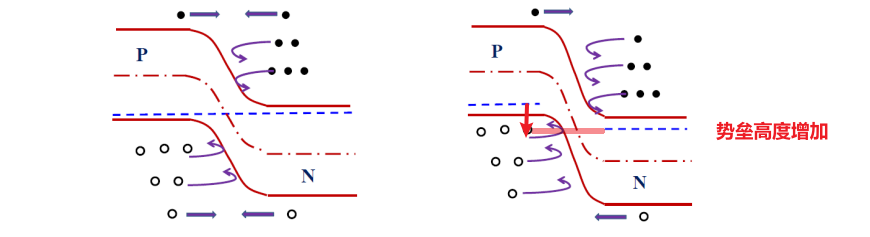

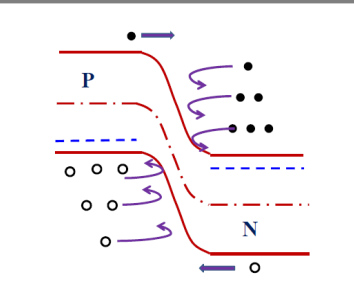

外加反向偏压pn结载流子运动

反偏时势垒高度增加

势垒高度增加,多数载流子扩散运动极大削弱,少子在更强的电场作用下更容易漂移到耗尽层并被扫到结的另一侧,漂移运动加强

载流子扩散运动小于漂移运动

由于反向电流来源是少子,所以反向电流很小且饱和

由于界面附近处的少子有限,所以反向电流会出现饱和

反向电流密度也有两部分组成

空穴电流密度 Jp

电子电流密度 Jn

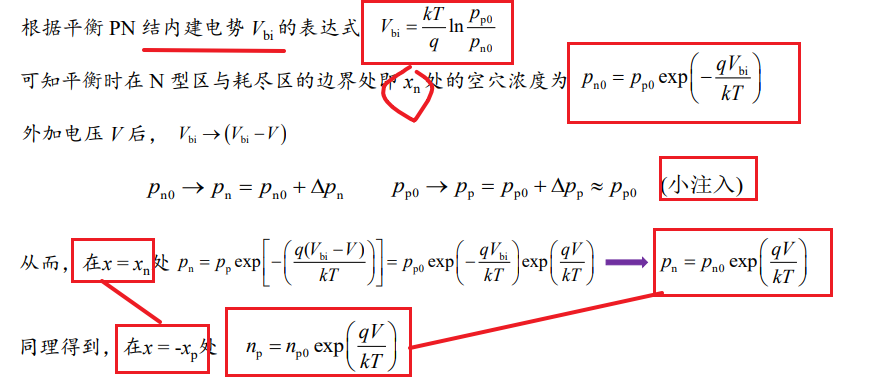

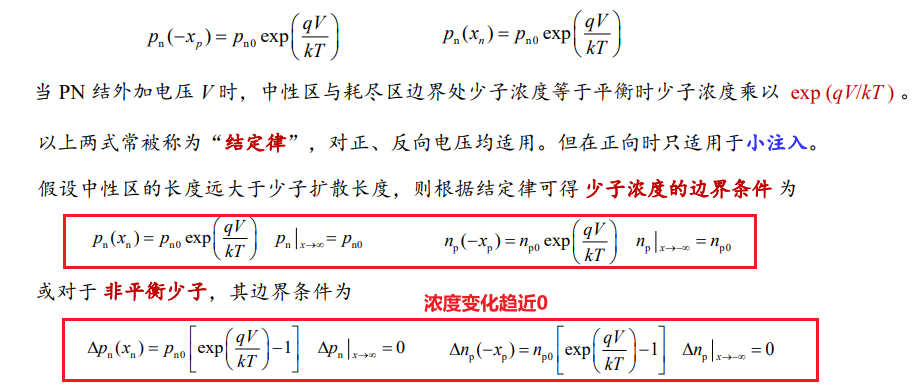

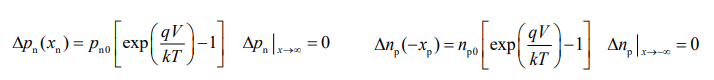

外加偏压下少子浓度分布

结定律

正反电压都能,在正向只适合小注入

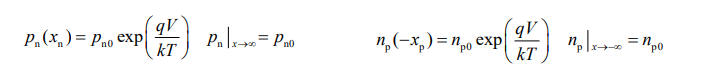

少子浓度边界条件

非平衡少子边界条件

扩散电流

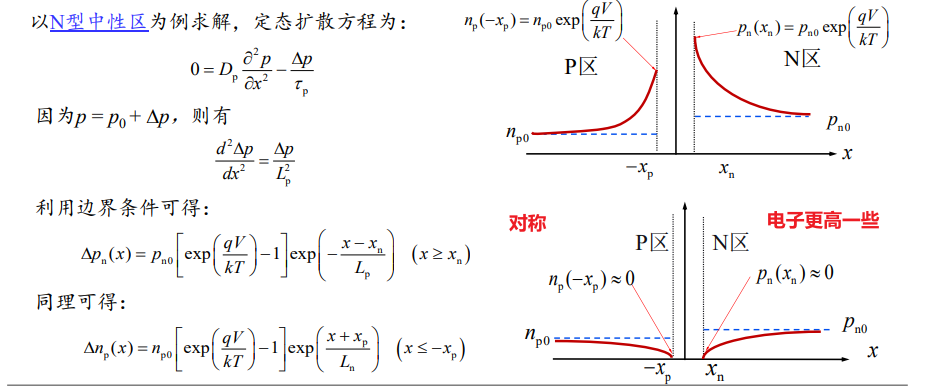

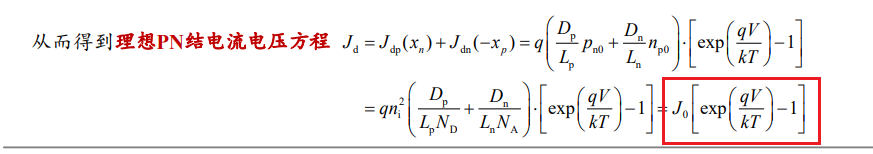

理想pn结电流电压方程是重点

影响反向饱和电流Jo的因素

- 与材料种类有关,EG ↑,则 ni ↓,Jo ↓

- 与掺杂浓度有关 ND 、NA ↑,则 pno 、npo ↓,Jo ↓ ,主要取决于低掺杂一侧的浓度

- 与温度关系 T ↑,则 ni ↑,Jo ↑

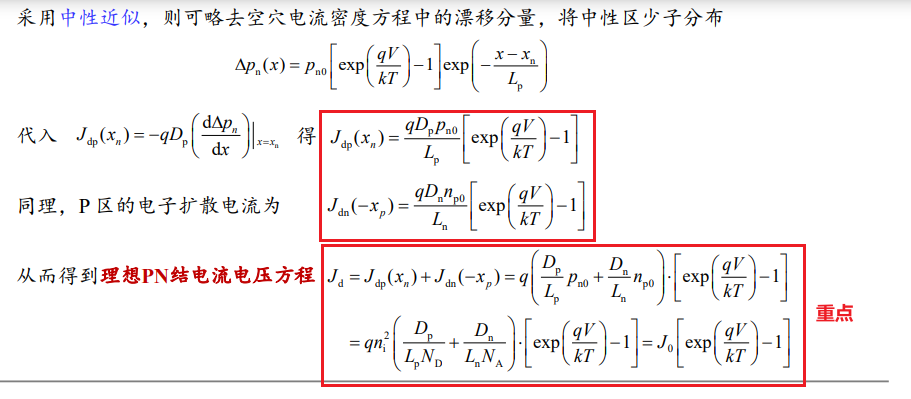

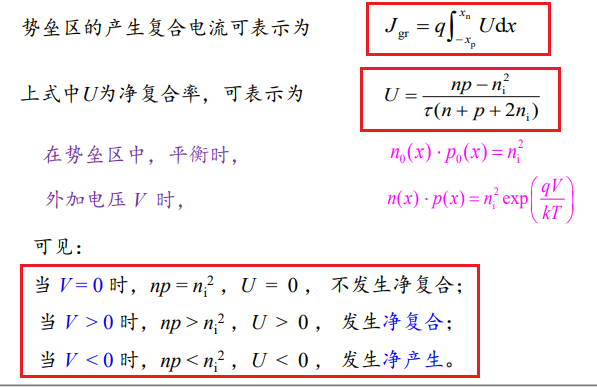

势垒区复合产生电流

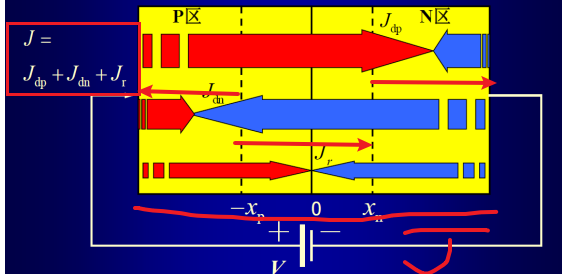

正向偏置

- 增加耗尽层内载流子浓度高于热平衡值

- 耗尽区载流子复合过程占优

- 耗尽区中复合过程使得只有部分多子越过势垒

- 由于载流子通过复合产生中心相互复合而消失的电流叫复合电流

1、空穴扩散电流密度:Jdp

2、电子扩散电流密度:Jdn加此外还有:

3、势垒区复合电流:Jr,

反向偏置

a.耗尽层中载流子浓度将会下降并低于热平衡条件下的值

b.耗尽层内电子空穴对的产生过程占优

c.耗尽层内的产生载流子被电场扫到中性区域

d.被电场扫到中性区域的载流子形成电流,叠加在反向饱和电流上。

反偏PN结的电流密度组成:

1、空穴扩散电流密度:Jdp

2、电子扩散电流密度:Jdn此外还有:

3、势垒区产生电流:Jg

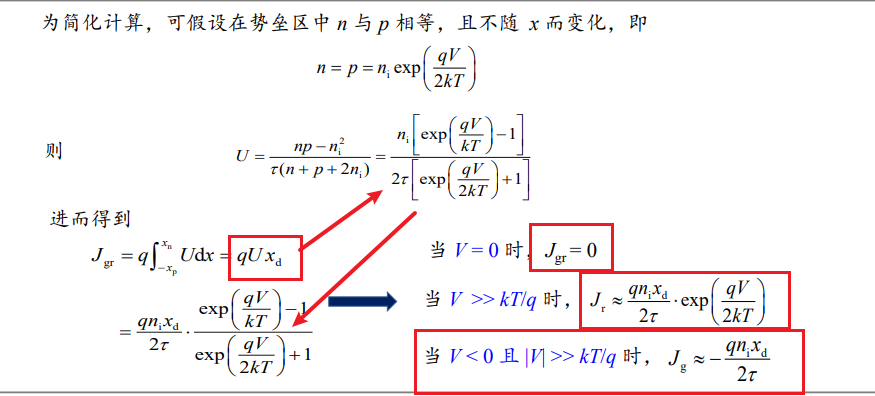

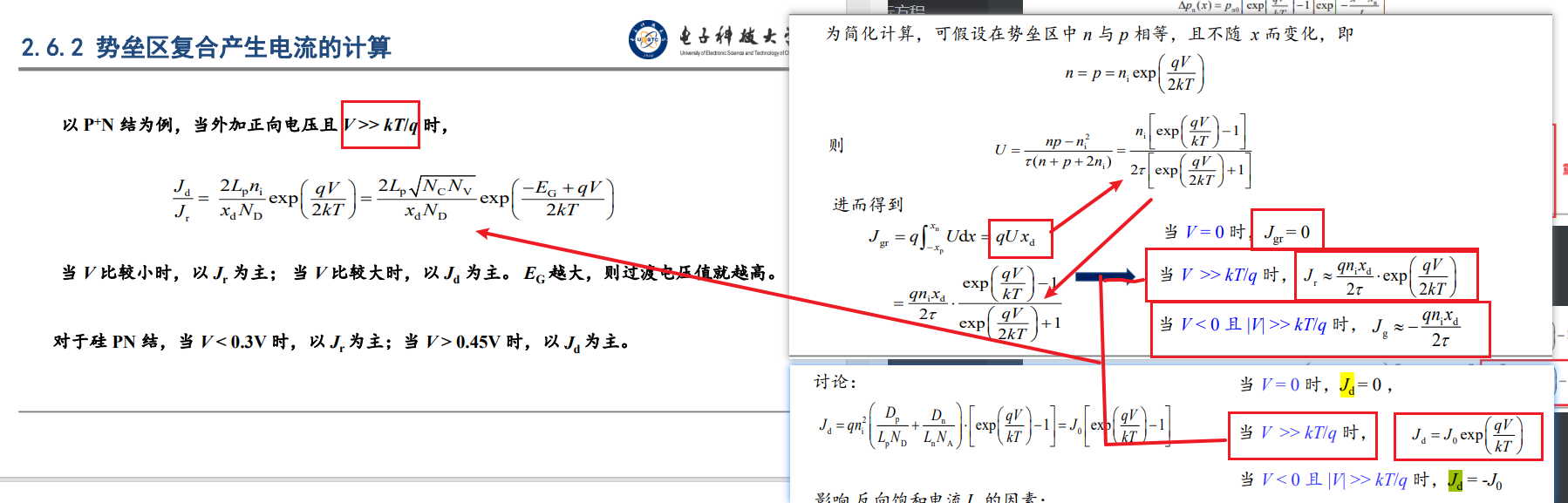

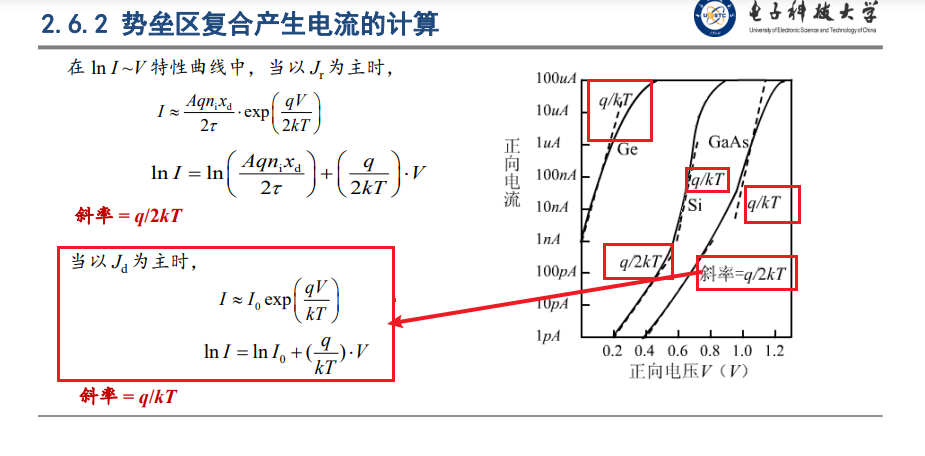

势垒区复合电流计算

当 V 比较小时,以 Jr 为主; 当 V 比较大时,以 Jd 为主。 EG 越大,则过渡电压值就越高。

对于硅 PN 结,当 V < 0.3V 时,以 Jr 为主;当 V > 0.45V 时,以 Jd 为主。

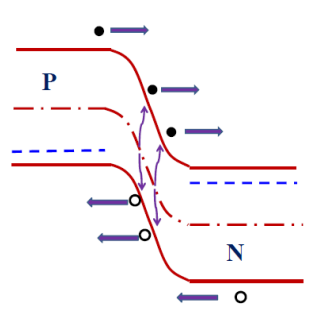

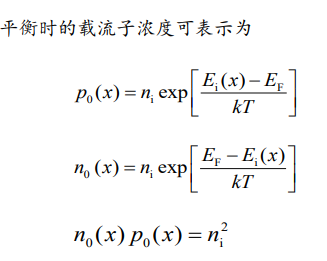

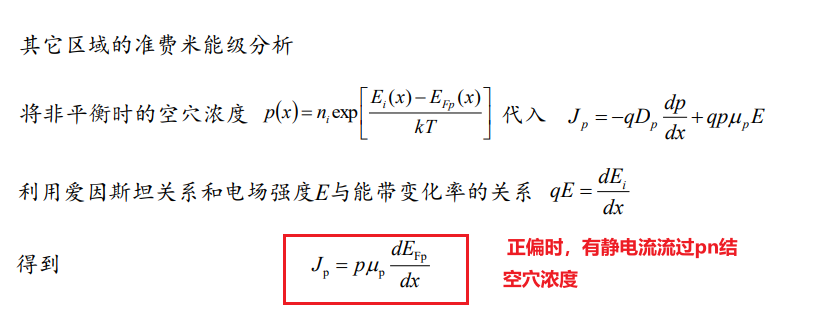

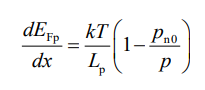

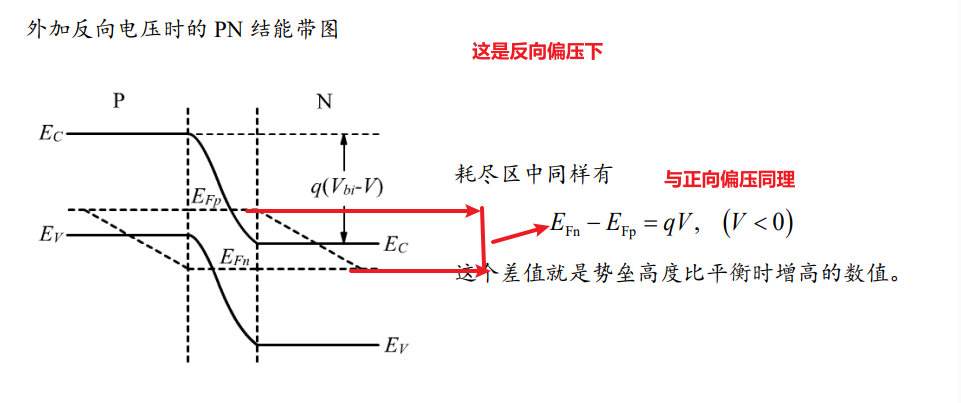

准费米能级

统一费米能级,电子和空穴有相同费米能级EF,费米能级在半导体内处处相等

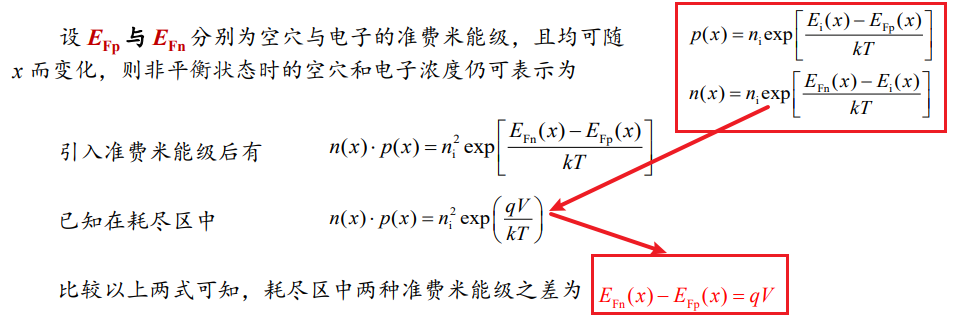

准费米能级

描述平衡状态的公式来描述非平衡状态的载流子浓度分布

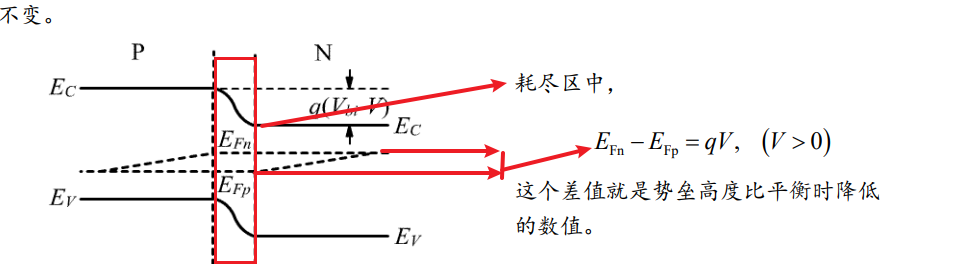

非平衡态PN结能带图

在欧姆接触电极处,存在大量复合中心,使得导带电子与价带空穴有足够相互交换

在p中性区,空穴使多子,由于空穴浓度P=Pp0,所以对一定的Jp,(dEFp /dx)极小。,EFp增加很小近似可以认为EFp(x)在p中性区保持不变。

在N中性区,空穴使少子,EFp(x)在p中性区保持不变。

在N区中离势垒区不远处(扩散区内),p >> pn0 ,每经过一个扩散长度,EFp就增加kT ;随着远离势垒区,当非平衡少子复合完成时,p接近pn0 ,EFp不再随距离变化。

在势垒区内部,空穴浓度比N区大,因此(dEFp/dx)更接近kT/Lp,又因为势垒区宽度小(一般 小于少子扩散长度),因此势垒区内EFp增量比N区内小,近似可以认为EFp准费米能级在势垒区保 持不变。

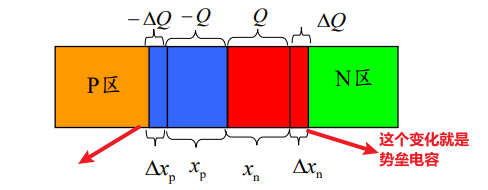

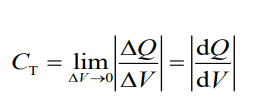

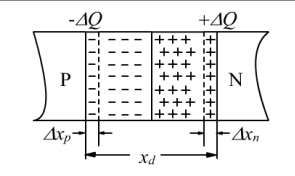

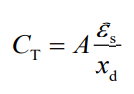

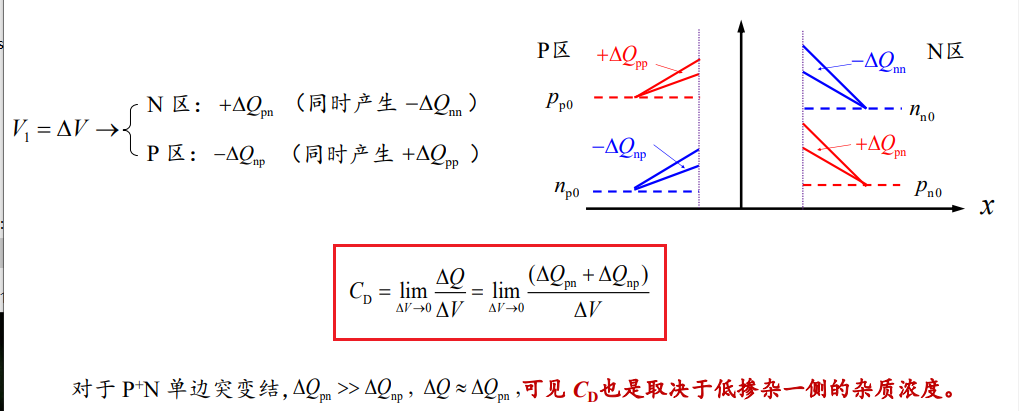

pn结势垒电容

势垒电容定义

当外加电压有(-ΔV)的变化时,势垒区宽度发生变化,使势垒区中的空间电荷也发生相应的ΔQ的变化。

简称势垒电容

简称势垒电容

由于 △xp与 △xn 远小于势垒区总宽度 xd ,所以可将这些变化的电荷看作是集中在势垒区边缘 无限薄层中的面电荷。这时PN 结势垒电容就像一个普通的平行板电容器一样,所以势垒电容 CT 可以简单地表为

有时也将单位面积的势垒电容称为势垒电容。

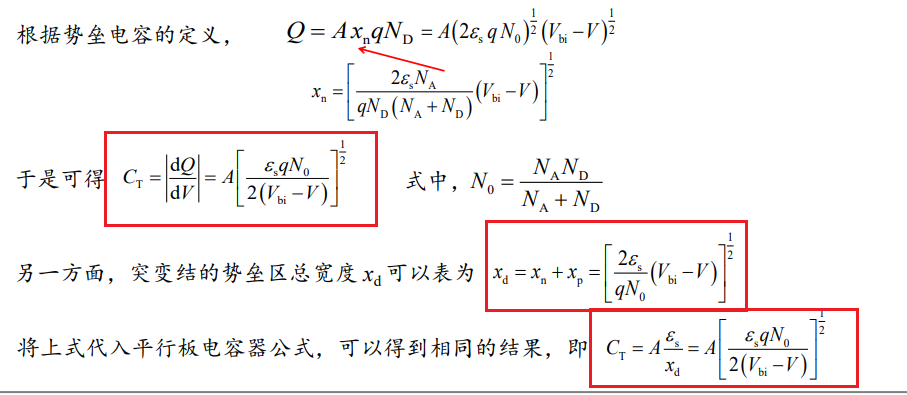

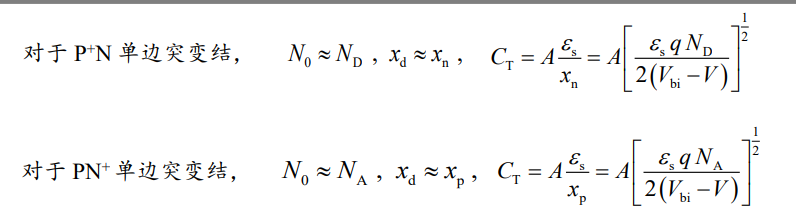

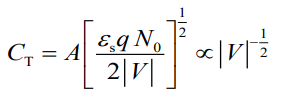

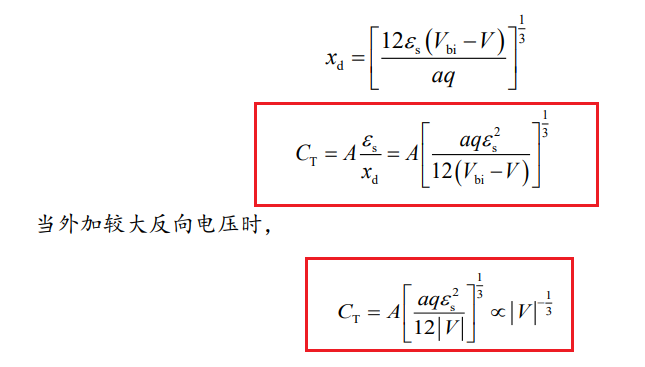

突变结势垒电容

势垒电容取决于低掺杂一侧的杂质浓度

外加较大反向电压时,可以将Vbi略去,

线性缓变结的势垒电容

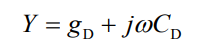

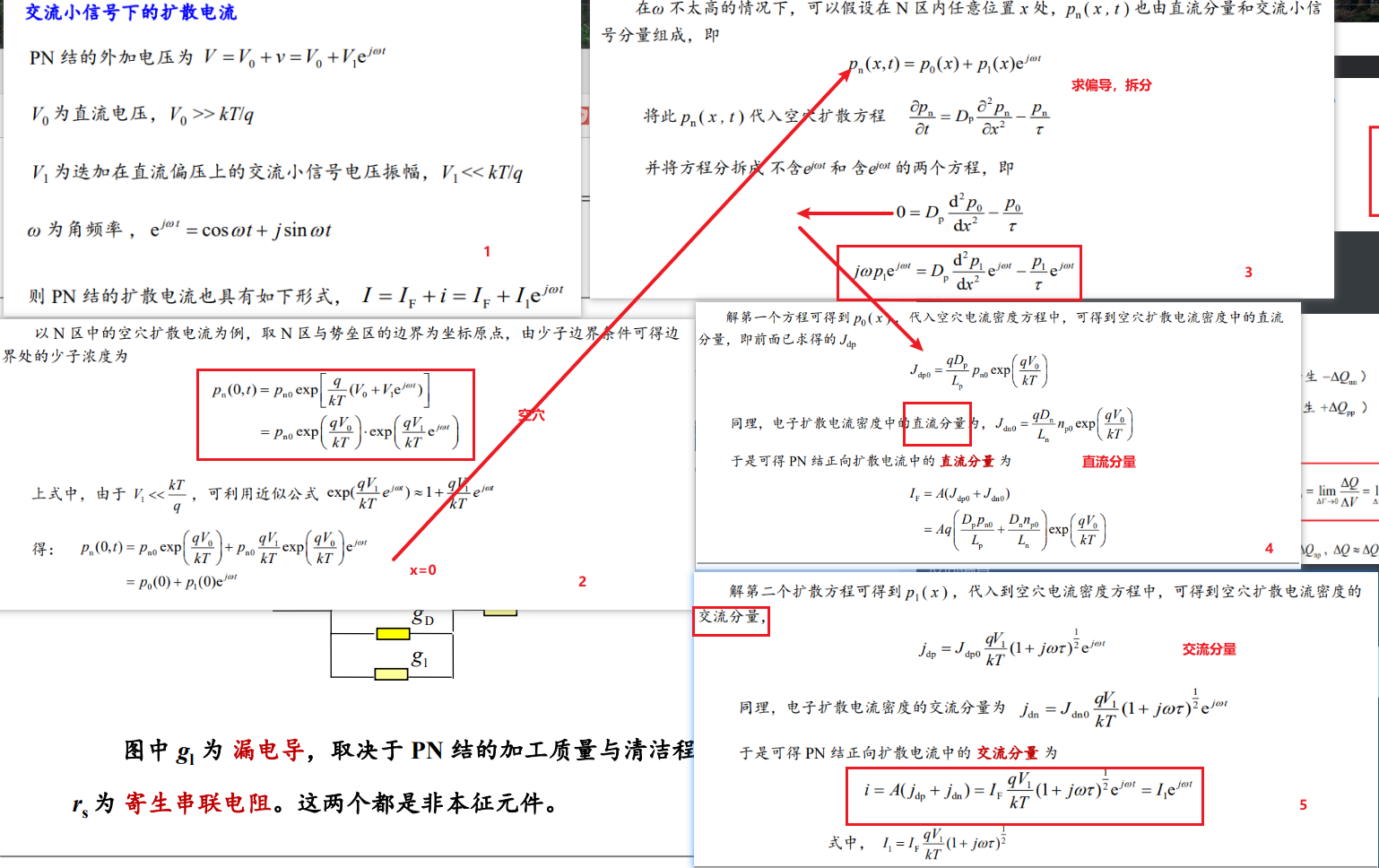

pn结扩散电容

求扩散电容

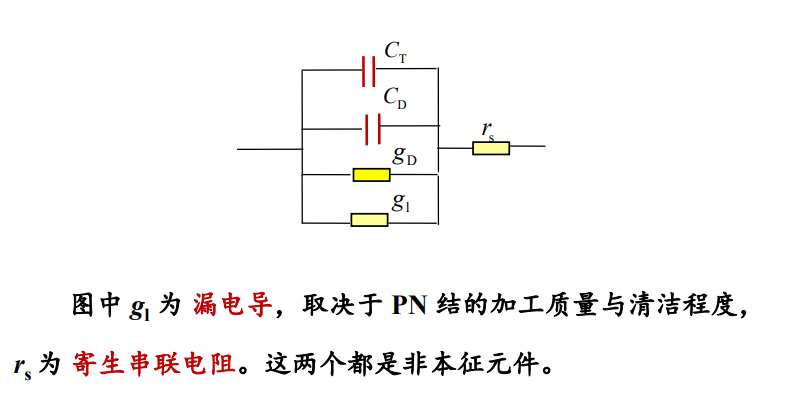

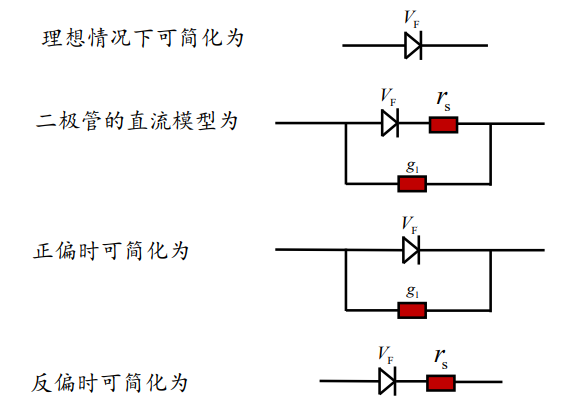

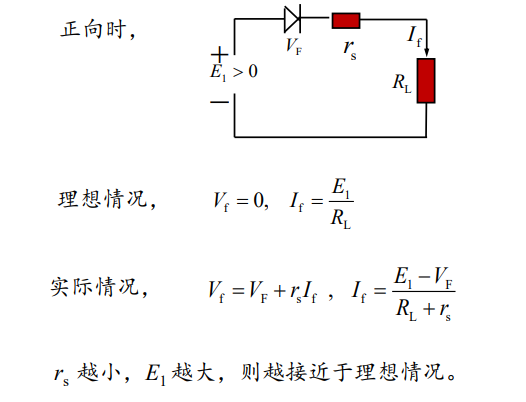

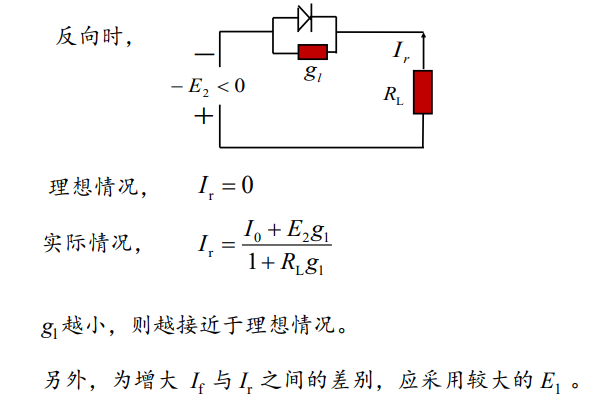

漏电导,取决于PN结加工质量与清洁程度,rs是寄生串联电阻,都是非本征元件

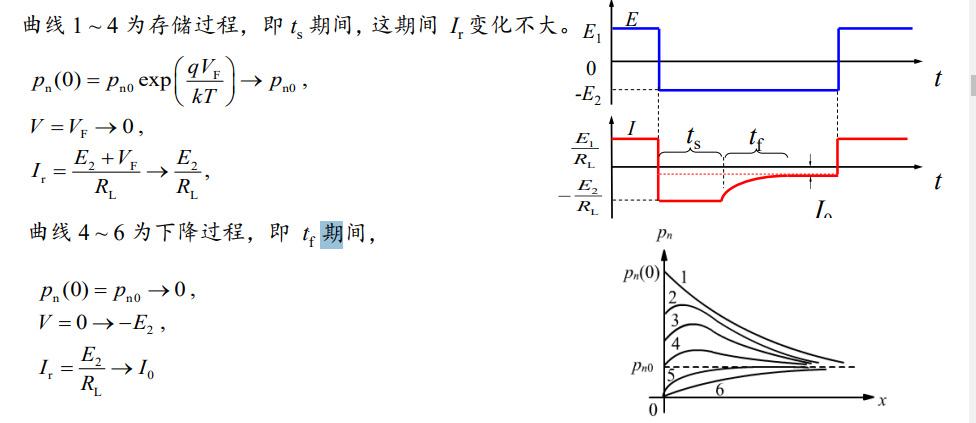

pn结直流开关特性

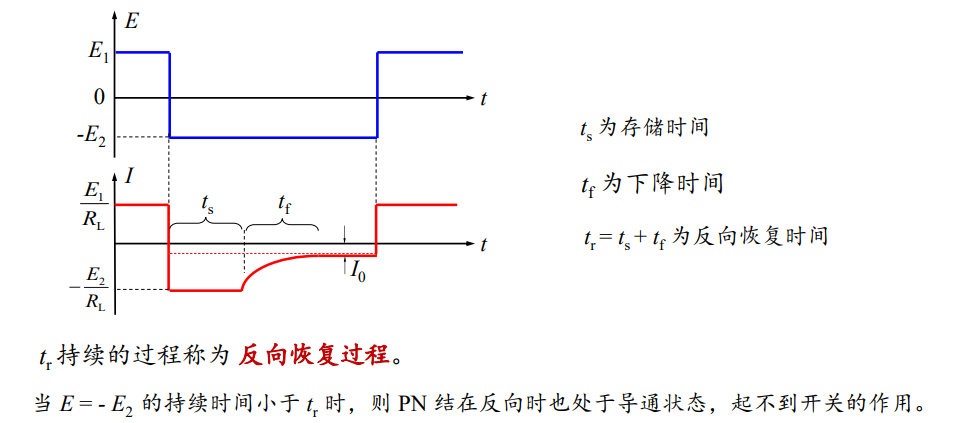

pn瞬态开关特性

tr持续过程是反向恢复过程

当 E = - E2 的持续时间小于 t r 时,则 PN 结在反向时也处于导通状态,起不到开关的作用。

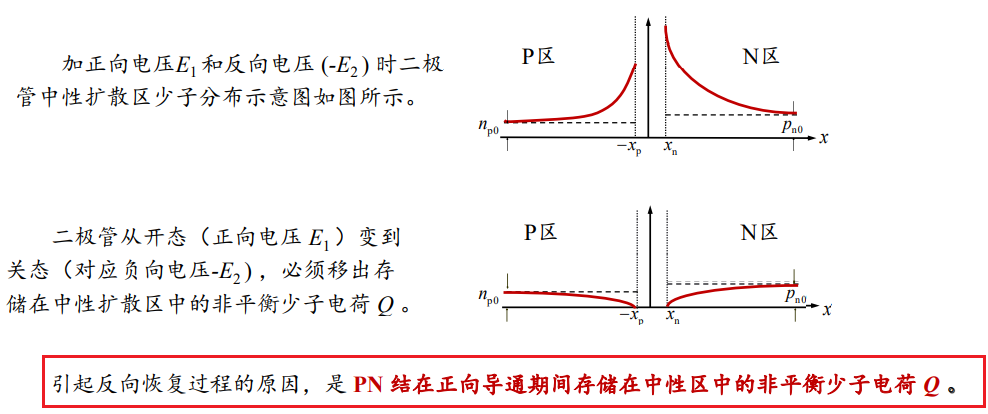

加正向电压E1 和反向电压 (-E2 ) 时二极 管中性扩散区少子分布示意图如图所示

引起反向恢复过程,是PN解在正向导通器件存储在中性区中非平衡少子电荷Q

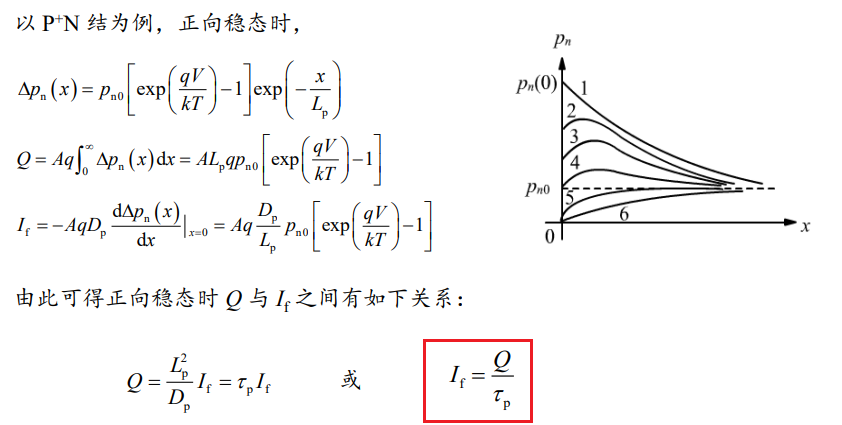

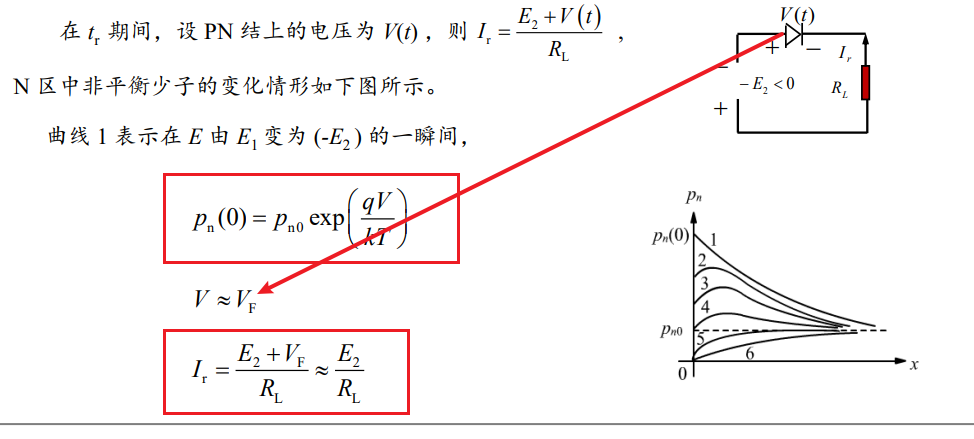

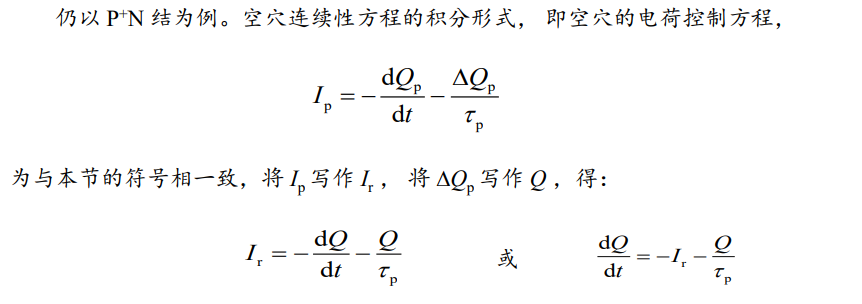

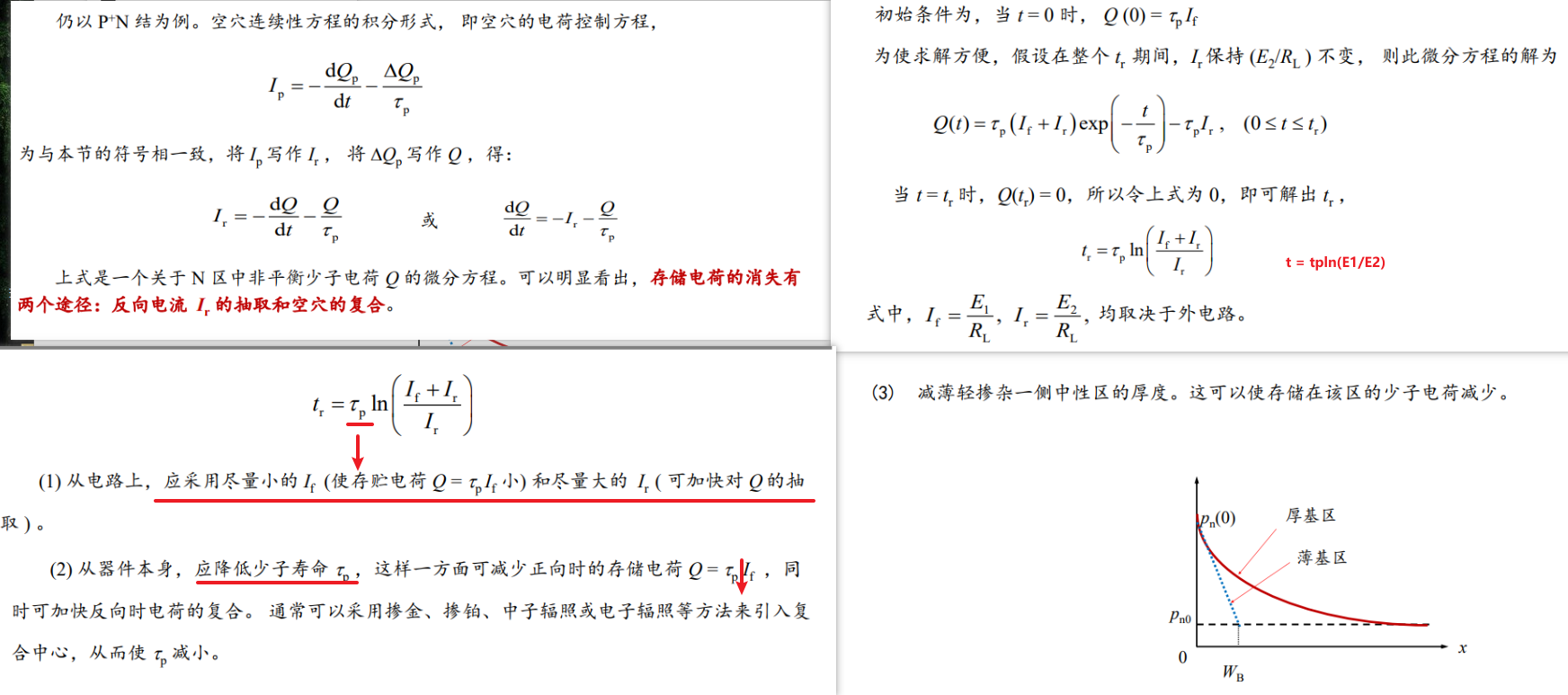

PN结开关时间

存储电荷的消失有 两个途径:反向电流 Ir 的抽取和空穴的复合

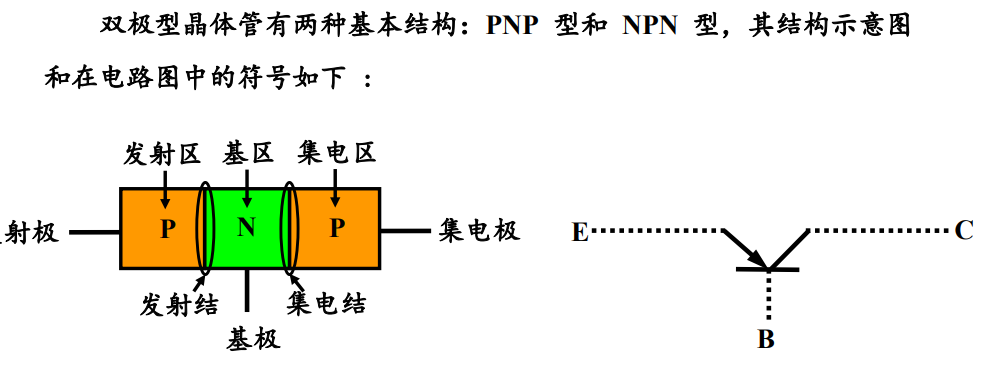

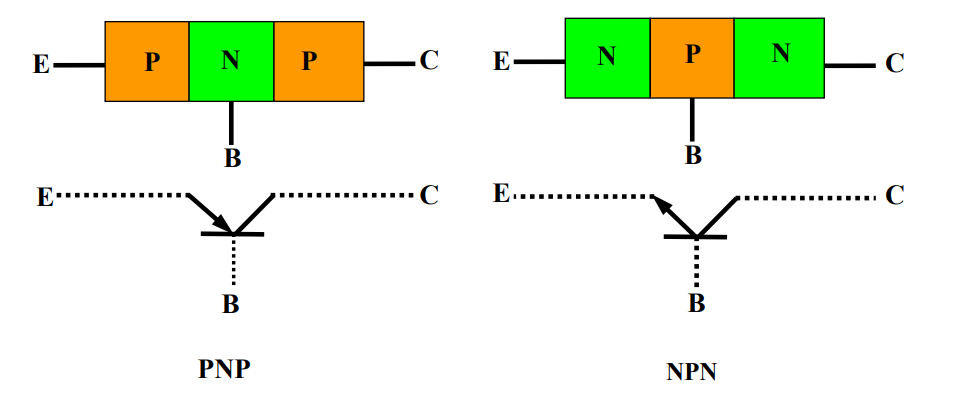

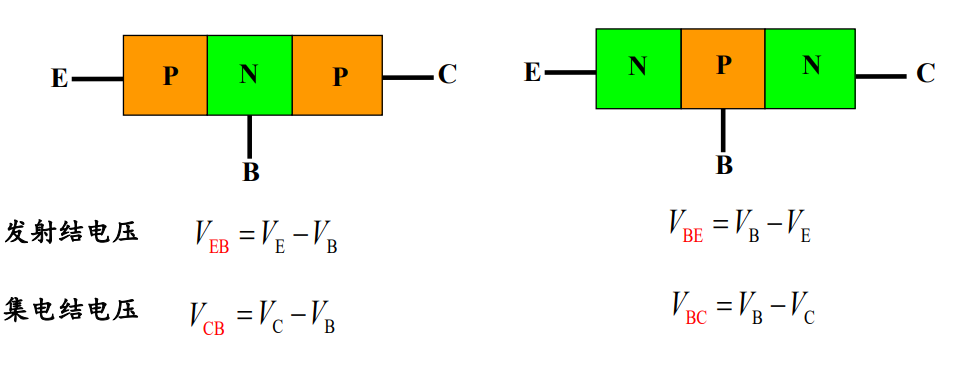

双极型晶体管

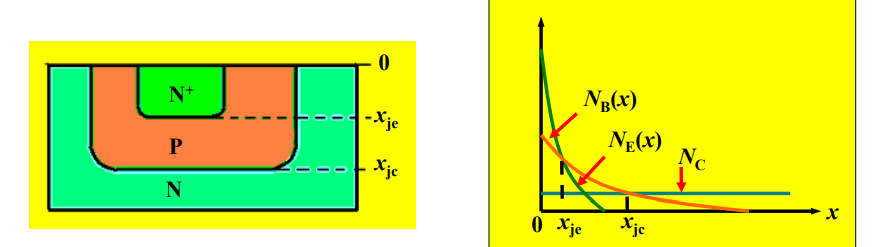

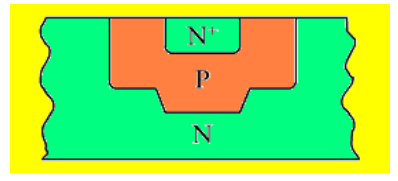

双极结型晶体管结构

PN结正向电流来源是多子,正向电流很大,反向电流是少子,反向电流很小

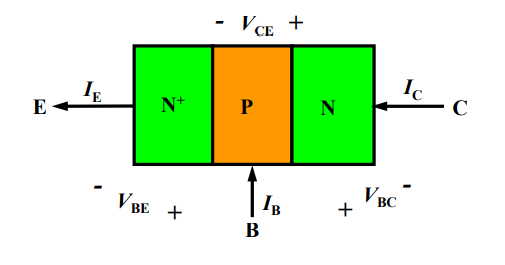

电路图

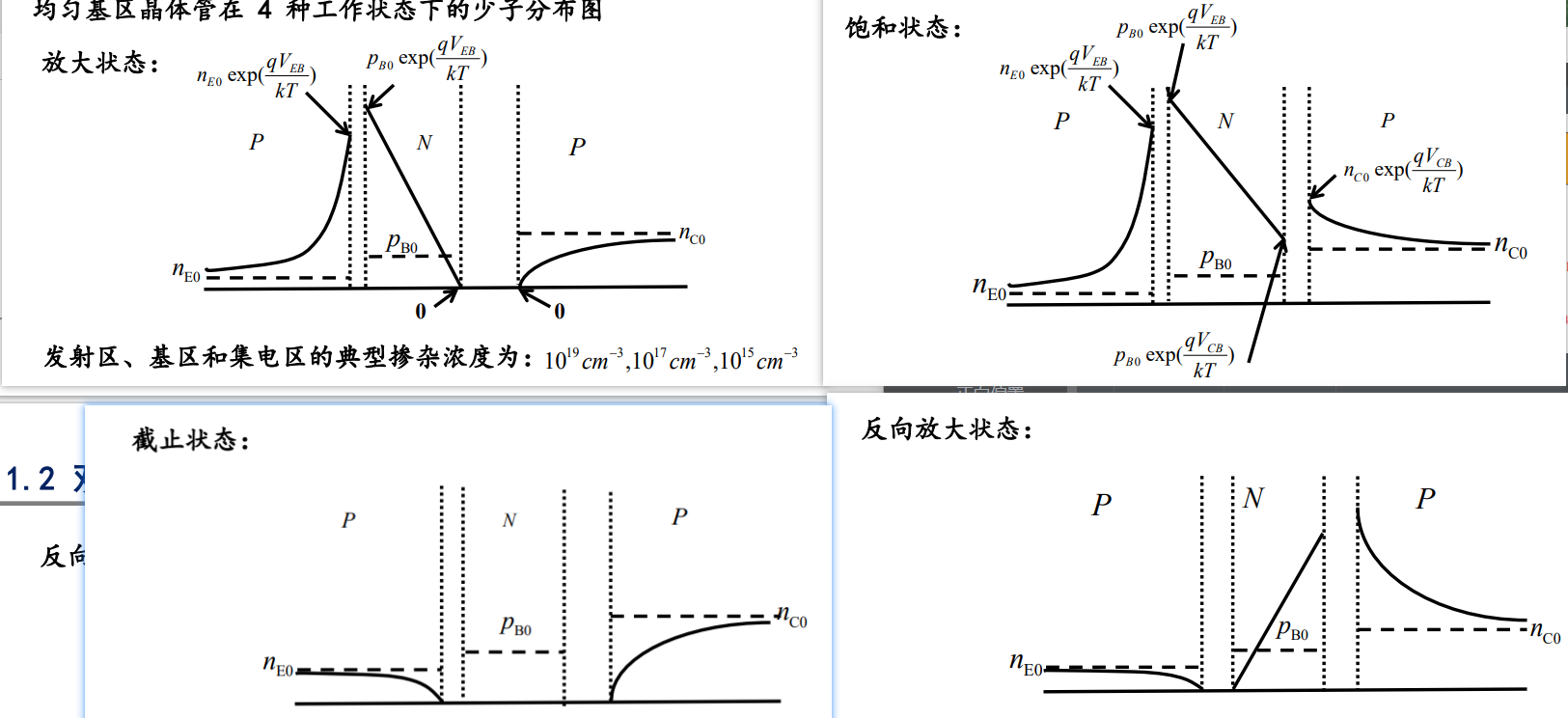

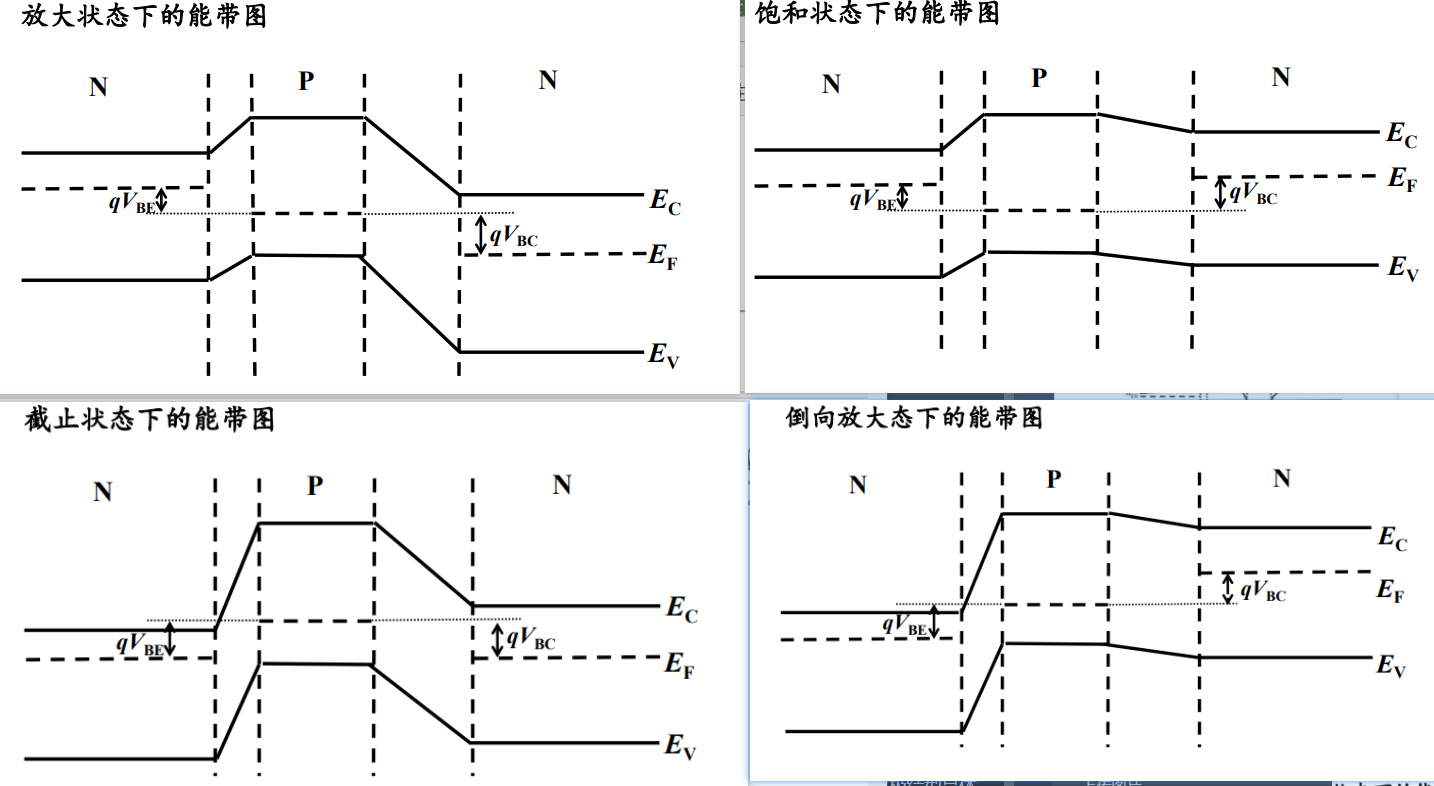

| E 结 | C 结 | 工 作 状 态 |

|---|---|---|

| + | - | 放大状态,用于模拟电路 |

| + | + | 饱和状态,用于数字电路 |

| - | - | 截止状态,用于数字电路 |

| - | + | 倒向放大状态 |

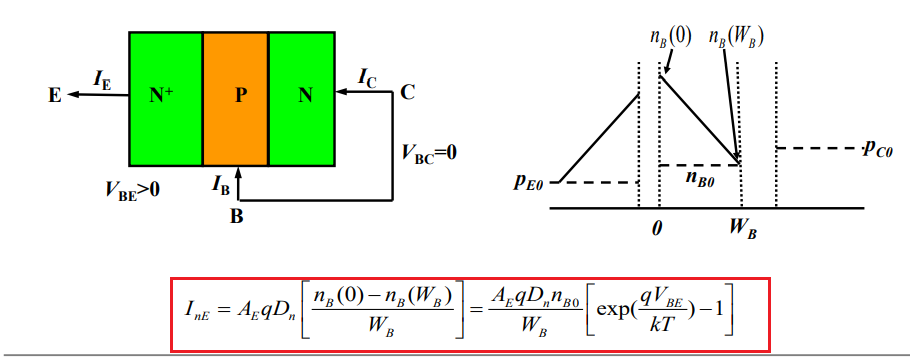

双极型晶体管少子分布图

均匀晶体管4种工作状态下少子分布图

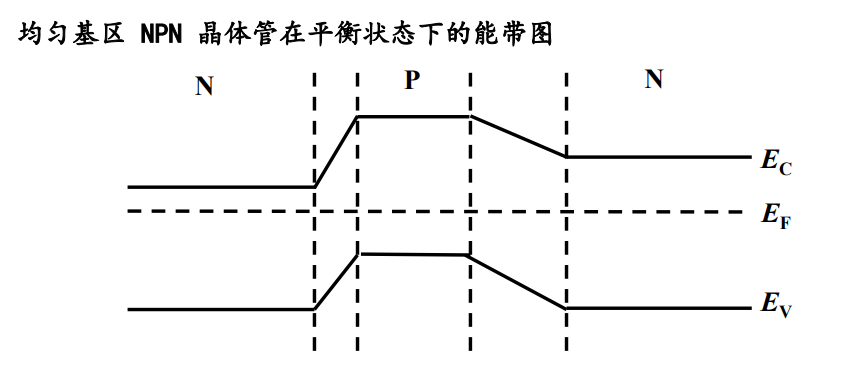

双极型晶体管能带图

均匀基区NPN晶体管在平衡状态下能带图

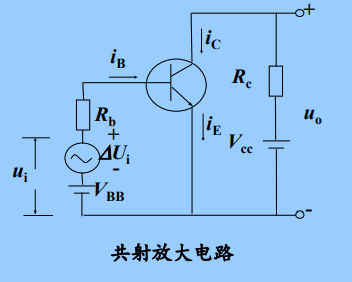

晶体管放大电路有两种基本类型:共基极接法与共发射极接法。

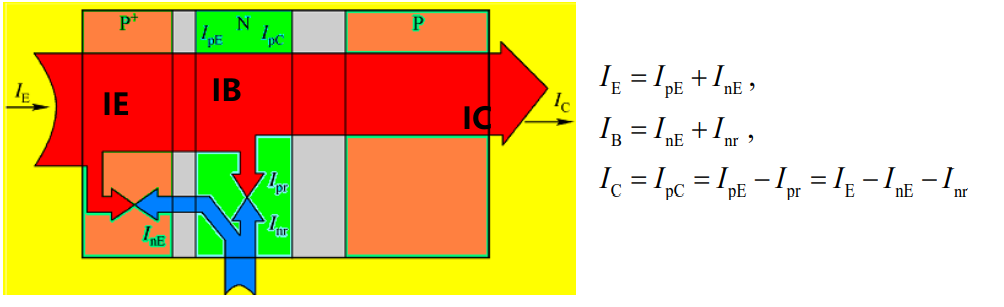

双极型晶体管放大作用

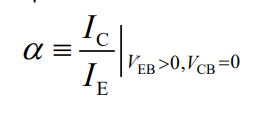

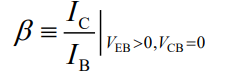

定义:发射结正偏,集电结 零偏 时的 IC 与 IE 之比,称为共基极直流短路 电流放大系数,记为 α ,即

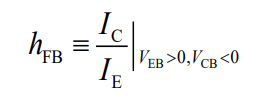

定义:发射结正偏,集电结 反偏 时的 IC 与 IE 之比,称为共基极静态电流 放大系数,记为 hFB ,即

定义:发射结正偏,集电结 零偏 时的 IC 与 IB 之比,称为共发射极直流短路 电流放大系数,记为β ,即

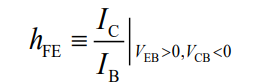

定义:发射结正偏,集电结 反偏 时的 IC 与 IB 之比,称为共发射极静态电 流放大系数,记为 hFE ,即

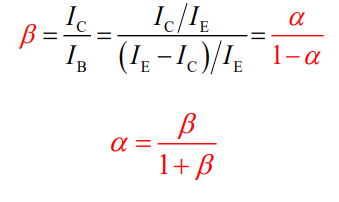

根据晶体管各端电流之间的关系:IB = IE - IC,以及 α 与β的定义,可得 α 与β之间的关系为

对于一般的晶体管, α = 0.9500 ~ 0.9950 ,β = 20 ~ 200

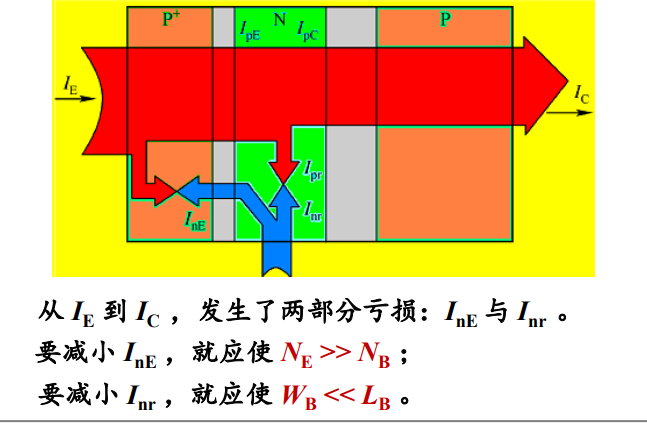

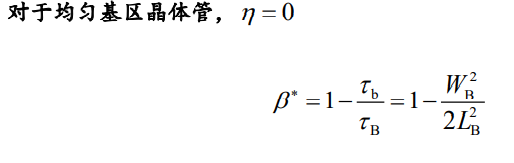

基区晶体管电流放大系数

要使晶体管区区别两个反向串联二极管具有放大作用,晶体管在结构上满足两个条件

- 少子在基区中复合必须很少,要求WB<<LB,可以利用基区输运系数定量分析

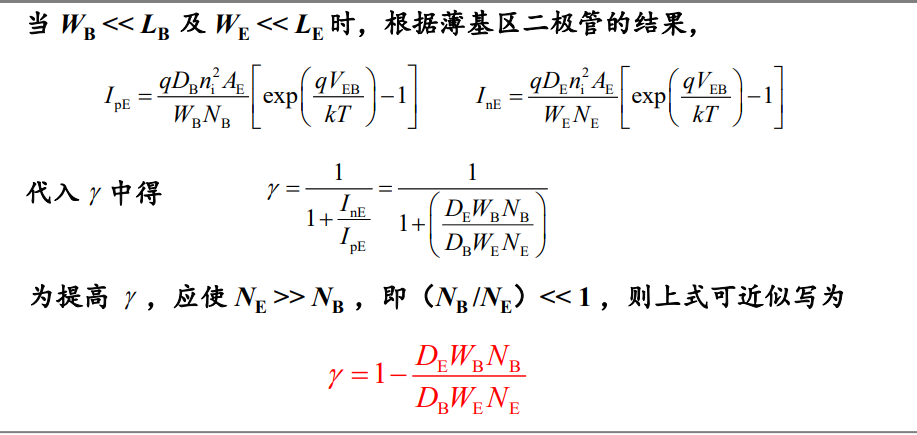

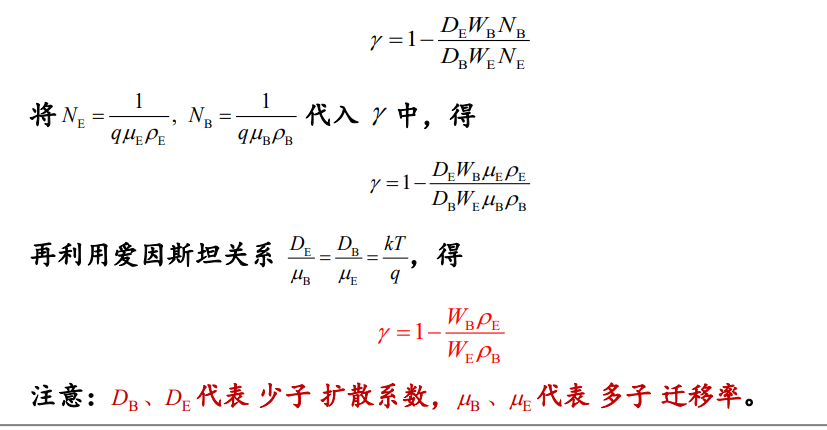

- 发射区注入基区少子形成的电流必须远大于基区注入发射区少子形成的电流,要求NE>>NB

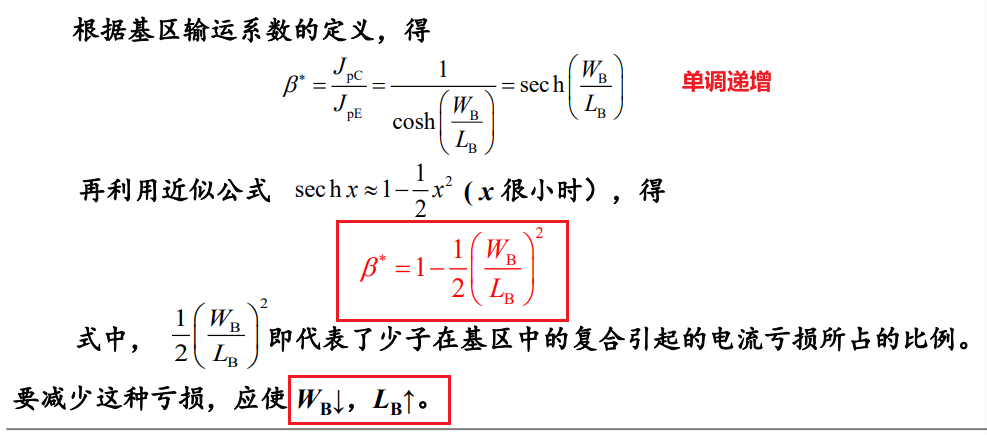

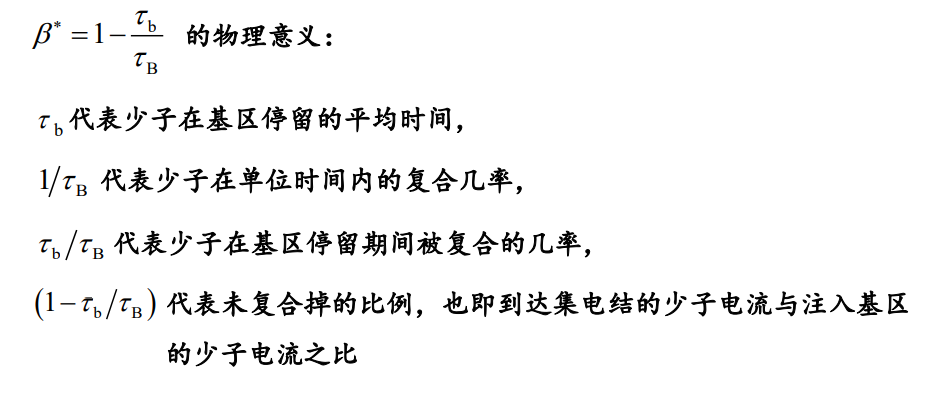

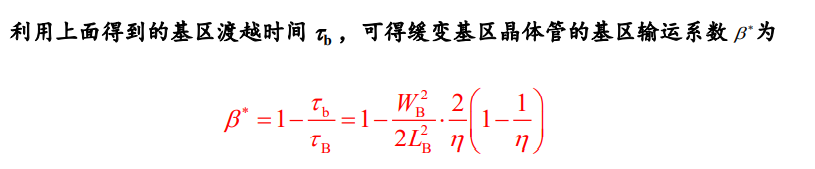

基区输运系数

定义:基区中到达集电结 的少子电流 与 从发射区注入基 区的少子形成的电流之比, 称 为 基区输运系数,记为 。对 于 PNP 管

由于少子空穴在基区的复 合,使 JpC < JpE , 。 β∗ <1

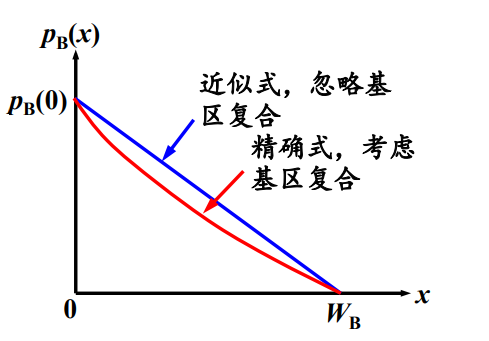

薄基区二极管精确结果

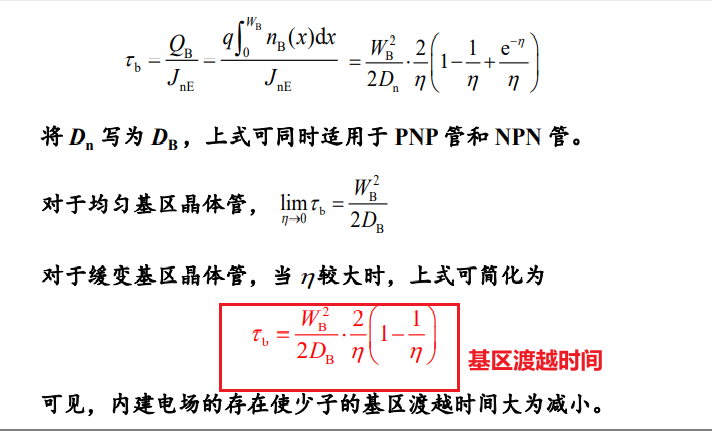

基区渡越时间

定义:少子在基区内从发射结渡越到集电结所需要的平均时间,称为少子的 基区渡越时间,记为 τb 。

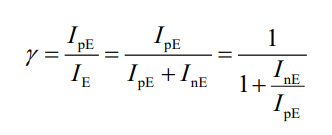

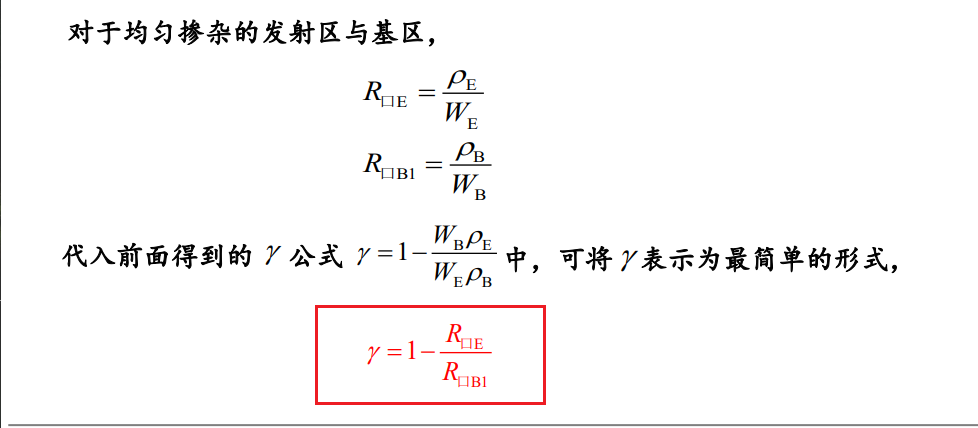

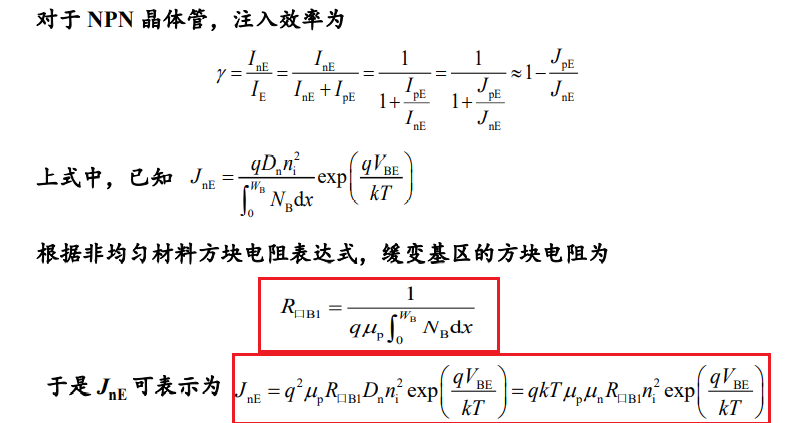

发射结注入效率

定义:从发射区注入基 区的少子形成的电流 与 总 的发射极电流之比,称为 注入效率(或 发射效率)

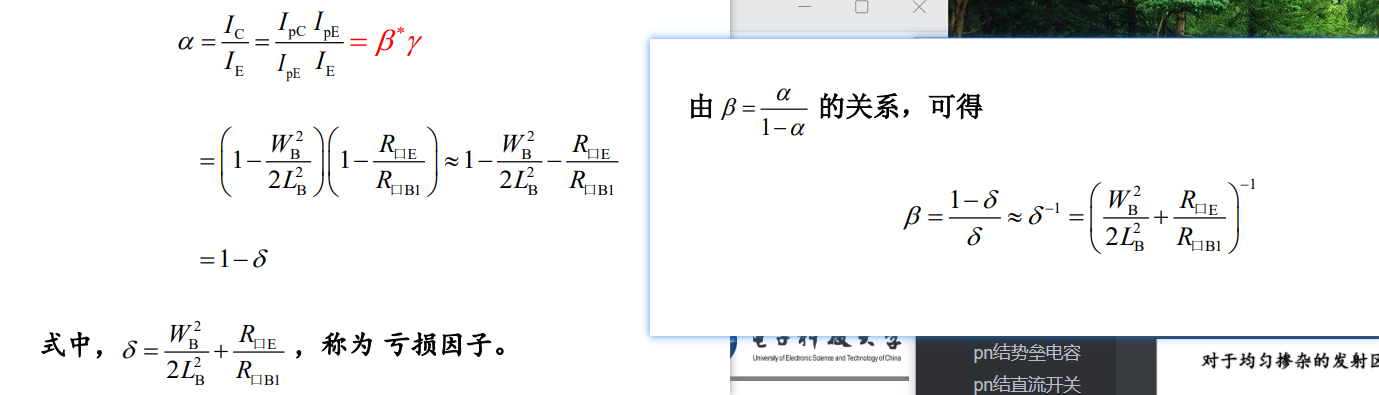

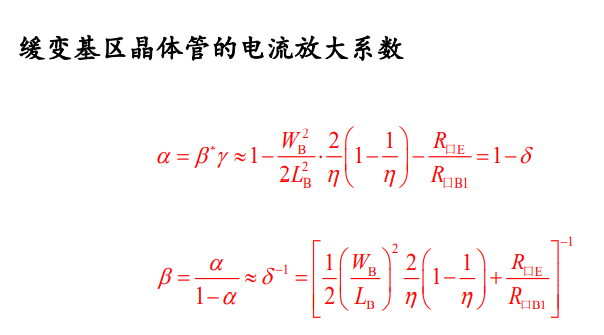

电流放大系数

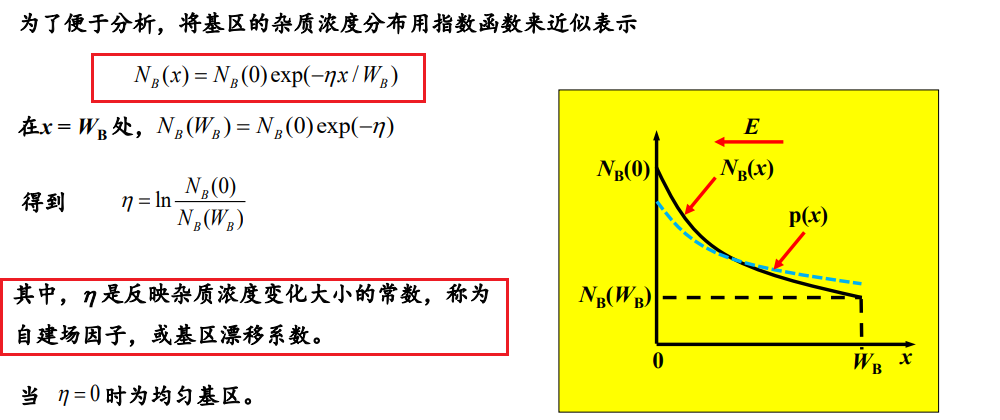

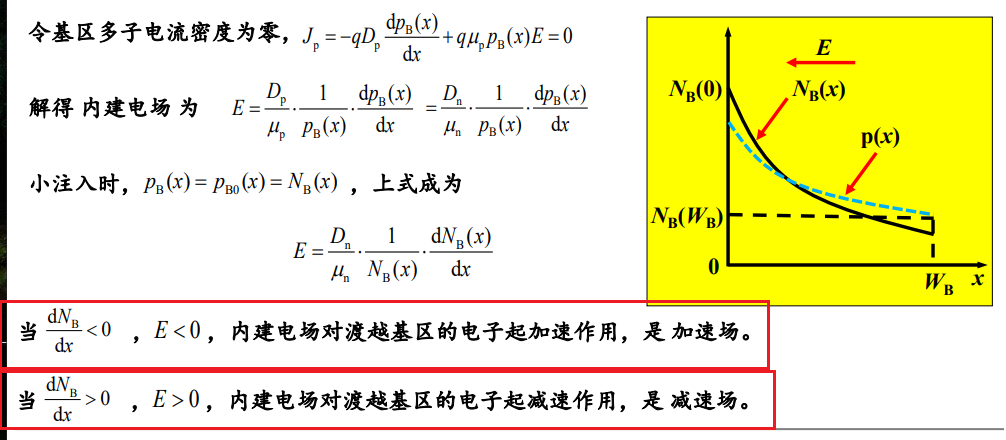

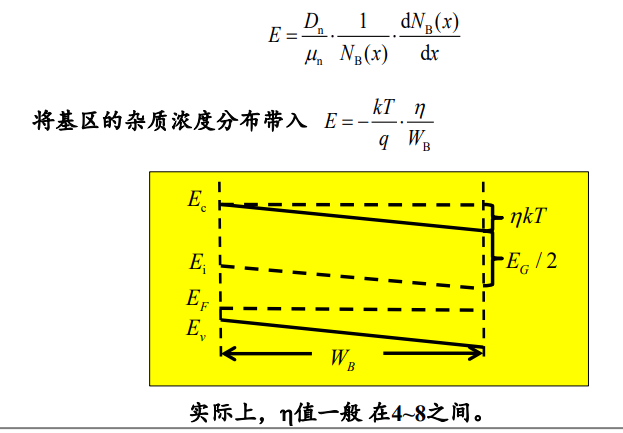

缓变基区晶体管内建电场

基区杂质分布的不均匀会在基区中产生一个内建电场 E ,使少子在基区内以漂移运动为主, 所以缓变基区晶体管又称为漂移晶体管

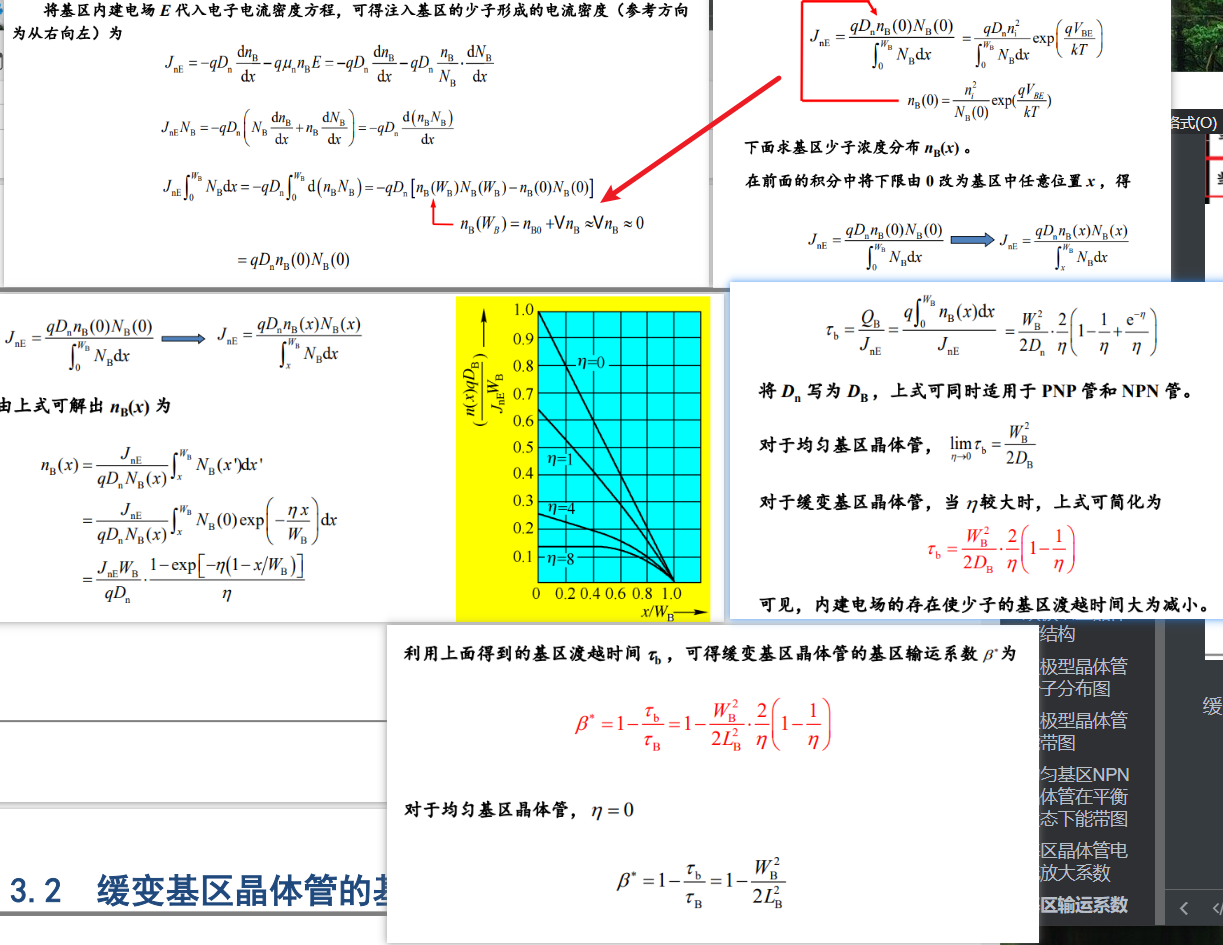

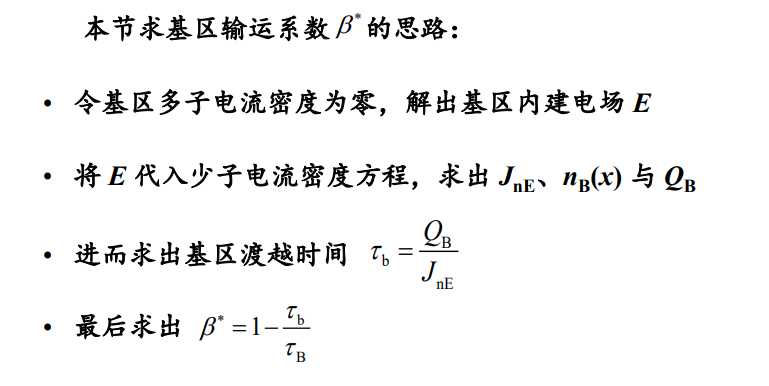

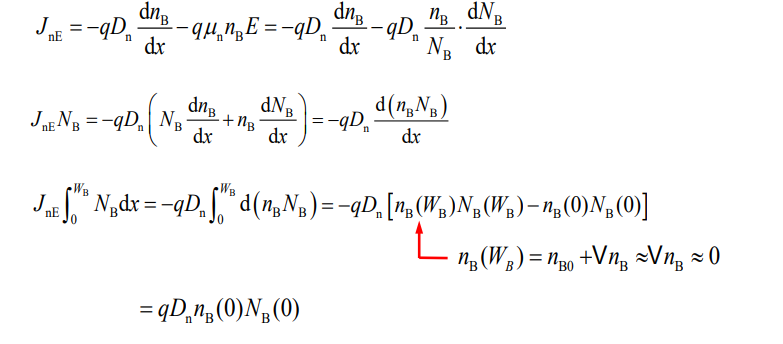

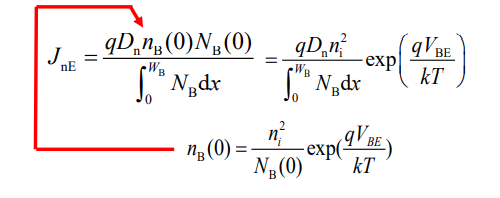

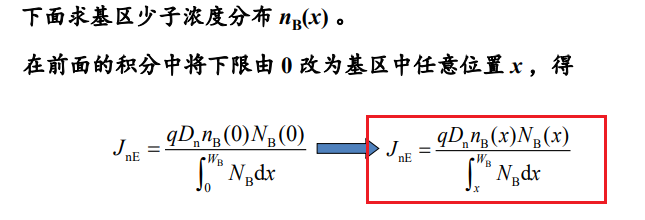

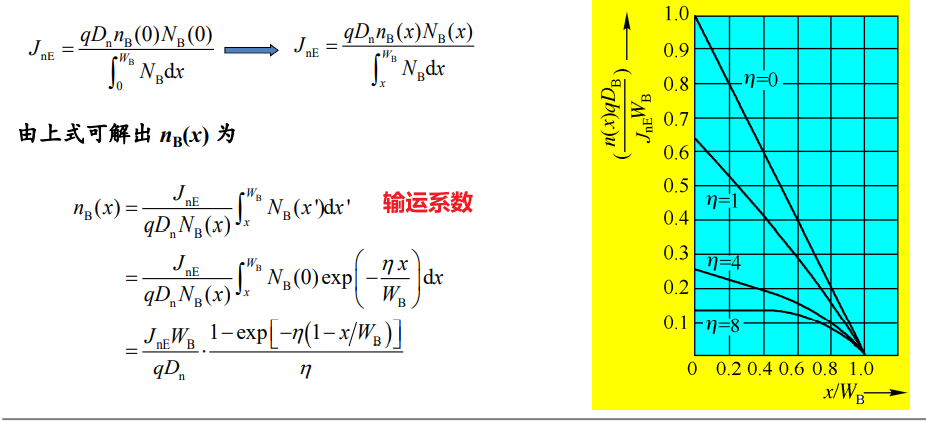

缓变基区晶体管基区输运系数

本节求基区输运系数 的思路

将基区内建电场 E 代入电子电流密度方程,可得注入基区的少子形成的电流密度(参考方向 为从右向左)为

内建电场存在使少子在基区渡越时间大大减小

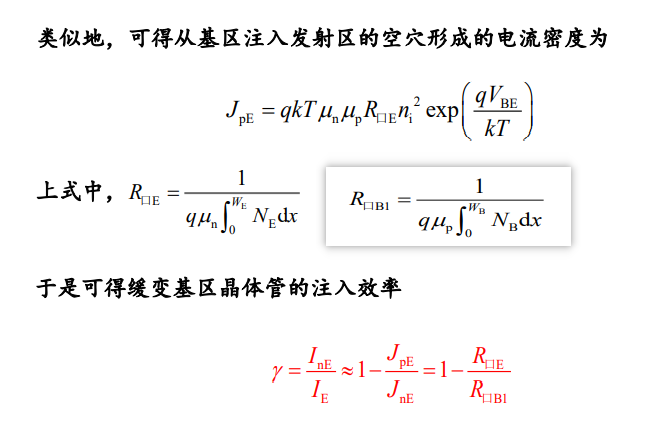

缓变基区晶体管电流放大系数

非理想情况下电流放大系数

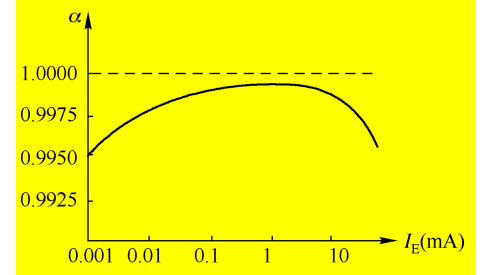

发射极电流Ie与α的关系

电流放大系数随发射极电流的变化

小电流α下降原因:当发射结正向电流很小,发射结势垒区,复合电流密度

JrE的比例将增大,使注入效率下降

当电流很大,α会开始下降,这是由于大注入效应,基区扩展效应引起的

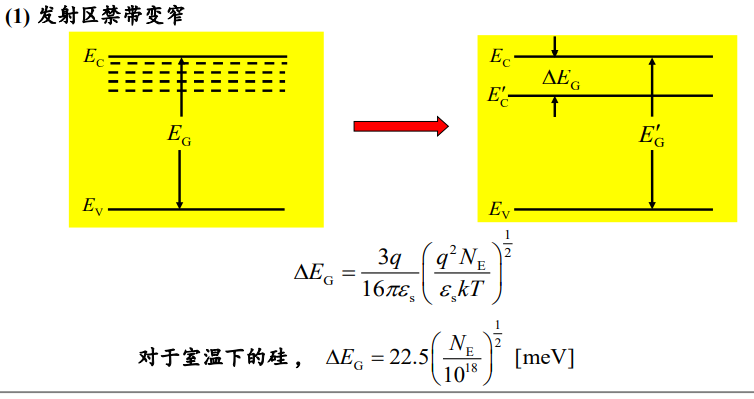

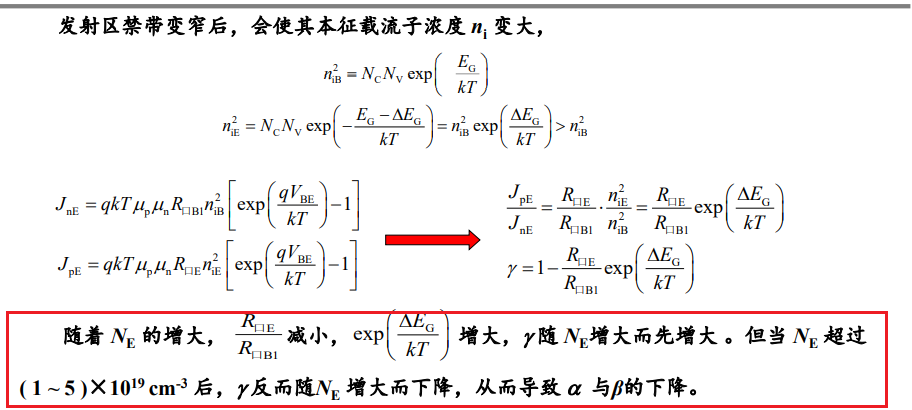

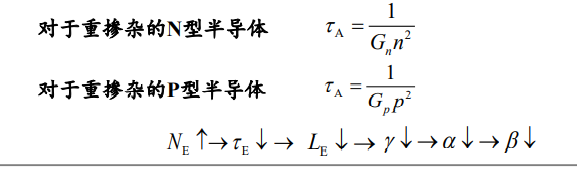

发射区重掺杂影响

发射区重掺杂效应:当发射区掺杂浓度NE太高,不但不能提高注入效率γ

反而会下降,从而使α 和β下降

原因:发射区禁带宽度变窄与发射区俄歇复合增强

发射区俄歇复合增强

基区陷落效应

当发射区磷掺杂浓度很高,会使发射区下方集电结结面向下扩展,这个现象叫基区陷落效应

由于基区陷落效应,使得结深不易控制,难以将基区宽度做的很薄

为了避免基区陷落效应,目微波晶体管发射区掺杂多采用坤来代替磷

异质结双晶体管

选择不同材料制作发射区基区,使两区具有不同禁带宽度

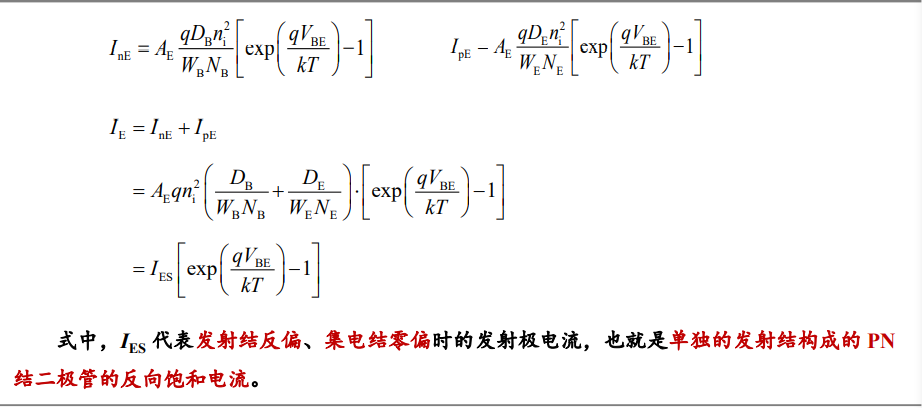

集电结发射结短路电流

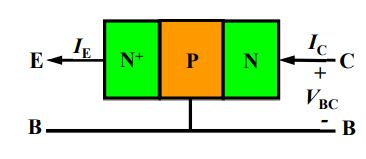

电流方向和电压参考极性

集电结短路时电流

式中,IES 代表发射结反偏、集电结零偏时的发射极电流,也就是单独的发射结构成的 PN 结二极管的反向饱和电流

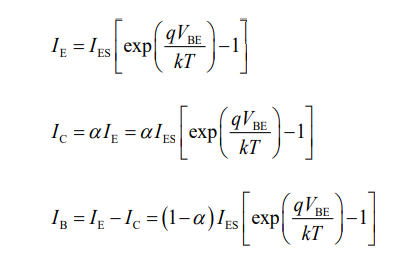

于是可得到发射结为任意偏压、集电结零偏时晶体管三个电极上的电流为

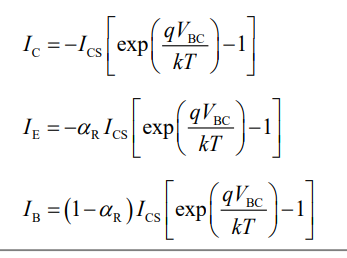

把晶体管的发射区当作“集电区”,集电区当作 “发射区”,就可得到一个倒过来应用的晶体 管,称为 倒向晶体管。发射结短路就相当于倒向晶体管的“集电结”短路,因此晶体管在本小节 的偏置状态就相当于倒向晶体管在上一小节的偏置状态。故可得

式中,ICS 代表集电结反偏、发射结零偏时的集 电极电流,也就是单独的集电结构成的 PN 结二极管 的反向饱和电流。 代表倒向管的共基极直流短路电流放大系数, 通常比 小得多

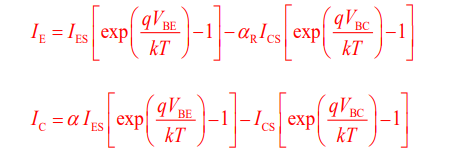

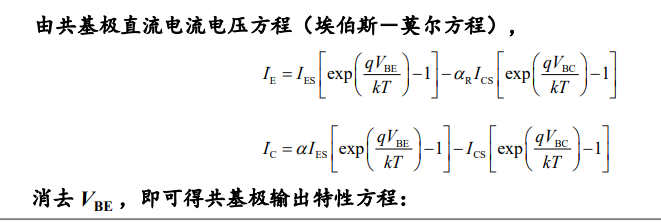

埃伯斯-莫尔方程

即可得到发射结和集电结上均外加任意电压时晶体管的 直流电流电压方程

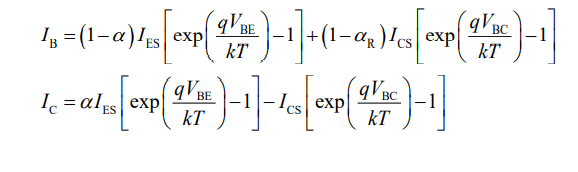

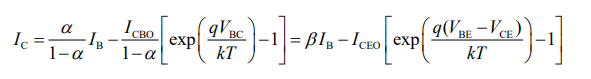

若选取 IB 与 IC

所得为共发射极直流电流电压方程,

正向管与倒向管之间存在一个 互易关系 ,

晶体管输出特性

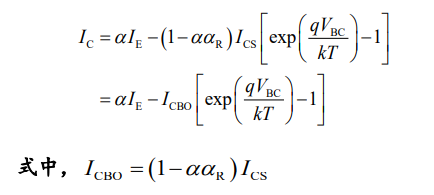

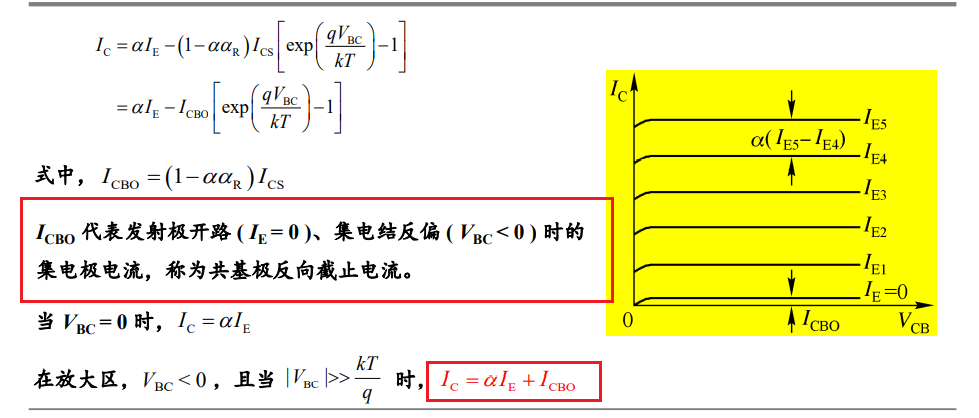

共基极输出特性

以输入端的 IE 为参变量,输出端的 IC 与 VBC 之间的关系

共发射极输出特性方程

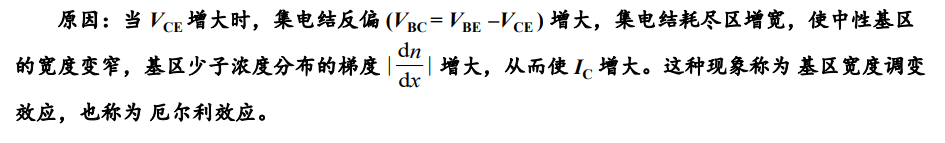

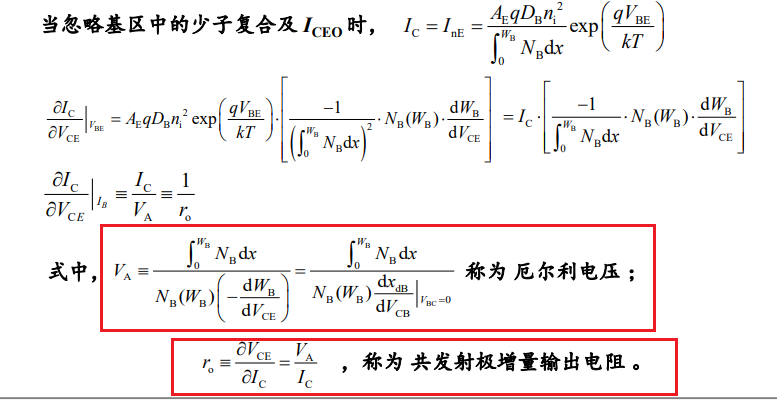

基区宽度调变效应

在共发射极放大区,理论上 ,即 IC 与 VCE 无关。但在实际的晶体管中,IC 随 VCE 的增大会略有增大 。

厄尔利效应

为减小厄尔利效应,应增大基区宽度 WB ;减小集电结耗尽区在基区内的宽度 xdB ,即增大基 区掺杂浓度 NB 。

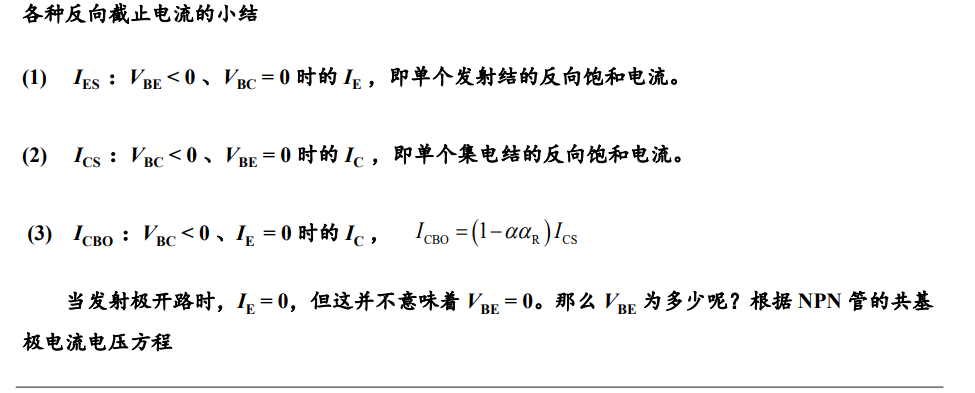

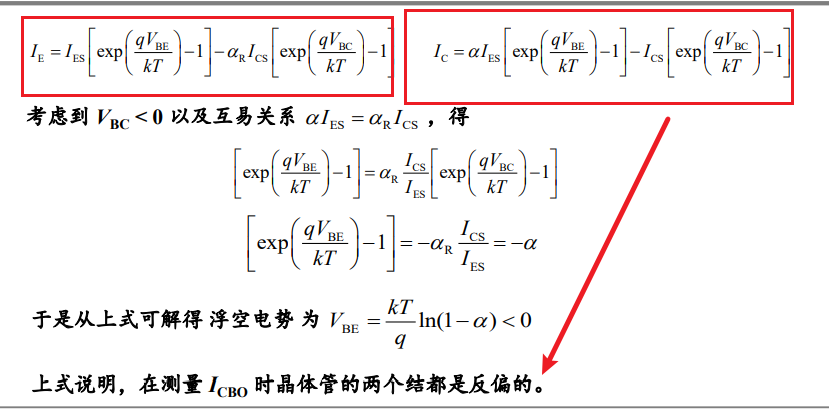

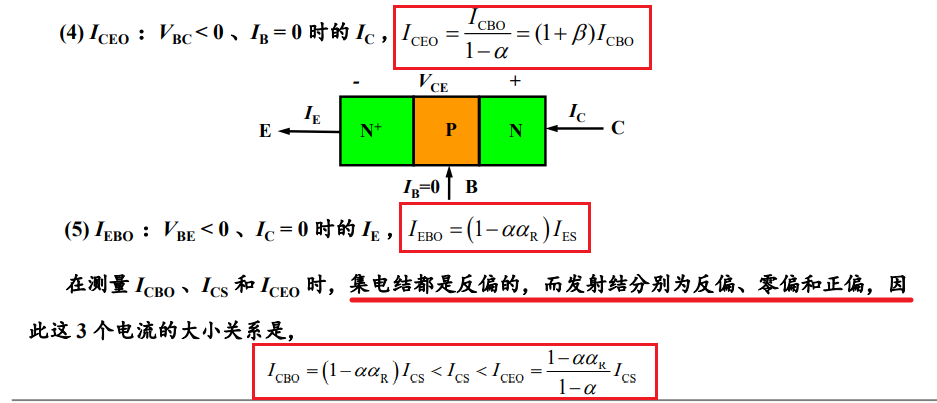

反向截止电流小结

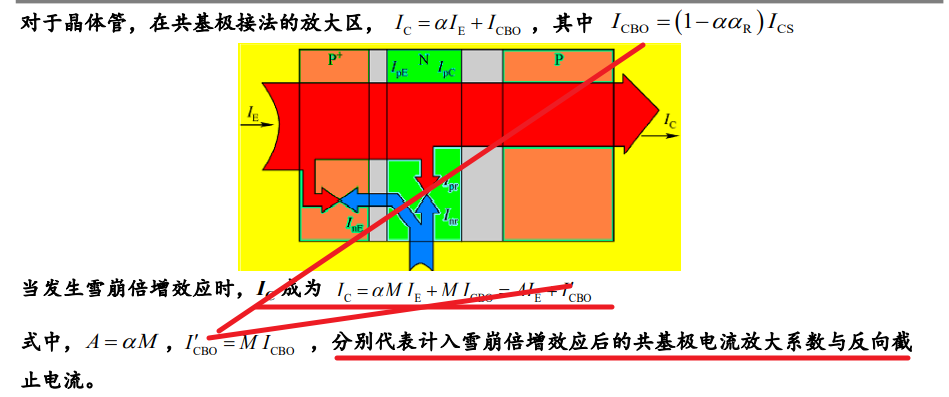

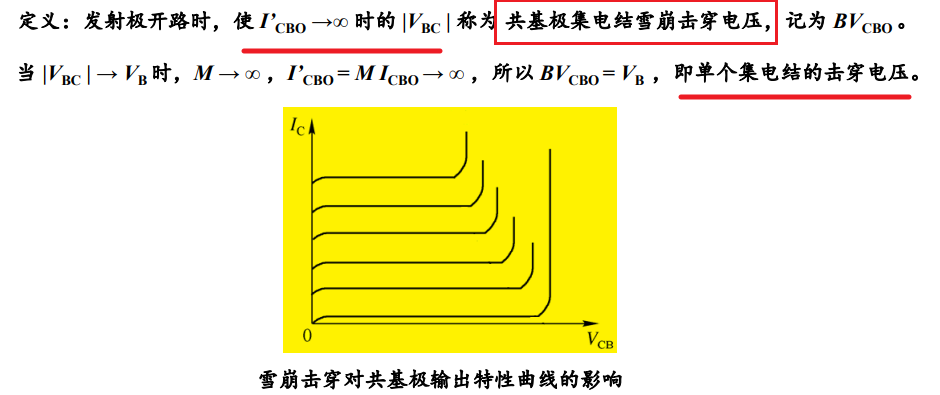

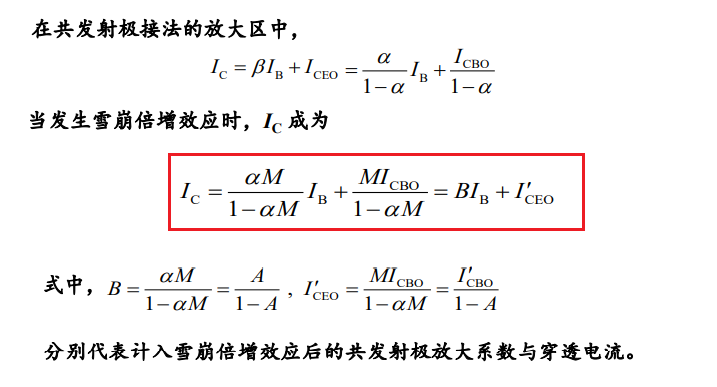

雪崩击穿电压

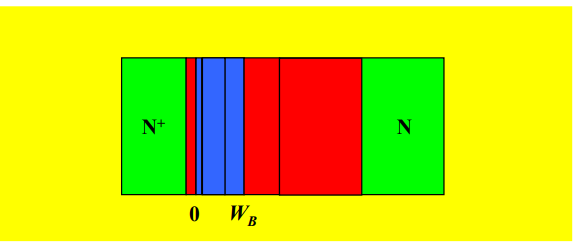

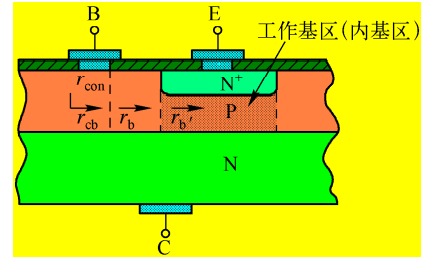

基区穿透效应

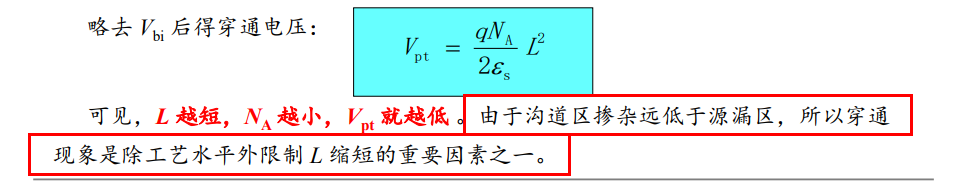

集电结上的反向电压增大到其势垒区将基区全部占据时,WB ’ = 0,这种现象称为 基区穿通, 相应的集电结反向电压称为 基区穿通电压,记为 Vpt。

基区穿透,进入基区中的势垒区宽度与基区宽度相等,对于突变结,当忽略Vbi时

防止基区穿通的措施:增大 WB 与 NB 。这与防止厄尔利效应的措施一致,但与提高放大系 数 与 的要求相矛盾。

基区局部穿透

在平面晶体管中 ,NB > NC ,势垒区主要向集电区扩展 ,一般不易发生基区穿通。但可能由于 材料的缺陷或工艺的不当而发生局部穿通

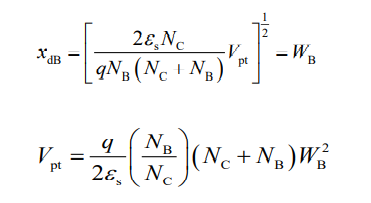

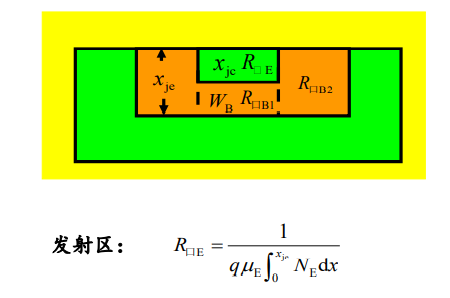

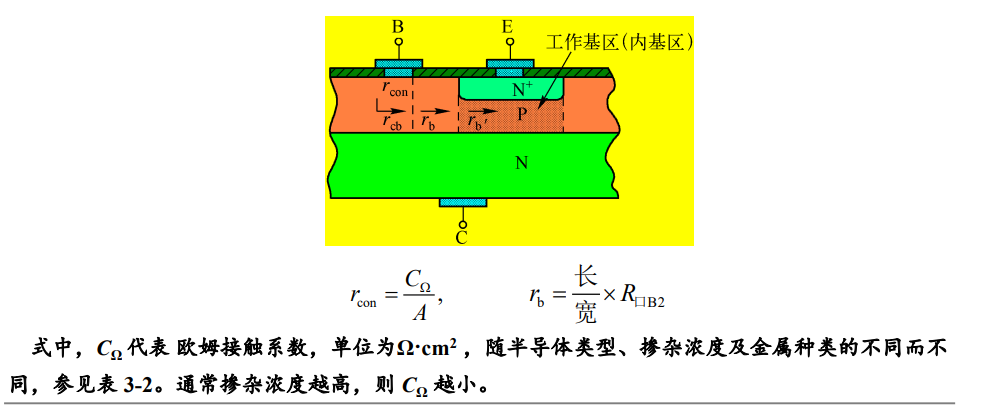

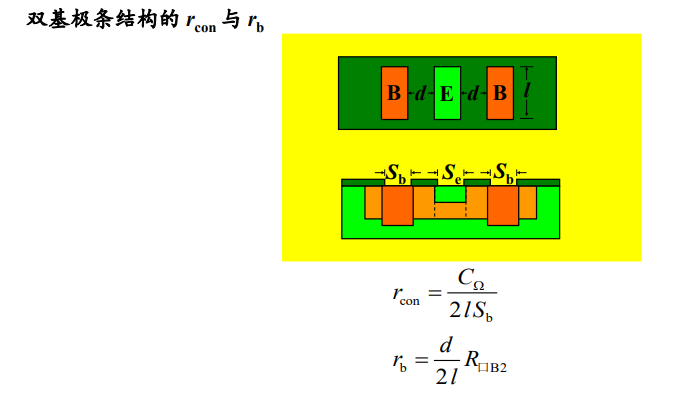

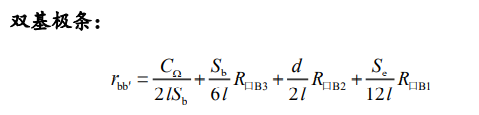

基极电阻

把基极电流 IB 从 基极引线 经 非工作基区 流到 工作基区 所产生的电压降,当作是由一个电 阻产生的,称这个电阻为 基极电阻,用 rbb’ 表示 。由于基区很薄,rbb’ 的截面积很小,使 rbb’ 的数 值相当可观,对晶体管的特性会产生明显的影响

基极电阻

- 基极电阻有四部分构成

- 基极金属电极与基区欧姆接触电阻 rcon

- 基极接触处到基极接触孔边缘的电阻 rcb

- 基极接触孔边缘到工作基区边缘的电阻rb

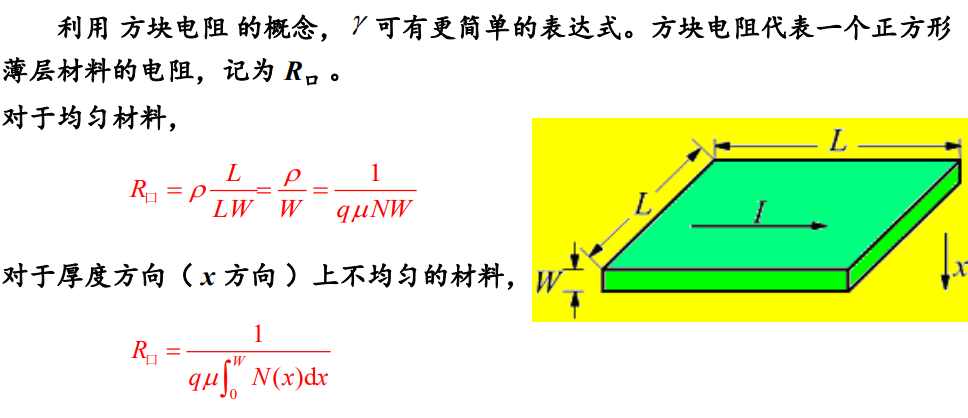

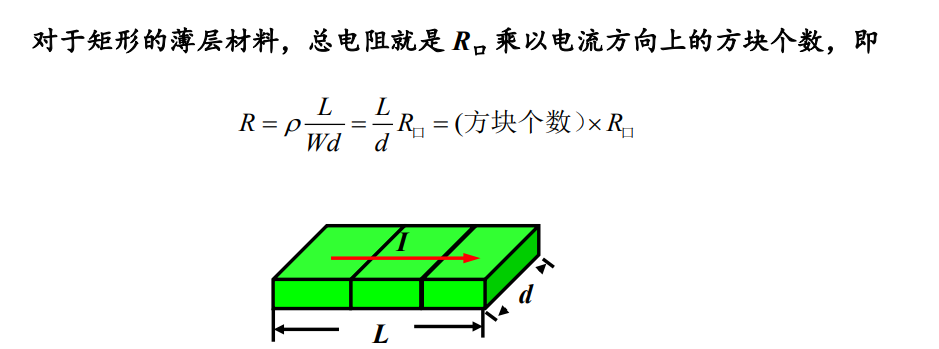

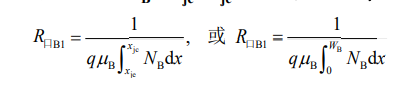

晶体管中各个区的方块电阻分别为

工作基区

指正对着发射区下方的在 WB = xjc - xje 范围内的基区,也称为 有源基区 或 内基区

非工作基区:指在发射区下方以外从表面到 xjc 处的基区,也称为 无源基区 或 外基区

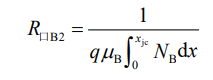

在产生电阻 rb’ 与 rcb 的基区内,基极电流是随距离变化的分布电流 Ib(y),因此这个区域内的 基极电阻是分布参数而不是集中参数。但是对于了解一些现象的物理机理,以及对于一些简化的 工程计算及电路研究而言,可以采用 等效电阻 的概念

这里的等效,是指集中电流 IB 在等效电阻上消耗的功率与分布电流 Ib(y) 在相应的基区内消耗 的实际功率相等

(1)减小 RB1 与 RB2 ,即增大基区掺杂与结深,但这会降 低β,降低发射结击穿电压与提高发射结势垒电容

(2)非工作基区重掺杂,以减小 RB3 和 CΩ

(3)减小 Se 、Sb 与 d ,增长 l ,即采用细线条,并且增加基 极条的数目,但这受光刻工艺水平和成品率的限制

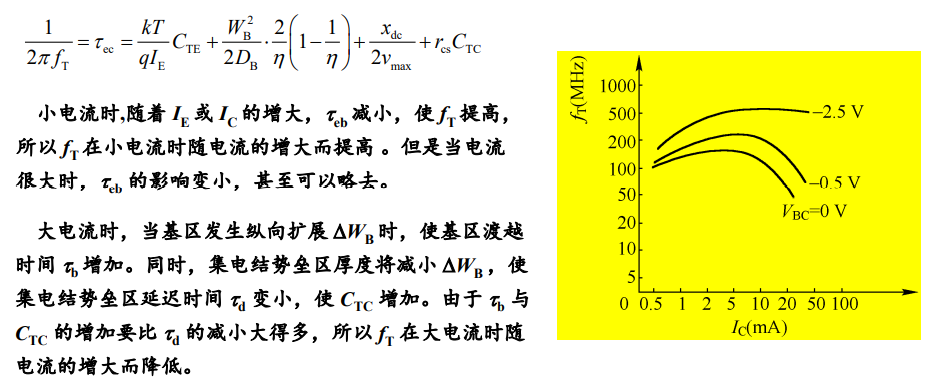

频率

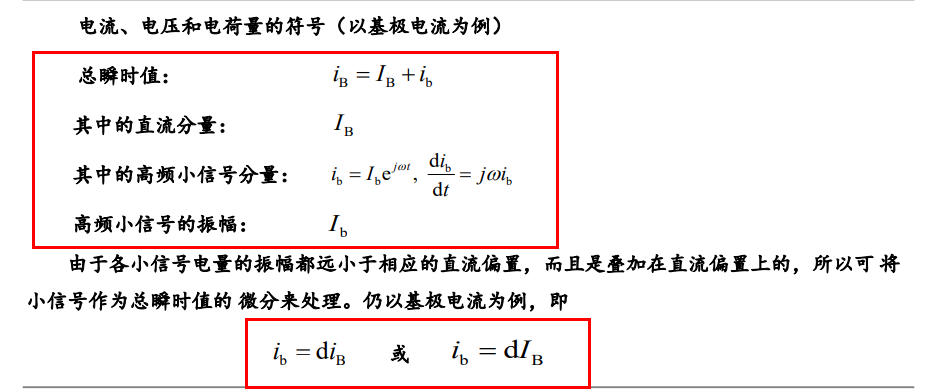

晶体管放大高频信号时,首先用被称为 “偏 置” 或 “工作点” 的直流电压或直流电流使晶体 管工作在放大区,然后 把欲放大的高频信号叠加 在输入端的直流偏置上 。 当 信号电压的振幅远小于 ( kT/q ) 时,称为 小信号。 这时晶体管内与信号有关的各电压、电流和电荷量,都 由直流偏置和高频小信号两部分组成,其高频小信号的 振幅都远小于相应的直流偏置。各高频小信号电量之间 近似地成 线性关系

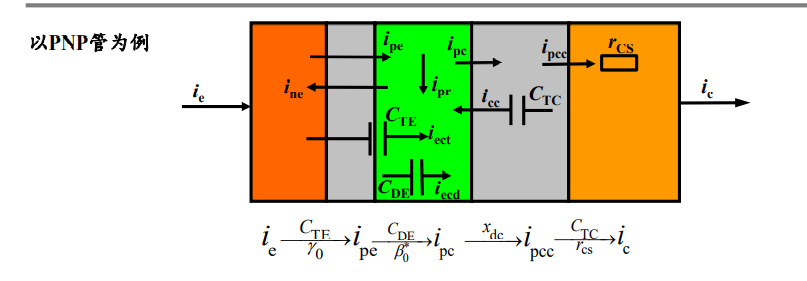

当晶体管中的电荷与电流作上述变化时,要消耗掉一部分从发射极流入的电流和需要一定的 时间。消耗掉的电流转变成了基极电流。信号的频率越高,电荷与电流的变化就越频繁,消耗掉 的电流就越大,从而使流出集电极的电流随频率的提高而减小

高频小信号电流变化

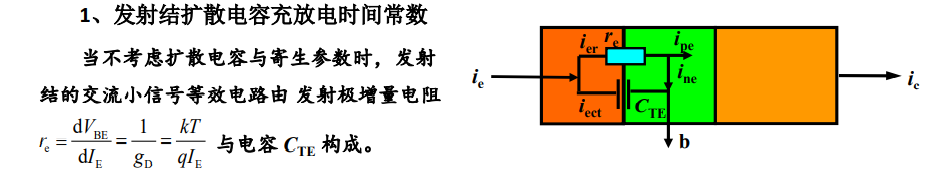

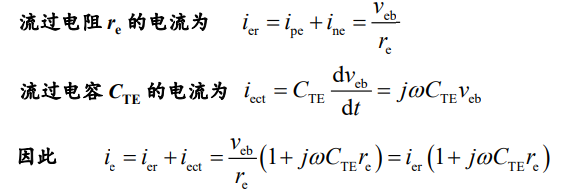

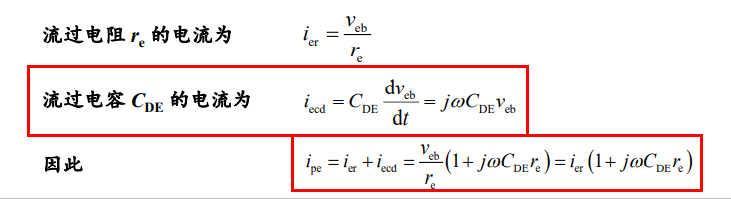

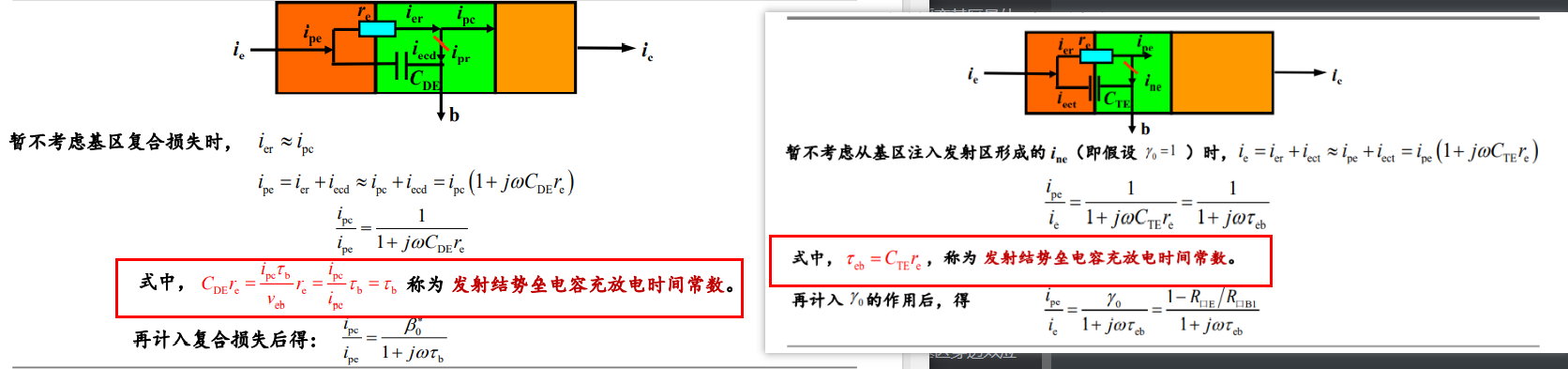

发射结扩散电容充放电时间常数

当不考虑势垒电容与寄生参数,发射结交流小信号等效电路由发射极增量电阻

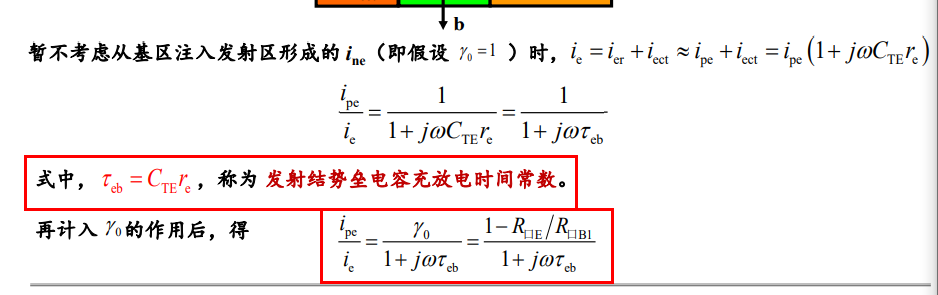

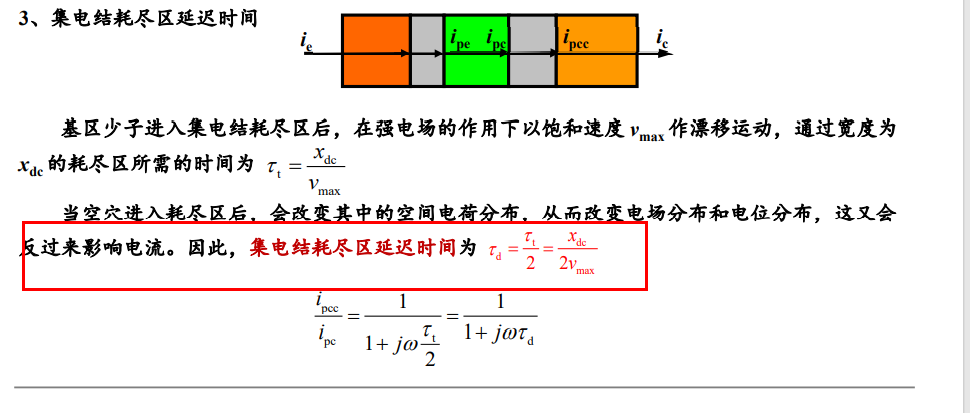

集电结耗尽区延迟时间

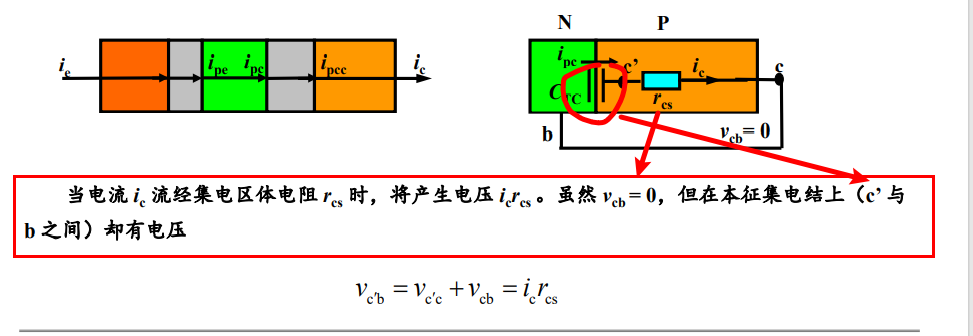

集电结势垒电容经集电区充放电区充放电时间常数

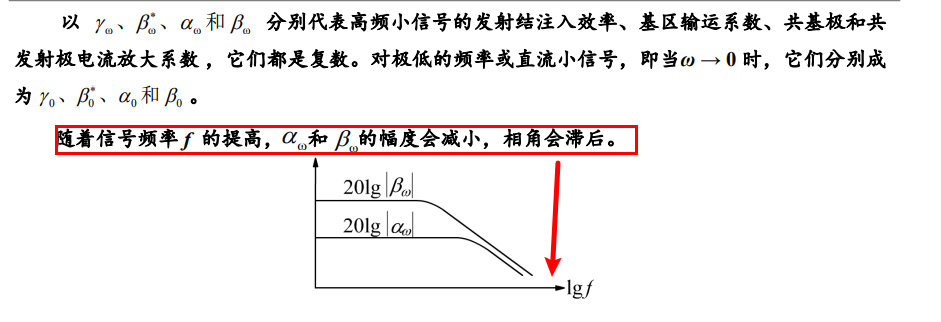

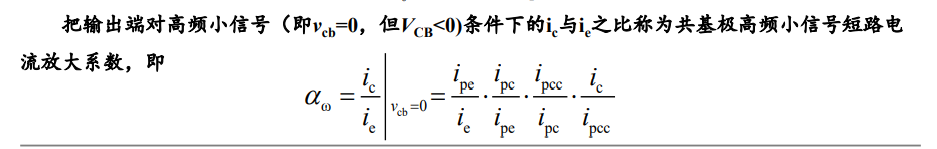

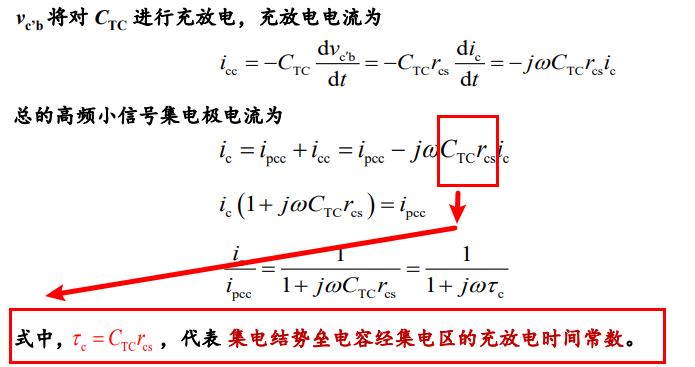

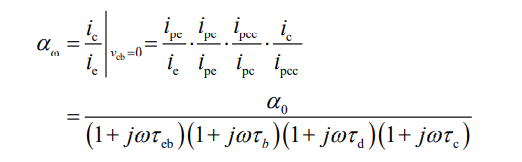

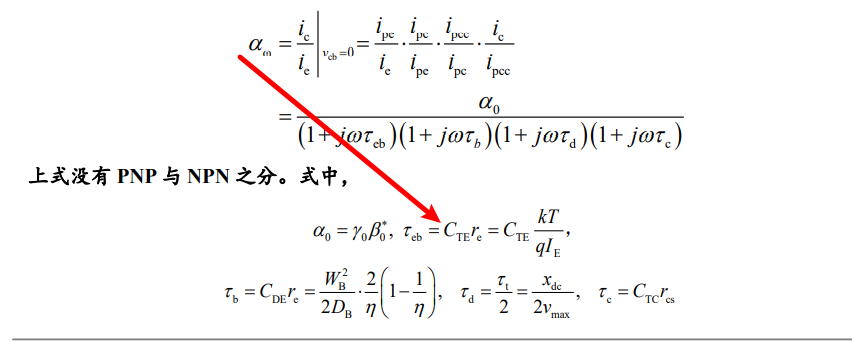

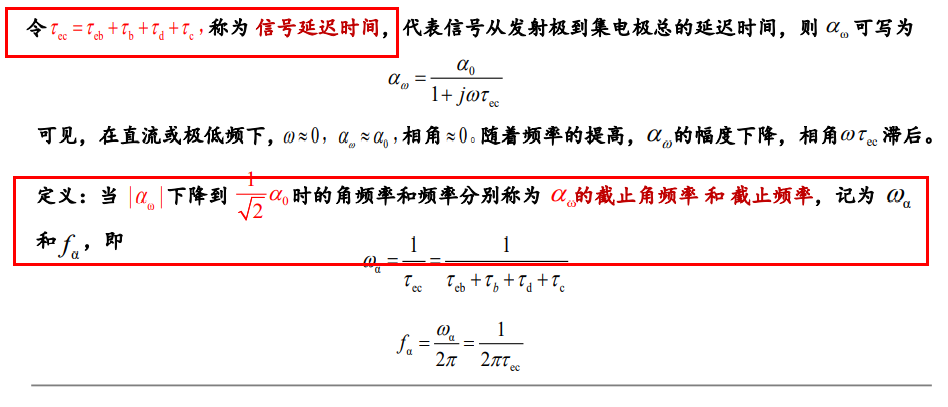

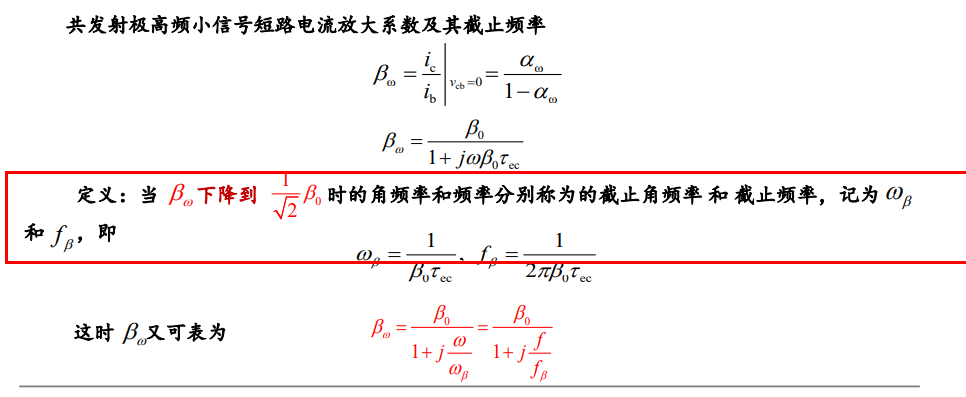

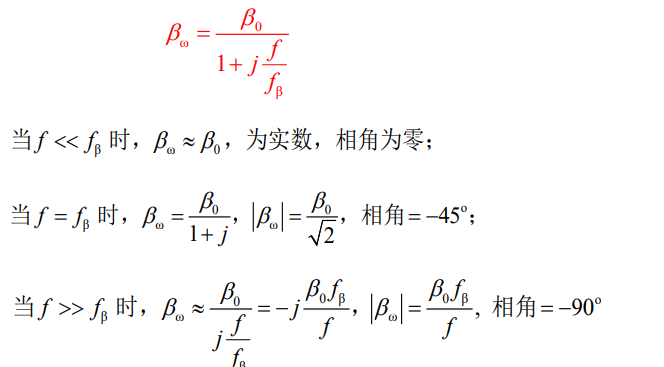

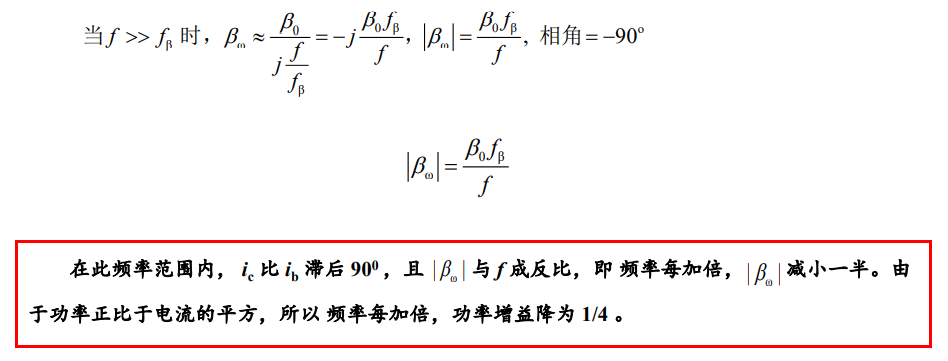

高频小信号短路电流放大系数

共基极高频小信号短路电流放大系数介质频率

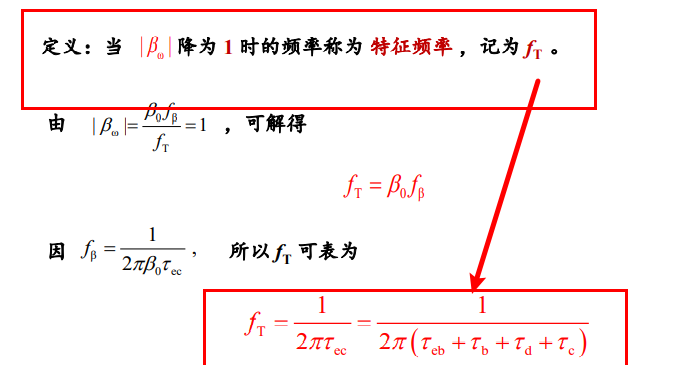

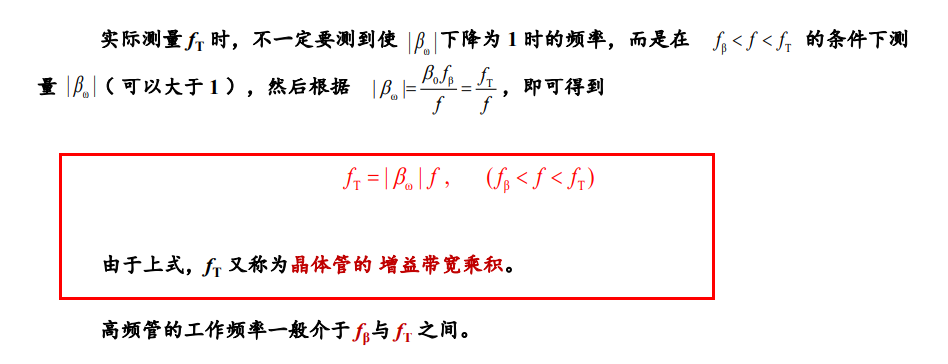

特征频率

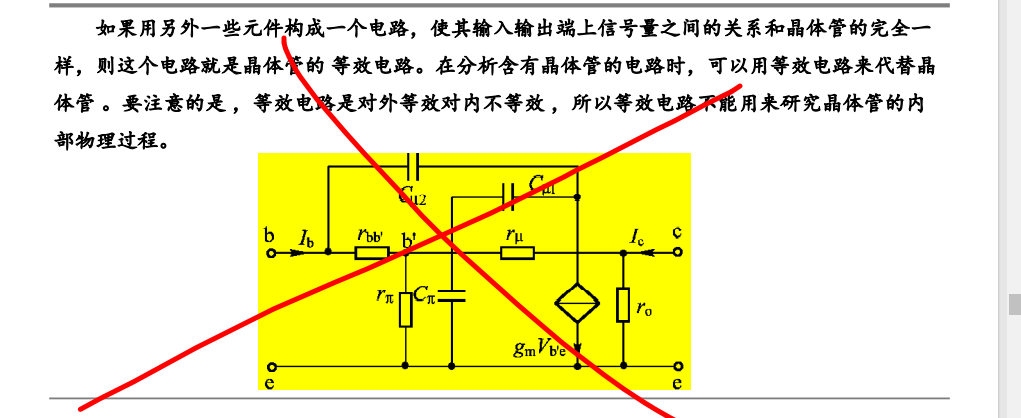

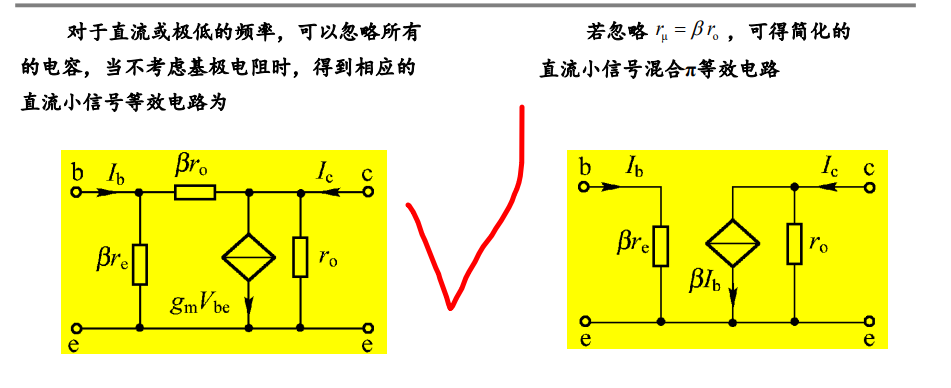

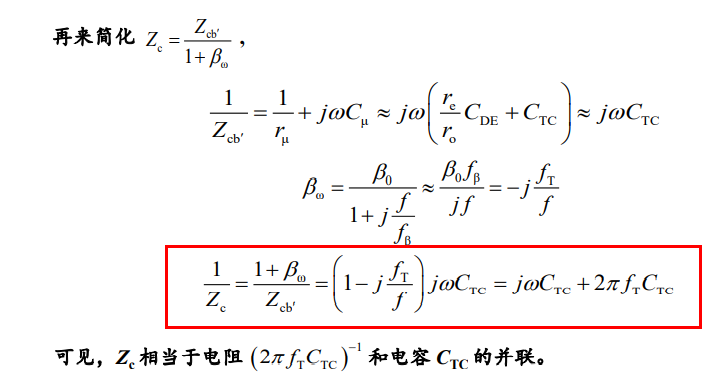

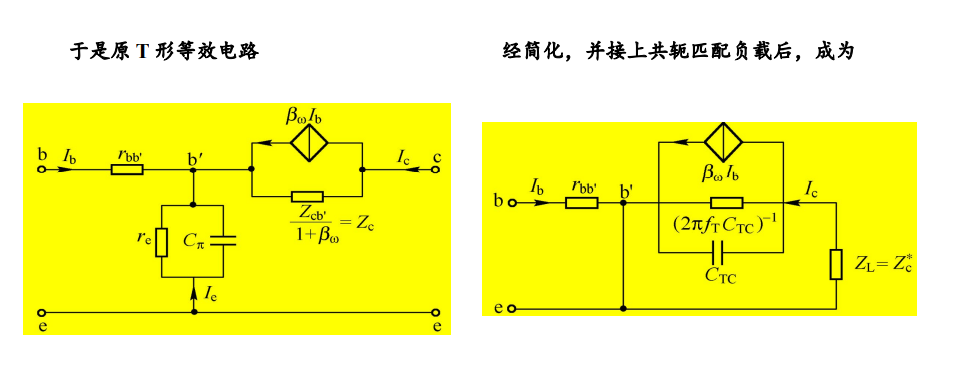

高频小信号等效电路

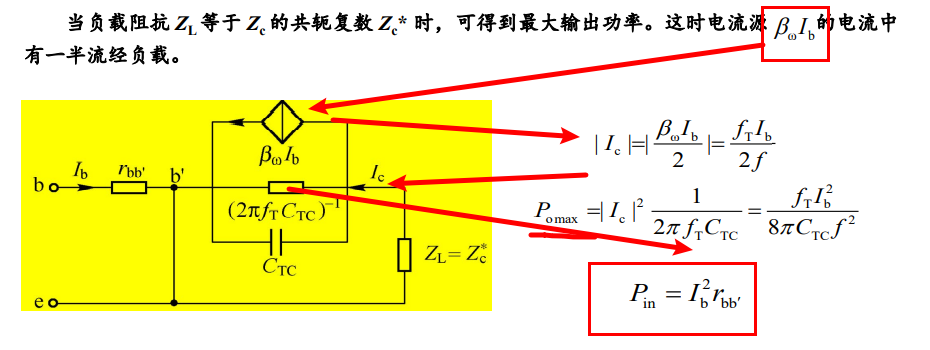

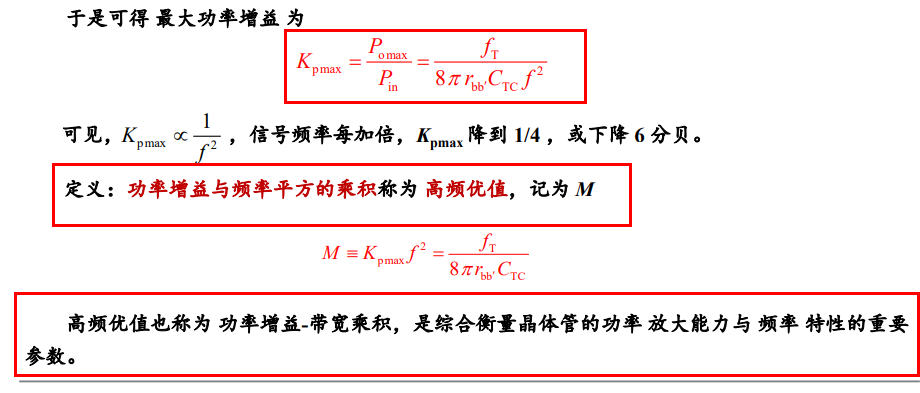

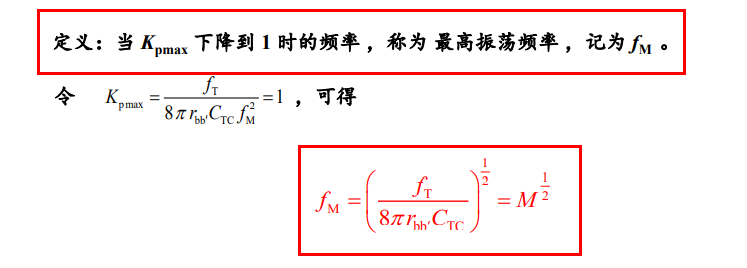

功率增益和最高振荡频率

功率增益与频率平方的乘积称为 高频优值

高频优值也称为 功率增益-带宽乘积,是综合衡量晶体管的功率 放大能力与 频率 特性的重要 参数

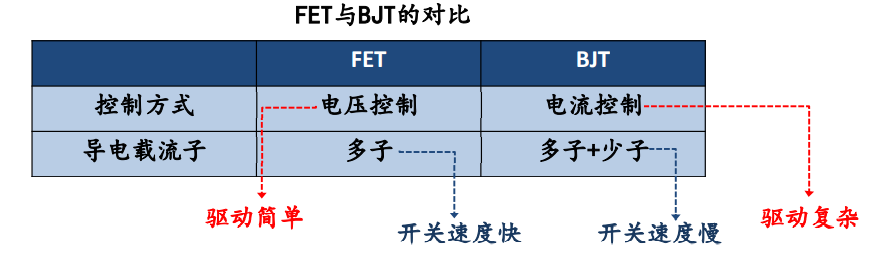

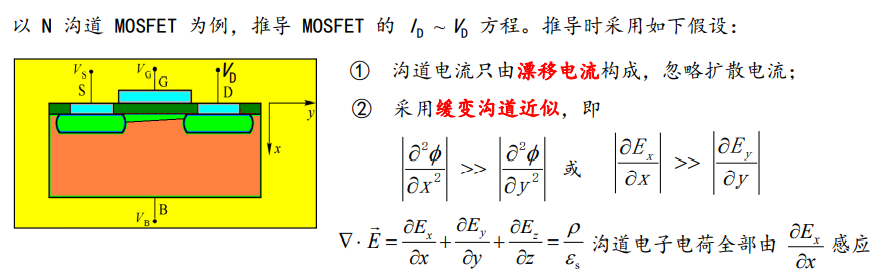

绝缘栅场效应晶体管

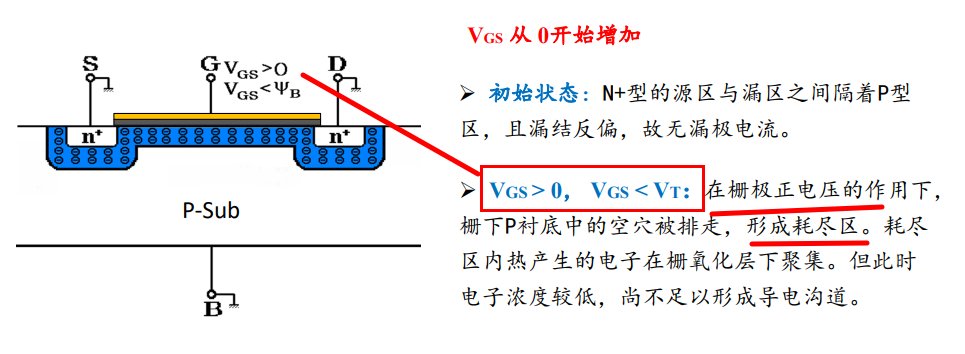

MOSFET的基本结构及工作原理

场效应晶体管(Field Effect Transistor,FET)是另一类重要的微电子器件,是 一种电压控制型多子导电器件,又称为单极型晶体管

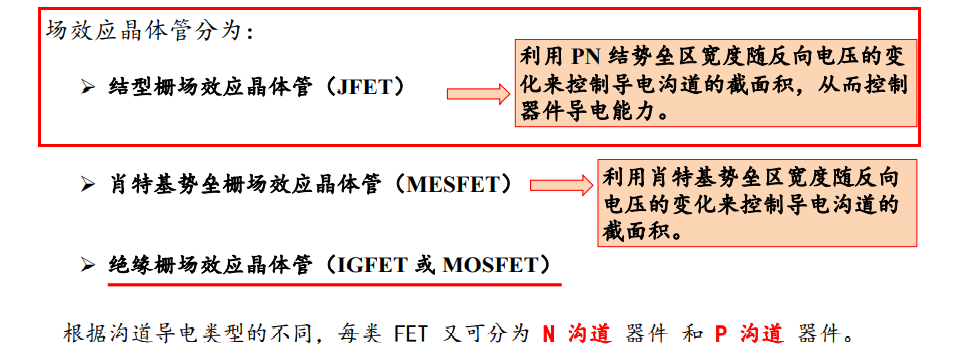

结型场效应晶体管

利用PN结势垒区宽度随反向电压变化来控制导电沟道面积,从而控制器件导电能力

肖特基势垒栅场效应晶体管

利用肖特基势垒区宽度随反向电压变化来控制导电沟道的截面积

根据沟道导电类型的不同,每类 FET 又可分为 N 沟道 器件 和 P 沟道 器件

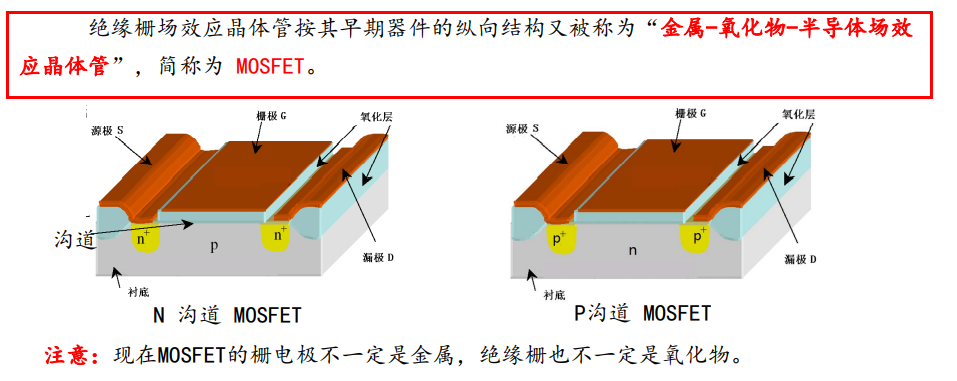

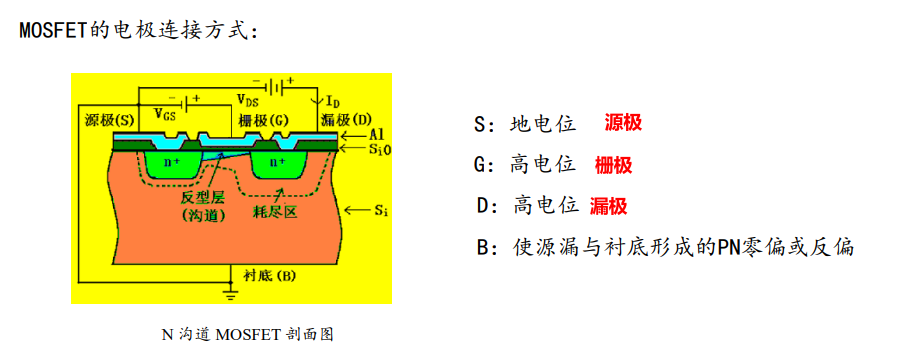

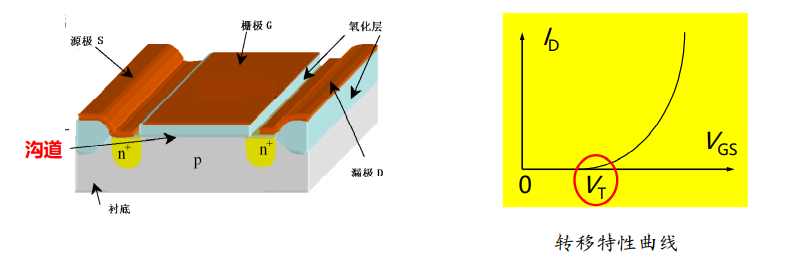

绝缘栅场效应晶体管按其早期器件的纵向结构又被称为“金属-氧化物-半导体场效 应晶体管”,简称为 MOSFET

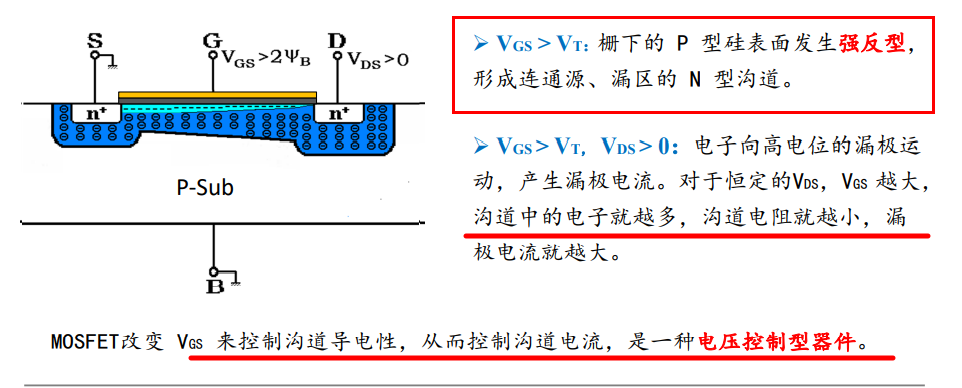

MOSFET改变 VGS 来控制沟道导电性,从而控制沟道电流,是一种电压控制型器件。

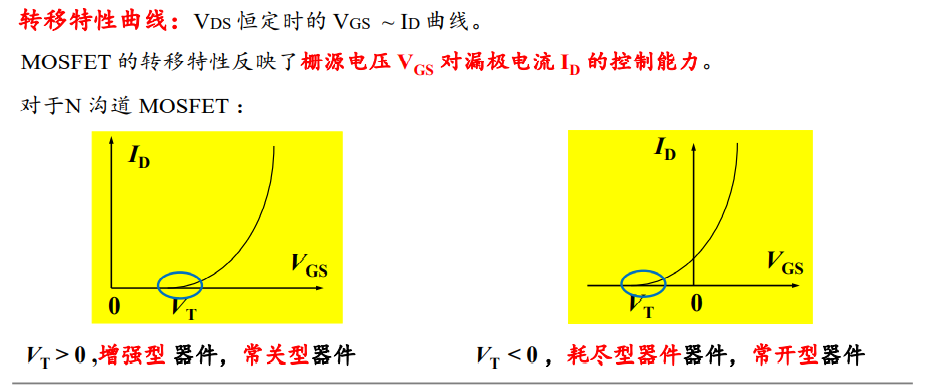

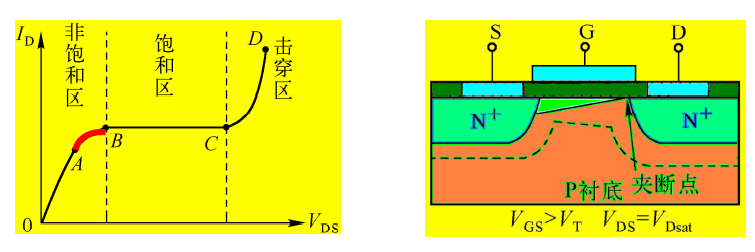

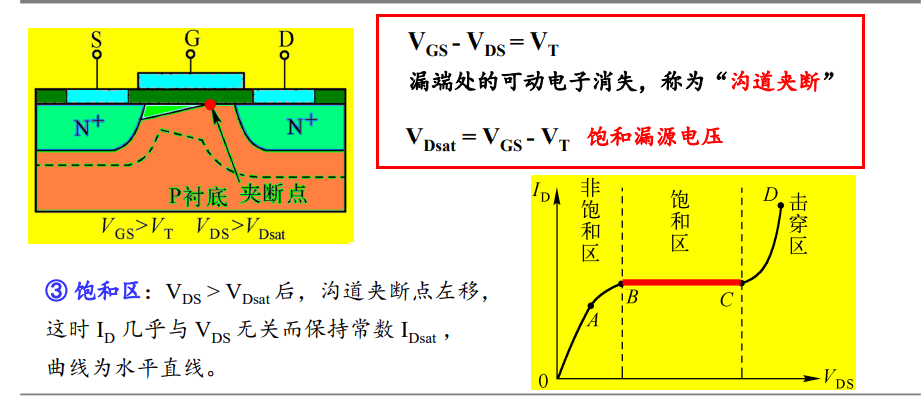

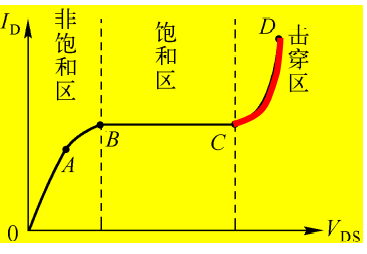

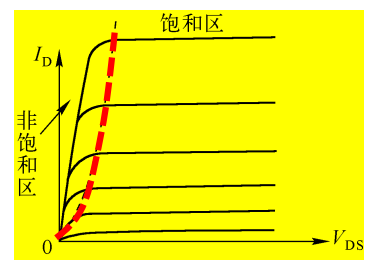

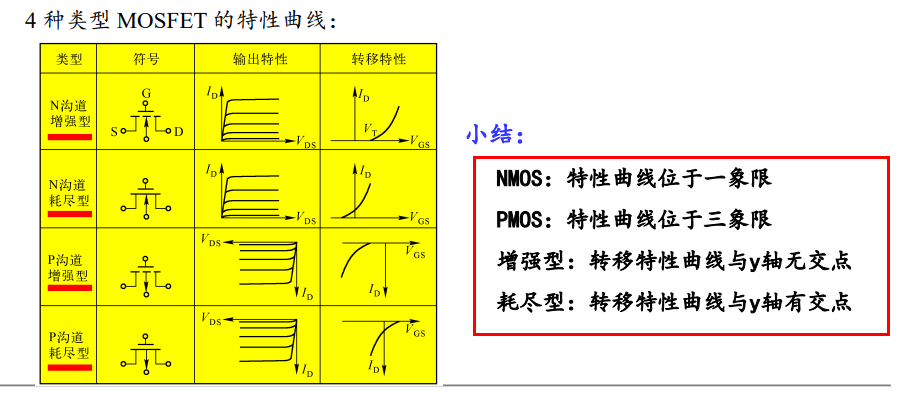

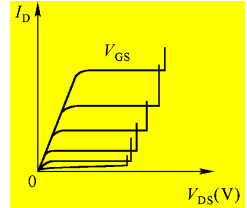

MOSFET的特性曲线和分类

MOSFET 的转移特性反映了栅源电压 VGS 对漏极电流 ID 的控制能力

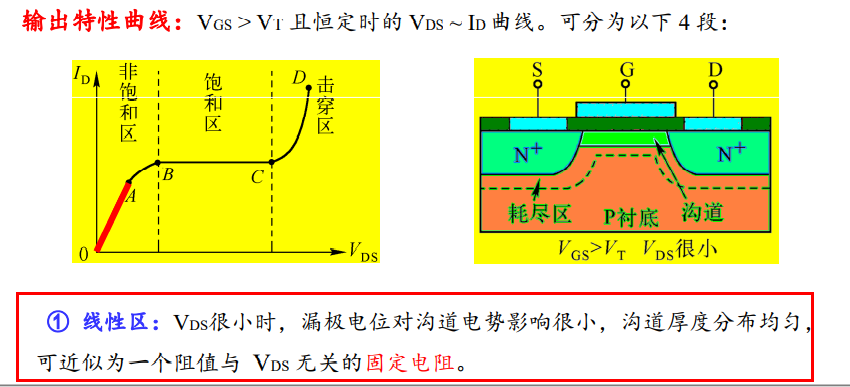

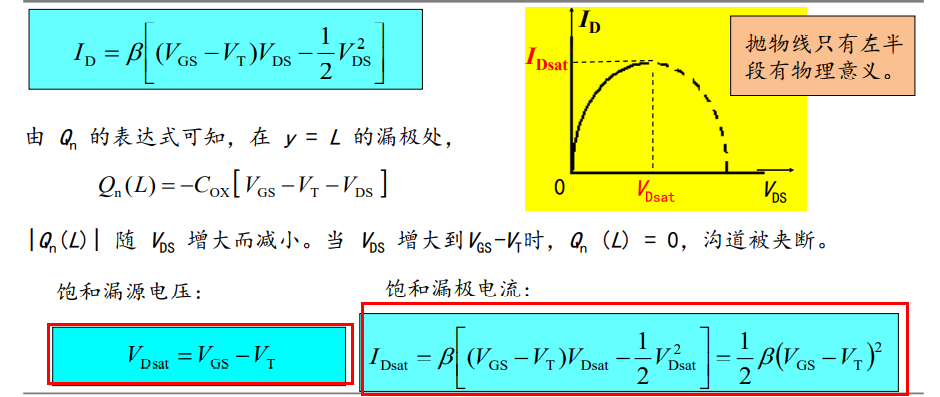

① 线性区:VDS很小时,漏极电位对沟道电势影响很小,沟道厚度分布均匀, 可近似为一个阻值与 VDS 无关的固定电阻

② 过渡区:随着 VDS 增大,漏附近沟道电势升高,栅极和沟道的电压差缩小, 衬底表面电子积累变弱,沟道电阻增大,曲线逐渐下弯

线性区与过渡区统称为 非饱和区,有时也统称为 线性区

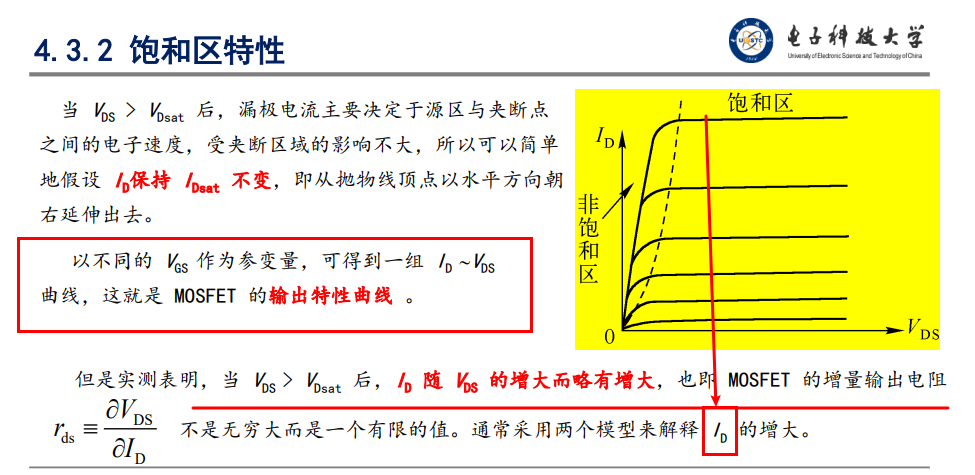

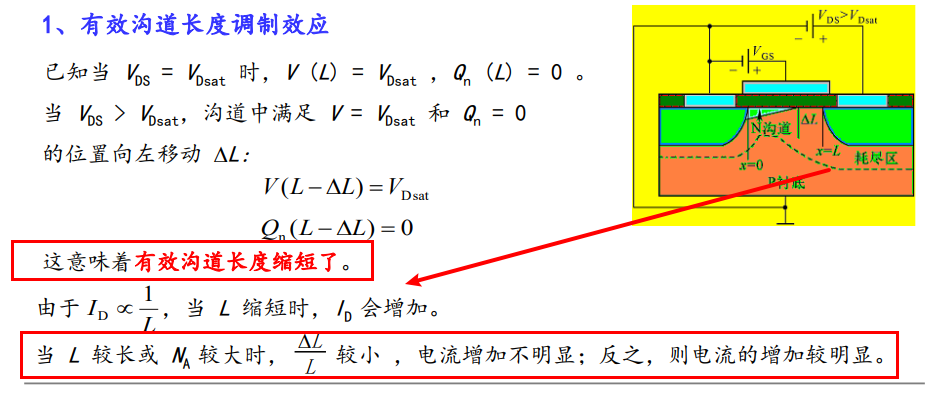

③ 饱和区:VDS > VDsat后,沟道夹断点左移, 这时 ID 几乎与 VDS 无关而保持常数 IDsat , 曲线为水平直线。

④ 击穿区:当 VDS 继续增大到 BVDS 时,漏结发生雪崩击穿,或者漏源间发生穿通, ID 急剧增大

以 VGS 作为参变量得到不同 VGS 下的 VDS ~ ID 曲线族,就是 MOSFET的输出特性曲线

将各条曲线的夹断点用虚线连接起来,虚线左侧为非饱和区,虚线右侧为饱和区

- P沟道MOSFET特性与N沟道MOSFET相对称

- 衬底是N型,源漏区是P+型

- VGS 、VDS 的极性以及ID的方向均与N沟道相反

- 沟道中可动载流子空穴

- VT < 0 时称为增强型(常关型),VT > 0 时称为耗尽型(常开型)

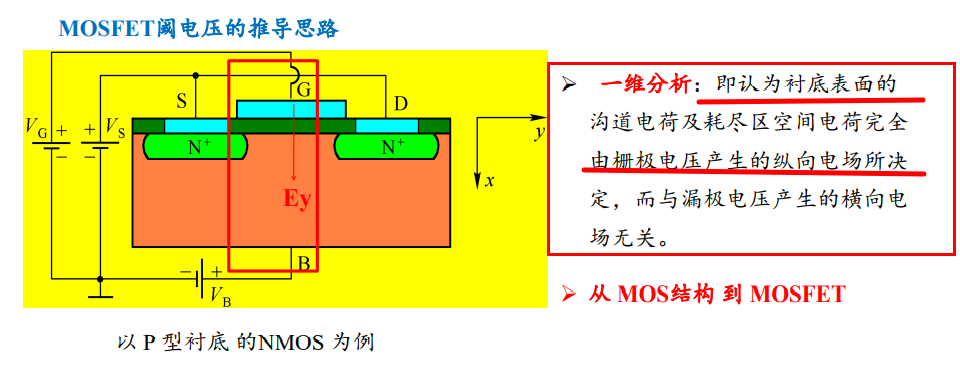

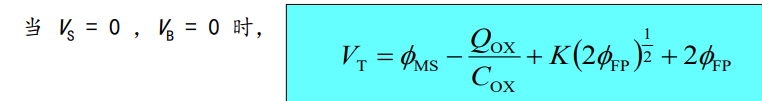

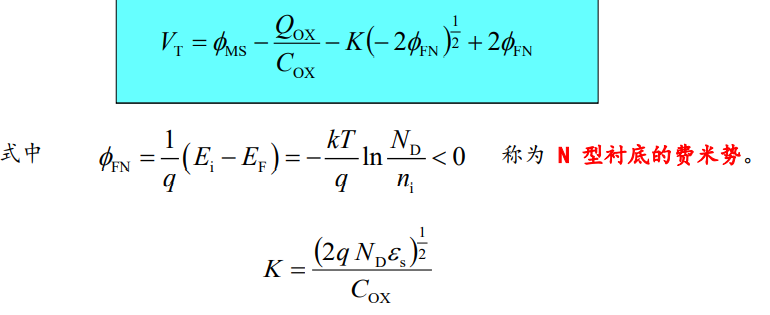

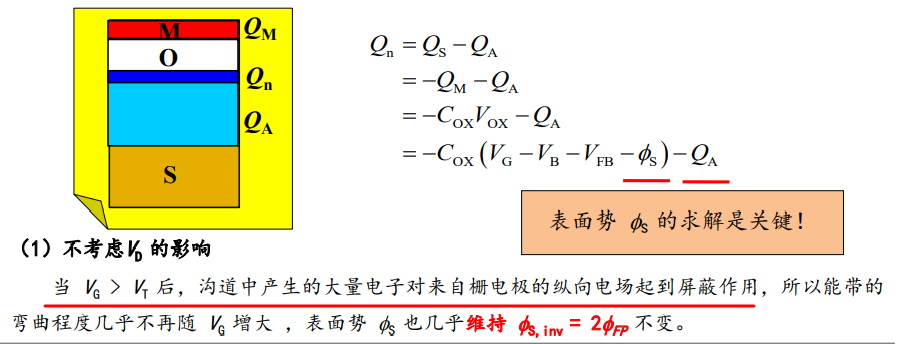

MOS结构的阈电压

阈电压:使栅下的硅表面处开始发生强反型时的栅压称为阈电压(或开启电压),记为 VT

强反型:当硅表面处的少子浓度达到或超过体内平衡多子浓度时,称表面发生了 强反型

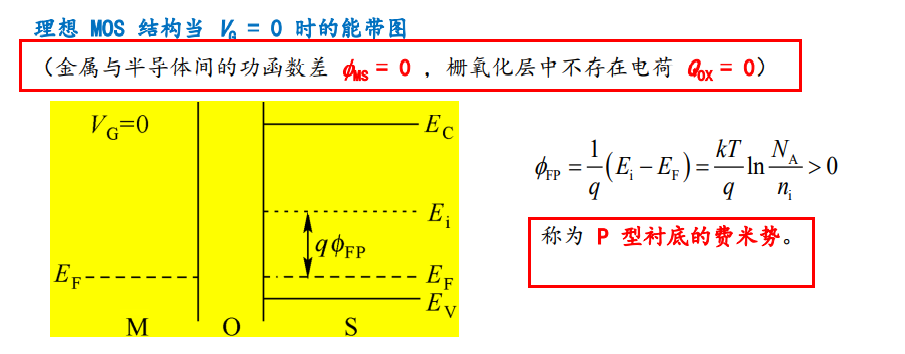

理想 MOS 结构当 VG = 0 时的能带图

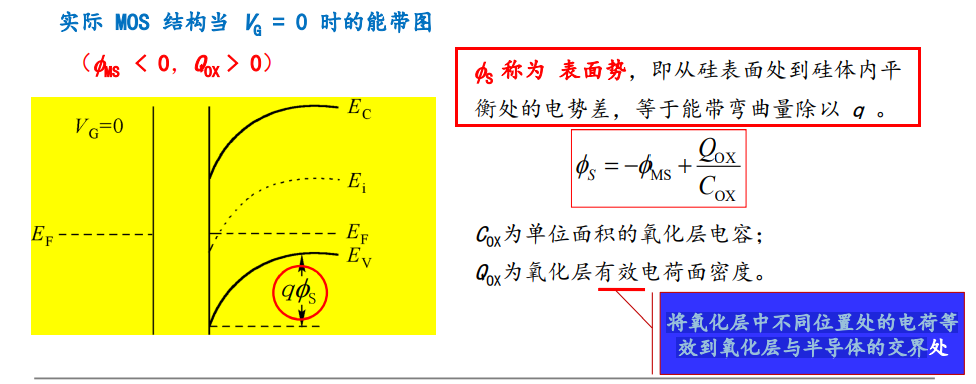

实际 MOS 结构当 VG = 0 时的能带图

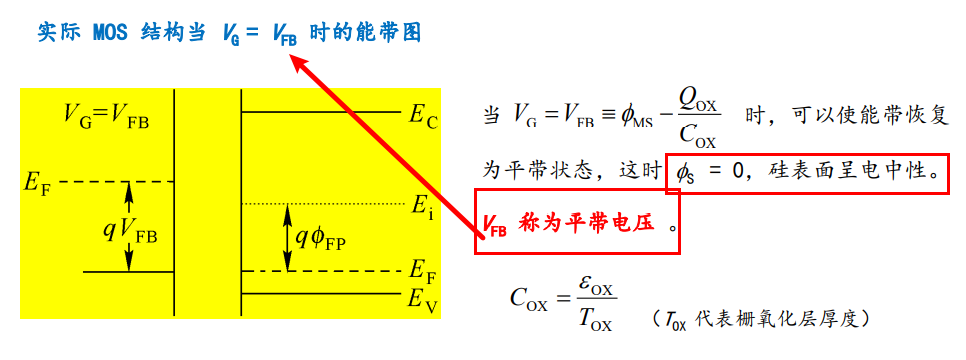

实际 MOS 结构当 VG = VFB 时的能带图

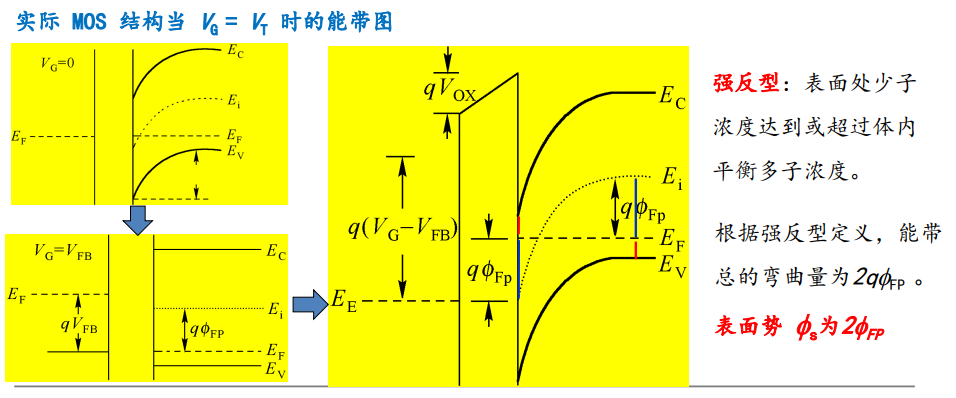

实际 MOS 结构当 VG = VT 时的能带图

强反型:表面处少子 浓度达到或超过体内 平衡多子浓度

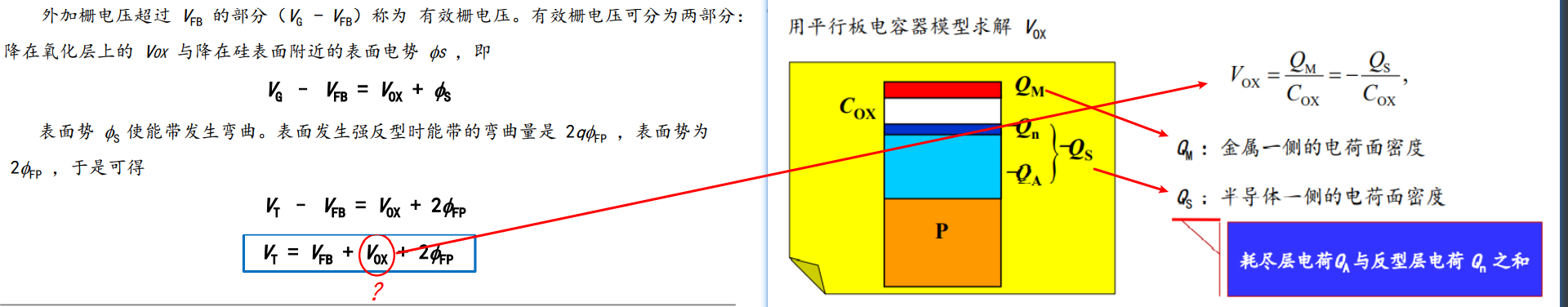

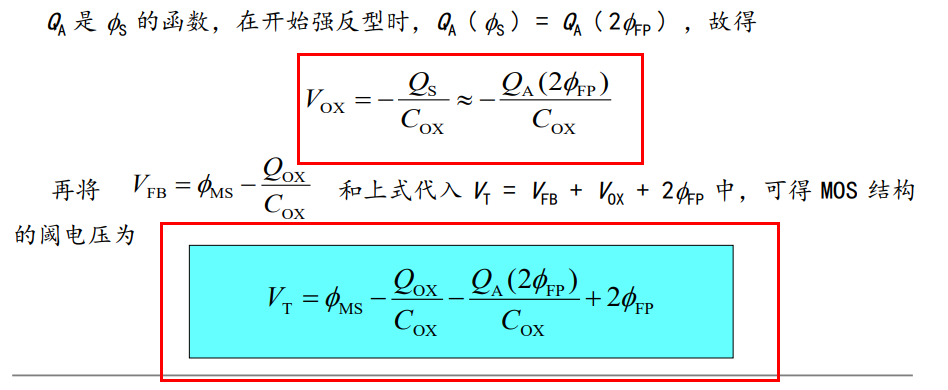

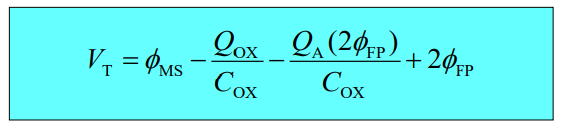

MOS 结构 的阈电压

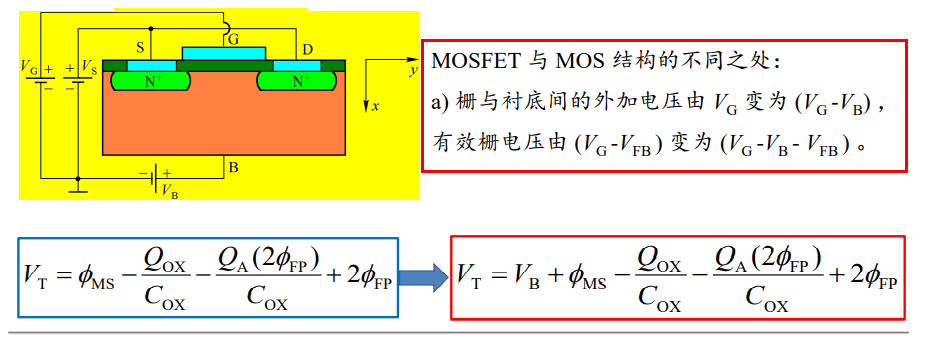

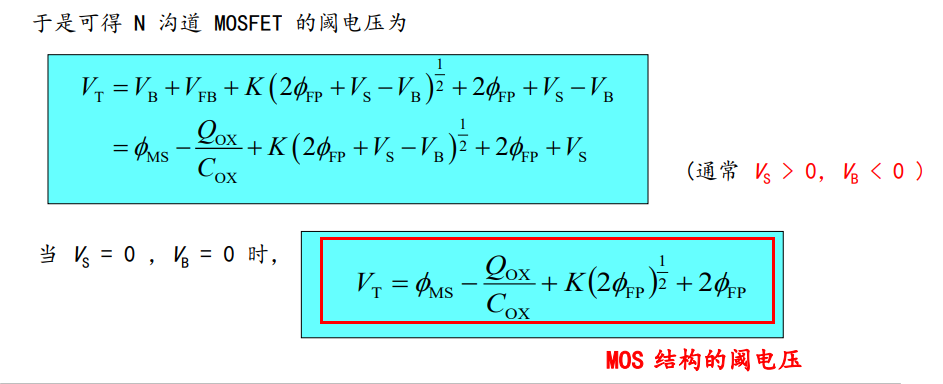

MOSFET的阈电压

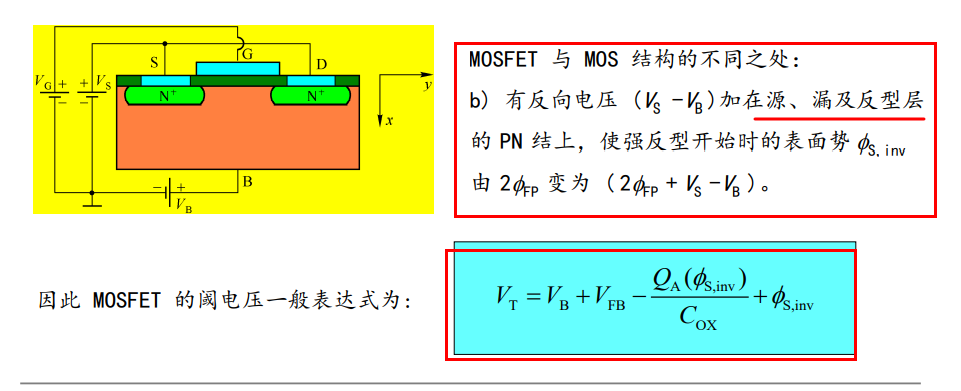

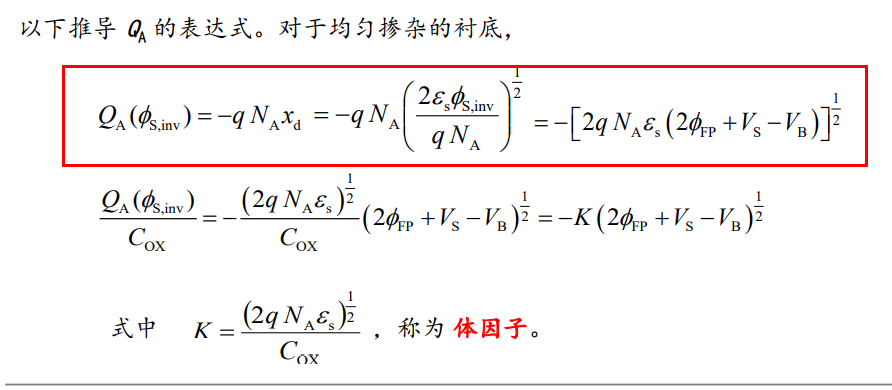

阈电压一般表达式的导出

MOS 结构的阈电压

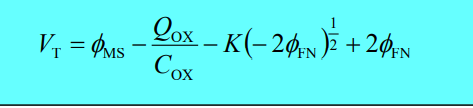

同理,P 沟道 MOSFET 当 VS = 0 ,VB = 0 时的阈电压为

影响阈电压的主要因素

- 栅氧化层厚度

- 一般来说,当 TOX 减薄时, |VT| 将减小

- 衬底费米势

- φFB 与衬底掺杂浓度有关,但受掺杂浓度的影响并不大

- 耗尽区电离杂质电荷面密度 QAD

- QAD与衬底掺杂浓度相关

- 功函数差φMS

栅氧化层中的电荷面密度 QOX

QOX 与制造工艺及晶向有关。MOSFET一般采用(100)晶面,并在工艺中尽量减小 QOX 。

调整阈电压主要通过改变掺杂浓度(例如离子注入)和改变栅氧化层厚度TOX 来实现。

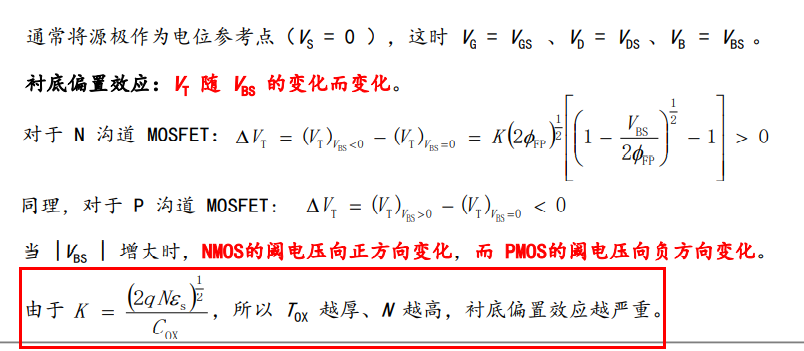

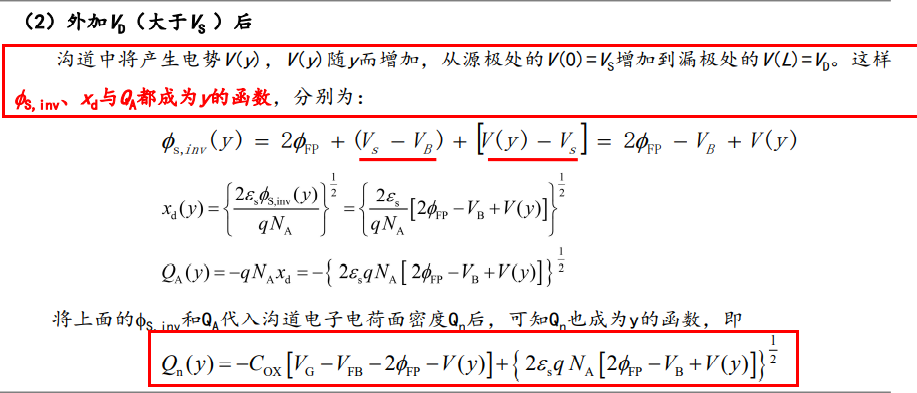

衬底偏置效应(体效应)

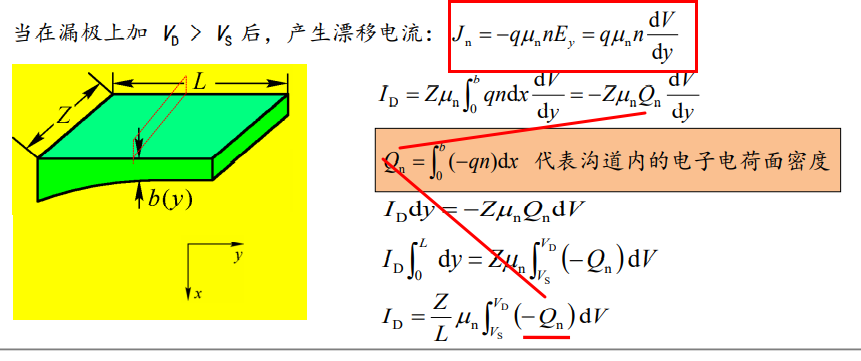

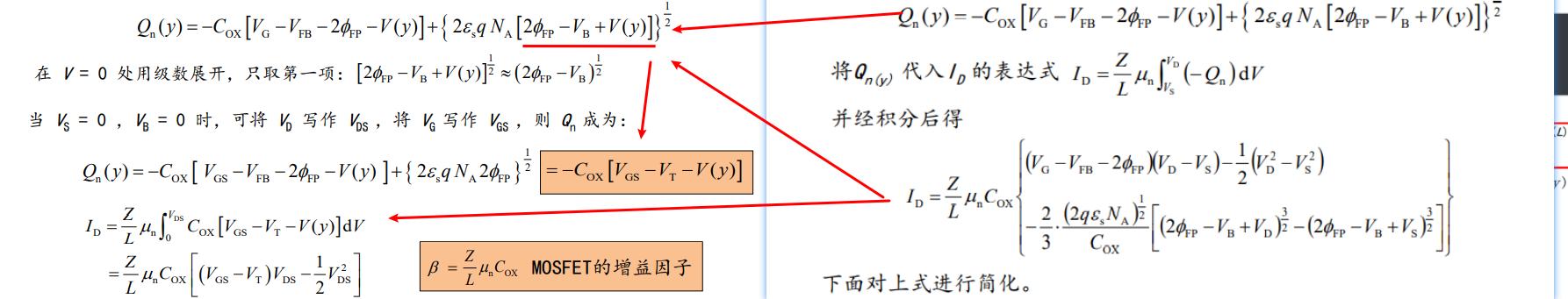

非饱和区直流电流电压方程

-

沟道内的载流子(电子)迁移率为常数

-

强反型近似,即认为当表面少子浓度达到体内平衡多子浓度时沟道开始导电

-

QOX 为常数,与能带的弯曲程度无关

漏极电流的一般表达式

沟道电子电荷面密度 Qn

外加VD(大于VS )后

漏极电流的精确表达式

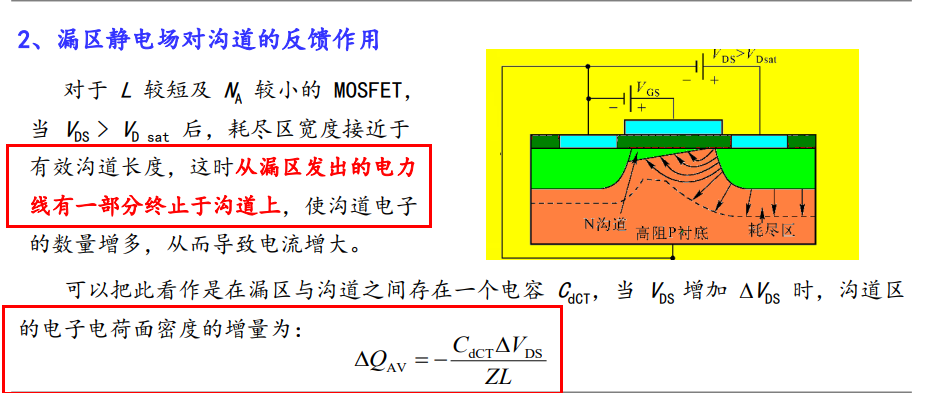

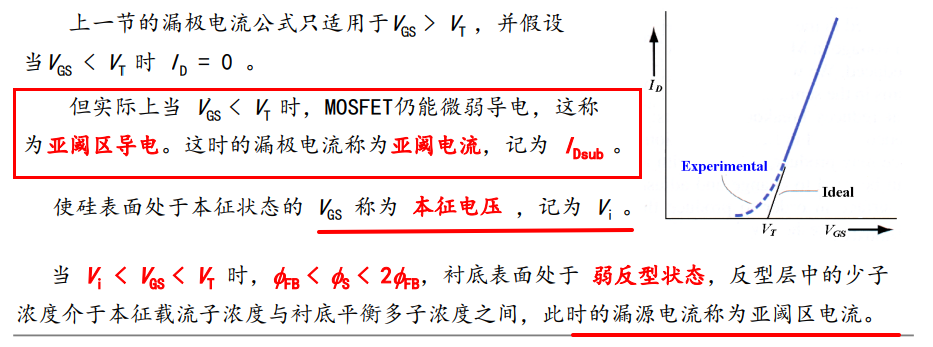

MOSFET的亚阈区导电

亚阈区的定义

但实际上当 VGS < VT 时,MOSFET仍能微弱导电,这称 为亚阈区导电。这时的漏极电流称为亚阈电流

MOSFET的亚阈区特性

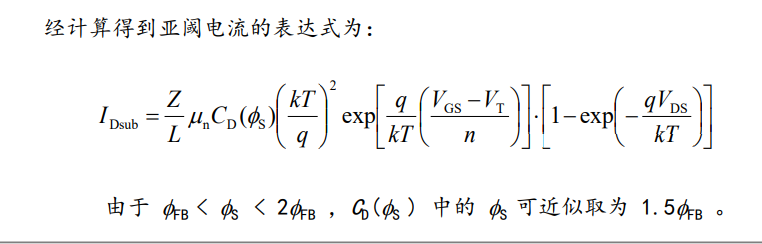

在亚阈区,表面弱反型层中的电子浓度较小,所以漂移电流很小;但电子的浓度 梯度却很大,所以扩散电流较大。因此在计算IDsub 时只考虑扩散电流而忽略漂移电流

亚阈区栅源电压摆幅 S

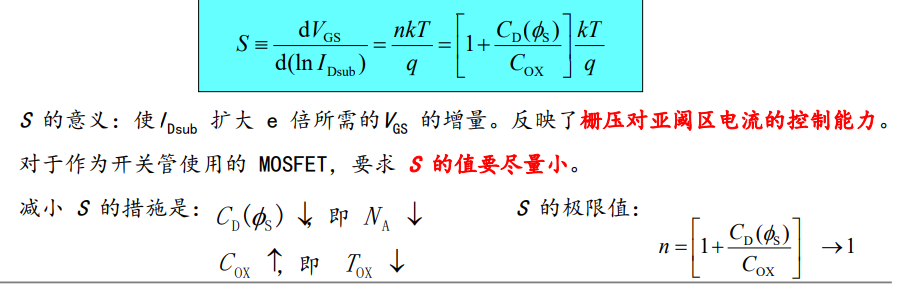

定义:亚阈区的转移特性半对数斜率的倒数称为亚阈区栅源电压摆幅,记为 S

S 的意义:使IDsub 扩大 e 倍所需的VGS 的增量。反映了栅压对亚阈区电流的控制能力 对于作为开关管使用的 MOSFET,要求 S 的值要尽量小

MOSFET的直流参数及击穿电压

阈电压 VT

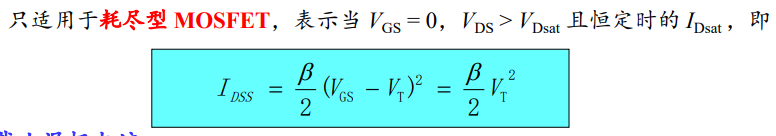

饱和漏极电流 IDSS

截止漏极电流

只适用于增强型 MOSFET,表示当 VGS = 0 ,外加 VDS 后的亚阈电流与 PN 结反 向电流引起的微小电流

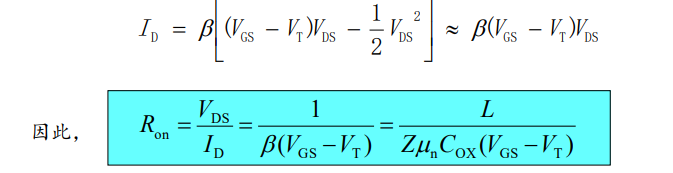

通导电阻 Ron

表示当 MOSFET 工作于线性区,且 VDS 很小时的沟道电阻。当 VDS 很小时,ID 可表示为

栅极电流 IG

表示从栅极穿过栅氧化层到沟道之间的电流。栅极直流电流IG 极小,通常小于 10-14 A

MOSFET的击穿电压

漏源击穿电压BVDS

漏 PN 结雪崩击穿

由于在漏、栅之间存在 附加电场,使栅极下面漏PN结 耗尽区内的电场增大,因此 MOSFET 的漏源击穿电压远低 于相同掺杂和结深的 PN 结雪崩击穿电压。 当衬底掺杂浓度小于 1016 cm-3 后,BVDS就主要取决于 VGS 的极性、大小和栅氧化层的厚度 TOX

随着栅极电压的增加,由漏PN结耗尽区指向栅极的电力线将减少,电场集中得到缓解,漏 源击穿电压将增大

源、漏之间的穿通

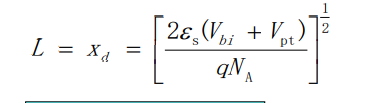

漏PN结尚未发生雪崩击穿,但是耗尽区已经扩展到源区,称为源漏穿通,此时也会 出现大的漏极电流。设沟道长度等于漏PN结耗尽区宽度

栅源击穿电压BVGS

BVGS 是使栅氧化层发生击穿时的 VGS

BVGS 大致正比于栅氧化层厚度 TOX ,当 TOX = 150 nm 时 ,BVGS 约为 75 ~ 150 V 。 但实际上由于氧化层的缺陷与不均匀 ,应至少加 50% 的安全系数由于 MOS 电容上存贮的电荷不易泄放,且电容的值很小,故很少的电荷即可导 致很高的电压,使栅氧化层被击穿。由于这种击穿是破坏性的 ,所以 MOSFET 在存 放与测试时,一定要注意使栅极良好地接地

MOSFET的温度特性

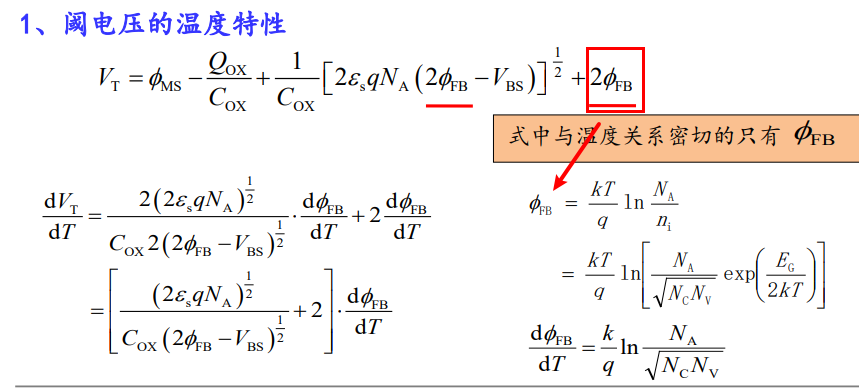

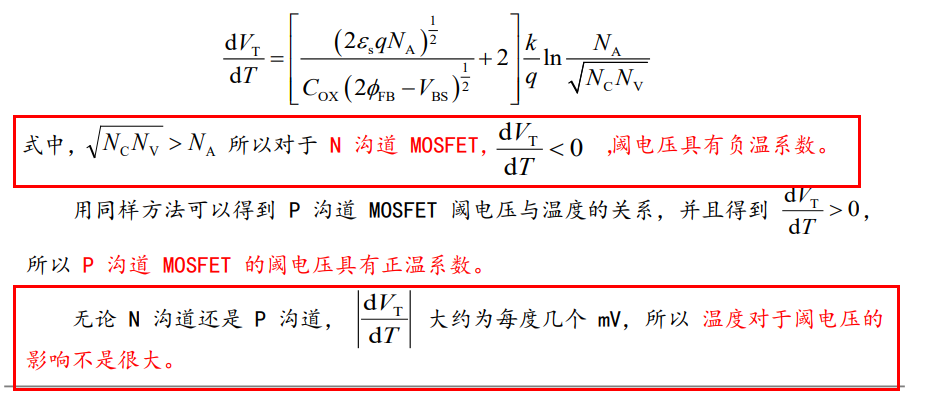

阈电压的温度特性

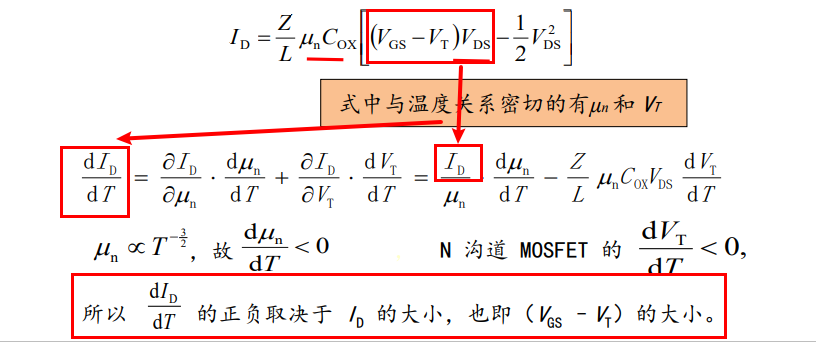

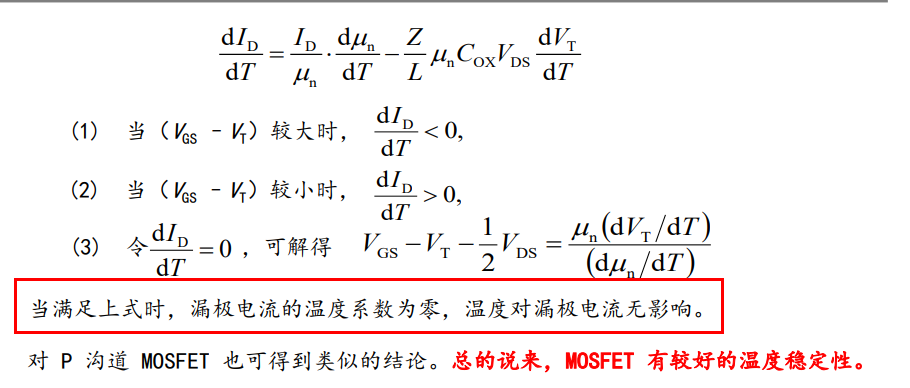

漏极电流与温度的关系

总的说来,MOSFET 有较好的温度稳定性

MOSFET的小信号交流参数

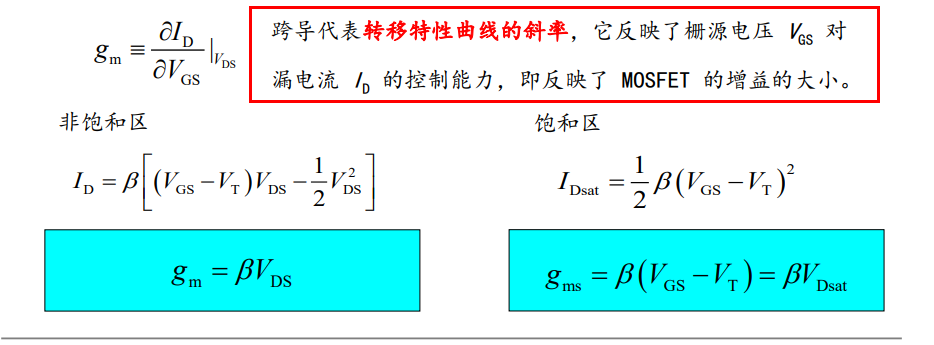

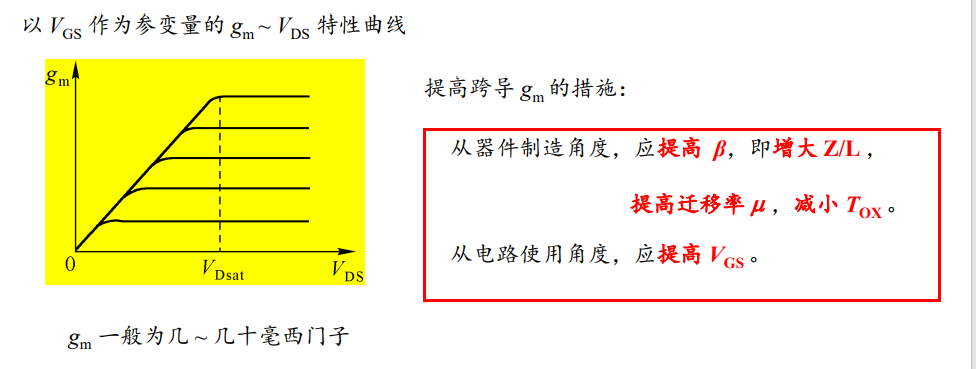

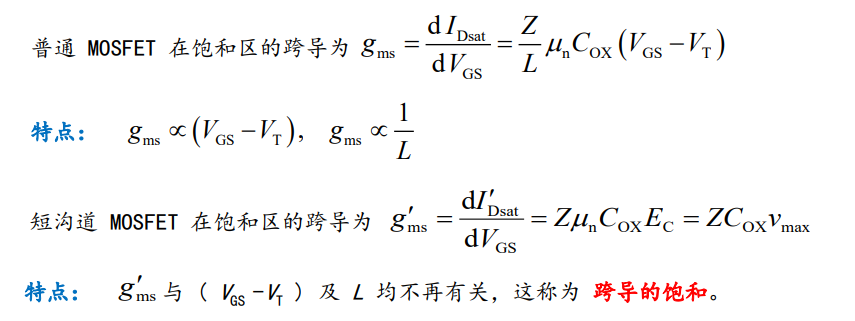

跨导

跨导代表转移特性曲线的斜率

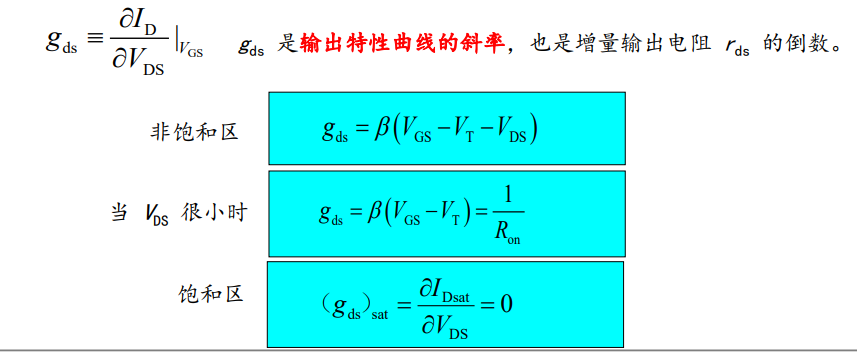

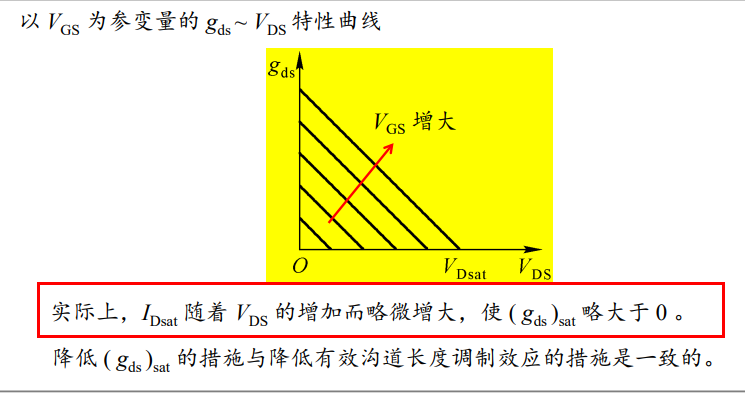

漏源电导 gds

是输出特性曲线的斜率

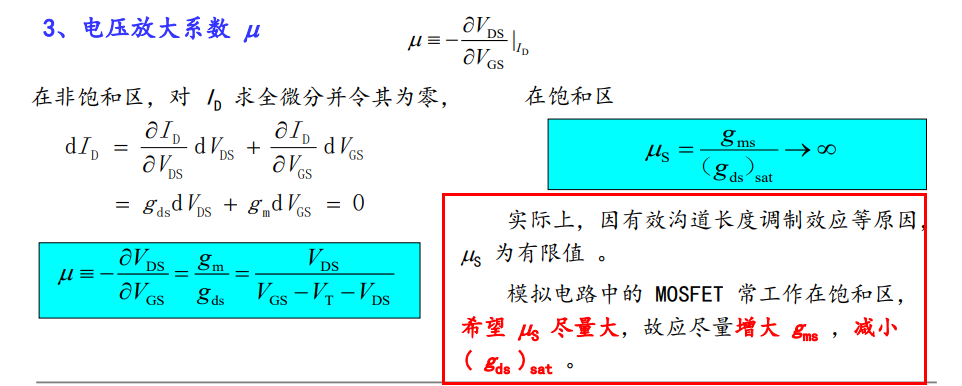

电压放大系数 µ

小尺寸效应

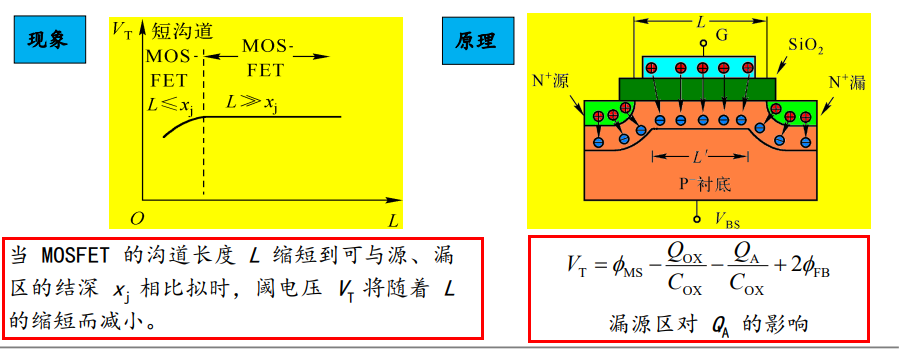

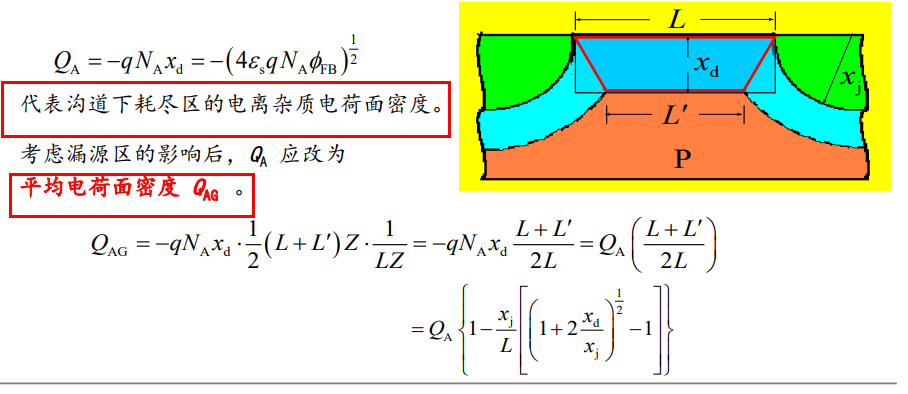

阈电压的短沟道效应

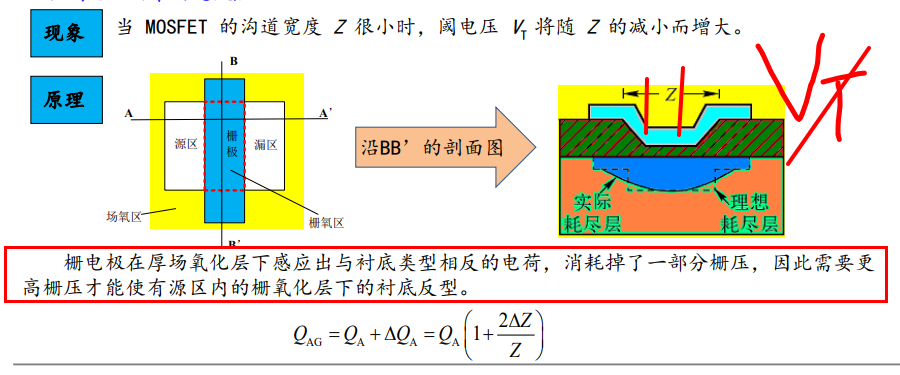

阈电压的窄沟道效应

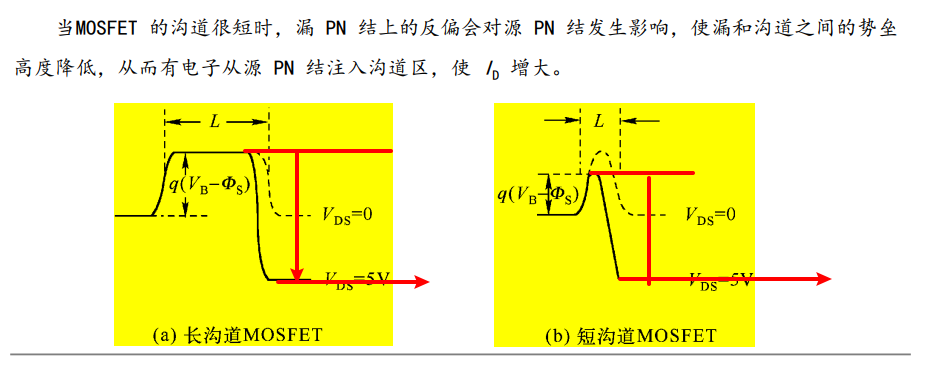

漏诱生势垒降低效应

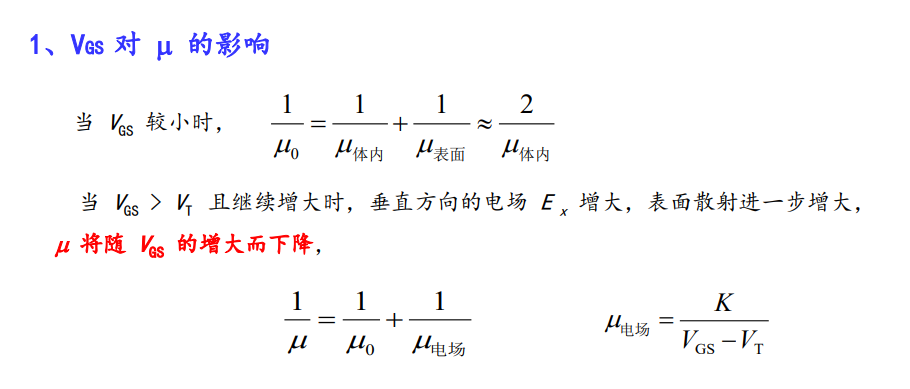

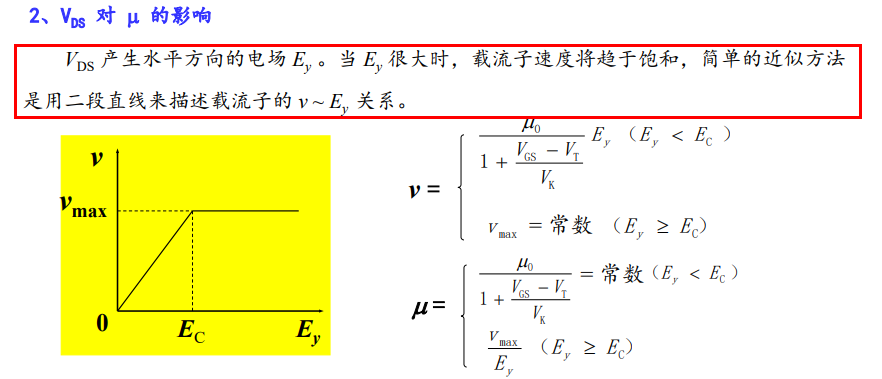

迁移率调制效应

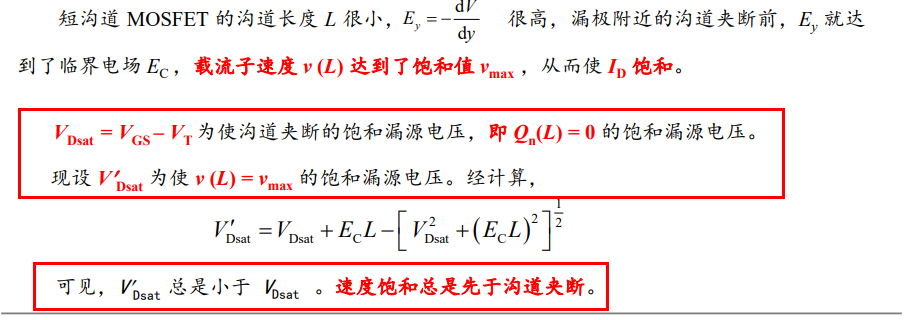

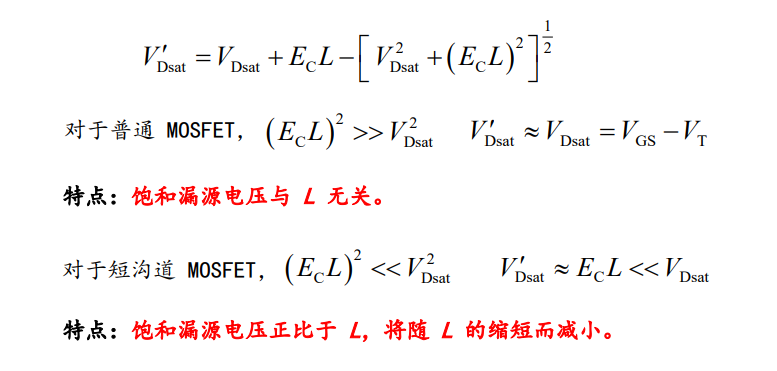

速度饱和对饱和漏源电压的影响

特点:饱和漏源电压与 L 无关

特点:饱和漏源电压正比于 L,将随 L 的缩短而减小

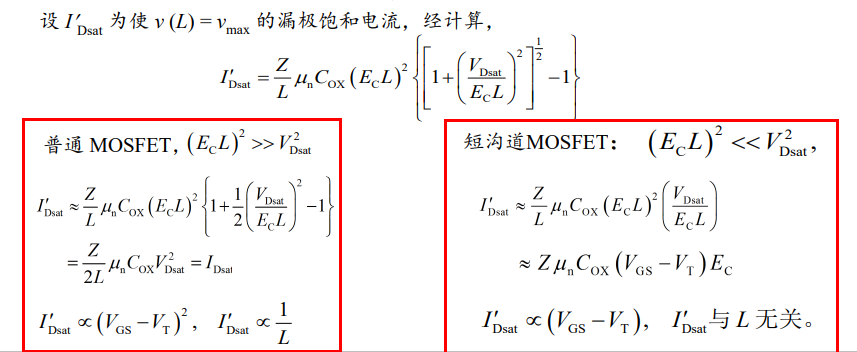

速度饱和对饱和漏极电流的影响

速度饱和对跨导的影响

强电场效应

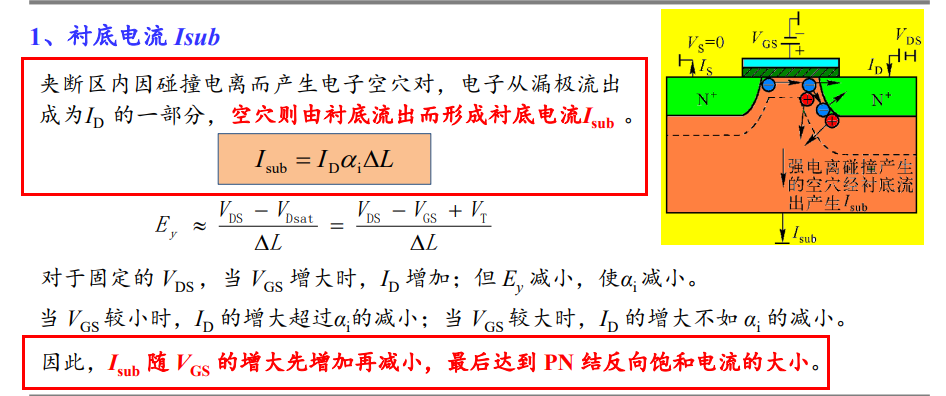

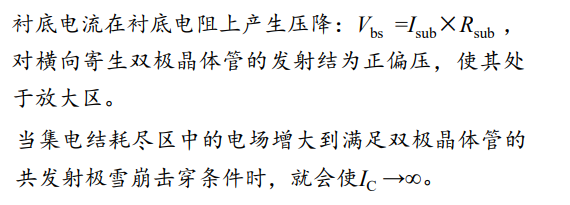

衬底电流 Isub

夹断区内因碰撞电离而产生电子空穴对,电子从漏极流出 成为ID 的一部分,空穴则由衬底流出而形成衬底电流Isub 。

击穿特性

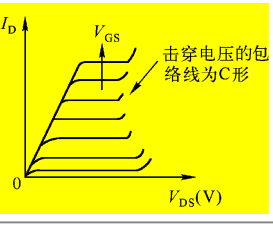

第一类击穿:正常雪崩击穿

BVDS 随VGS 的增大而增大,且是硬击穿。 主要发生在 P 沟道 MOSFET(包括短沟道) 与长沟道 N 沟道 MOSFET 中

第二类击穿:横向双极击穿

BVDS 随 VGS 的增大先减小再增大,其包络线 为 C 形,并且是软击穿,主要发生在 N 沟道短 沟道 MOSFET 中

横向双极击穿产生原因

为什么击穿曲线具有C形包络?

Isub 随 VGS 的增大先增加再减小

为什么 N 沟道 MOSFET 更容易发生横向双极击穿

N沟道MOSFET的Isub 随更大,衬底电阻更大

热电子效应

热电子:沟道中漏附近能量较大的电子

特点:热电子若具有克服Si ~ SiO2间势垒 ( 约 3.1 eV ) 的能量,就能进入栅氧化层。这些 电子中的一部分从栅极流出构成栅极电流 IG ,其余部分则陷在 SiO2的电子陷阱中

影响:陷在 SiO2中的电子随时间积累,长时期后将对 MOSFET 的性能产生影响。

- (a) VT 向正方向漂移,即 VT 随时间而逐渐增大

- (b) 因迁移率下降而导致跨导 gm 的退化

- (c) 因界面态密度增大而导致亚阈电流 IDsub 的增大

MOSFET的发展方向

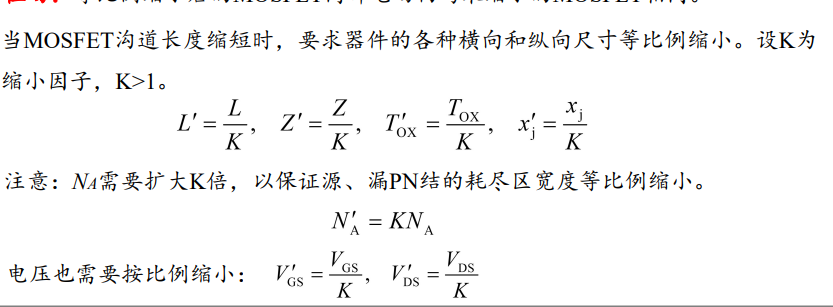

MOSFET的发展趋势是沟道长度不断缩短,因 为能够获得集成电路性能和集成度的提高。这种发 展趋势可以用摩尔定律来描述:MOS集成电路的 集成度每18个月翻一番,最小线宽每6年下降一半。 目前的最小线宽已达到14nm。 因此,MOSFET的发展过程,就是在不断缩短沟道长度的同时,尽量设法消除或削 弱短沟道效应的过程。 MOSFET的沟道长度缩短采用按比例缩小法则。 但是,沟道长度的缩短可能带来短沟道效应。为了消除或削弱短沟道效应,新结构 MOSFET 不断被提出,如 FinFET 等

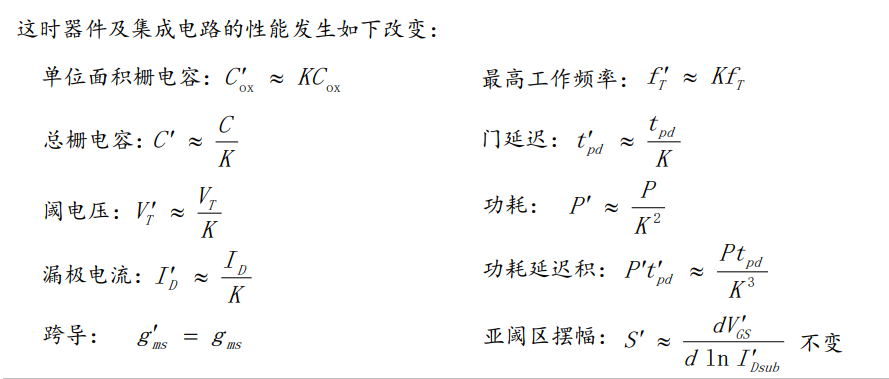

恒场按比例缩小法则

恒场:等比例缩小后的MOSFET内部电场仍与未缩小的MOSFET相同

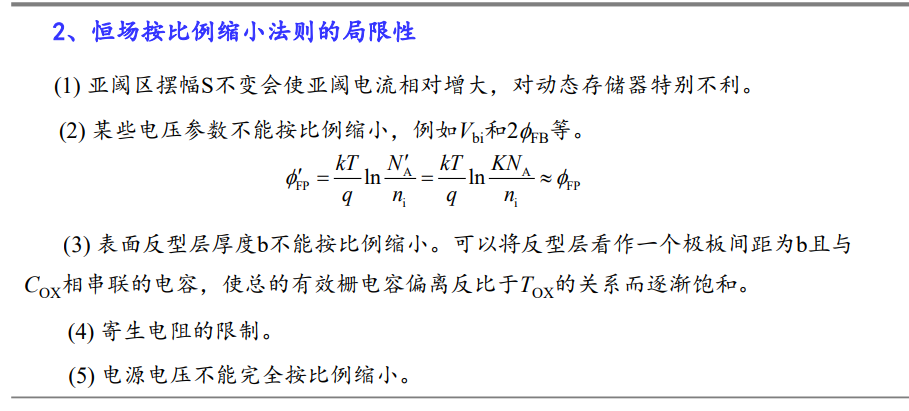

恒场按比例缩小法则的局限性

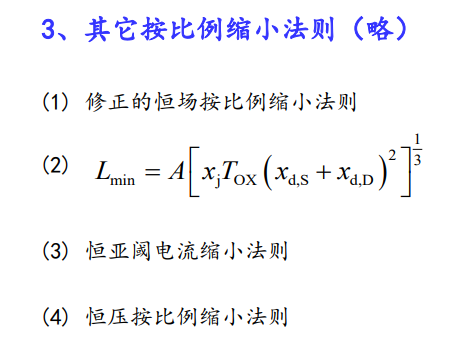

其它按比例缩小法则