GPIO8种方式小总结

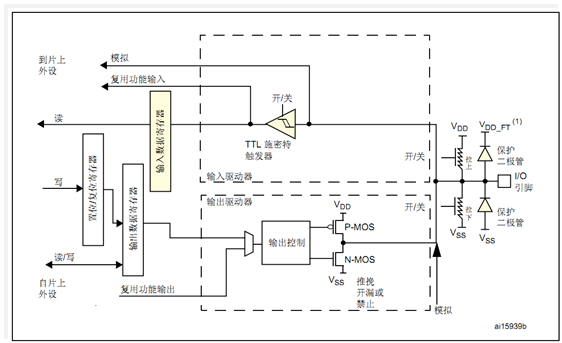

在输出3时写1时上反向为0,下为1,1时MOS不接通,0接通

为1时上导通输出高电平1;

为0时下导通输出低电平0;

VDD为逻辑电源正

VSS为逻辑地

若为输出状态则施密特触发器总为开

然后经过上拉下拉电阻输出高低电平,此时施密特总为开;

若施密特开则总为读

推挽输出与开漏输出不同之处在于推挽输出两个MOS都用,而开漏输出则是只能选择是否用下面的,若为高电平则下面的P-MOS截止,路不通默认由上拉电阻拉高

复用与不复用区别在于从哪里输出

若为开漏输出则只可以输出强低电平,若为推挽输出则强高低电平都可以输出

输入上拉,输入下拉,及浮空状态施密特触发器都为开,而模拟输入为关

输入上拉默认为高电平,下拉为低电平。

可能有错,以后改正