汇编学习笔记(1) -- 计算机简单结构与寄存器

计算机简单结构

存储器

指内存

存储器被划分成若干个存储单元,每个存储单元从0开始编号

一个存储单元可以存储8bit(比特,b,一个二进制位),即存储1byte(字节,B)

1byte=8bit

1KB=1024B(byte)

1MB=1024KB...

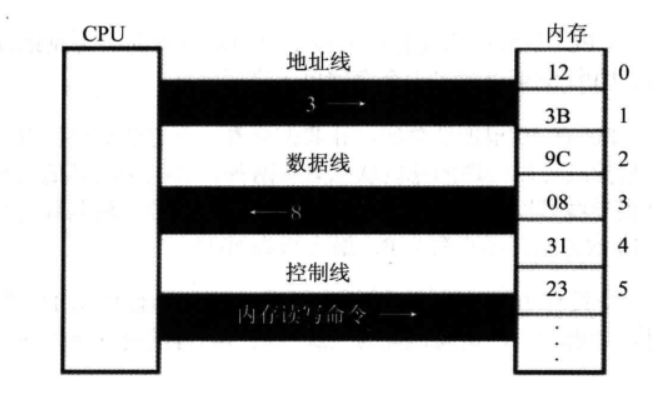

cpu要从内存中读取数据,得进行3类信息的交互:

存储单元的地址(地址信息);

器件的选择,读或写的命令(控制信息);

读或写的数据(数据信息)。

数据通过总线传输,总线逻辑上分为:地址总线,控制总线和数据总线

cpu从3号单元读取数据过程

1.cpu通过地址线将地址信息3发出

2.cpu通过控制线发出内存读命令,选中芯片并通知

3.存储器将3号单元中的数据8通过数据线送入cpu

地址总线

地址总线传输信息决定了cpu对存储单元的寻址能力

一根地址总线只能传输1个二进制数据

设有十根地址总线,则一次传输10个二进制数据,而10个二进制可以组合成2^10个(0~1023)

N根地址总线可以让cpu最多可以寻找2^N个内存单元

数据总线

数据总线的宽度决定了cpu数据交互的速度

8根总线传输8二进制数(bit)即一个字节

控制总线

由不同的控制线组成,其宽度决定了cpu对外部器件的控制力

列如:"读信号输出"的控制线,cpu向该线输出低电平表示要读取数据

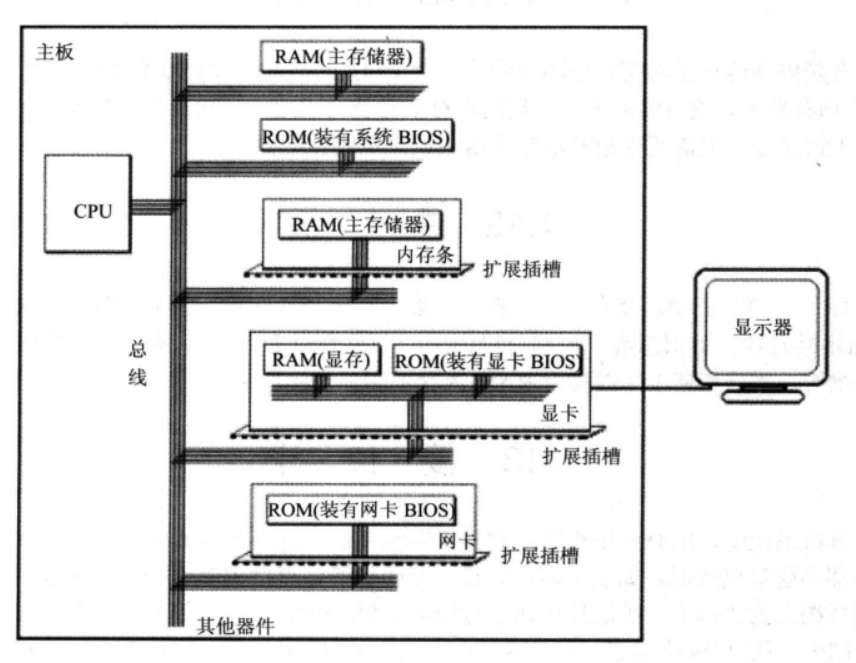

主板

cpu,存储器,外围芯片组等在主板上,通过总线相连

接口卡

cpu不能直接控制外设(显示器,音箱),外设连接插在扩展插槽上的接口卡,cpu通过总线控制接口卡,接口卡控制外设

存储器芯片

随机存储器(RAM)

内存

与CPU直接交换数据的内部存储器。

速度很快,断电所存储的数据将丢失

接口卡上的RAM

接口卡的内存,如显存,显卡将显示的内容放在显存上再输出到显示器

只读存储器(ROM)

BIOS(基本输入/输出系统)

主板和各类接口卡(显卡网卡)厂商提供的软件系统

以上存储器均与总线相连,cpu将这些存储器看作一个由若干个存储单元组成的逻辑存储器(内存地址空间)

逻辑存储器大小受cpu寻址能力限制

总线地址宽度为20,则可以传输2^20个不同地址信息(定位2^20个内存单元)

1内存单元为字节

地址总线为20,2^20byte=1MB

地址总线为32,2^32byte=4GB

地址总线为32,2^32byte=4GB

寄存器

cpu一般由运算器、控制器、寄存器等器件构成,由总线(相对于cpu为内部总线)相连

运算器进行信息处理;

寄存器进行信息存储;

控制器控制各种器件进行工作;

内部总线连接各种器件,在它们之间进行数据的传送。

汇编主要学习寄存器,可以用指令改变寄存器内容实现控制cpu

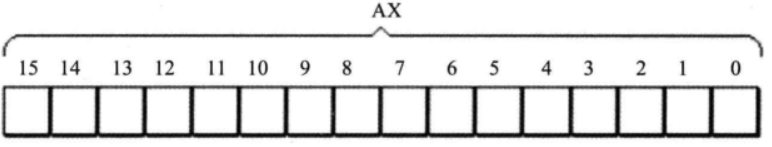

8086CPU 有14个寄存器: AX、BX、CX、DX、SI、DI、SP、BP、IP、CS、SS、DS、ES、PSW

通用寄存器

AX、BX、CX、DX通常用来存放一般性数据

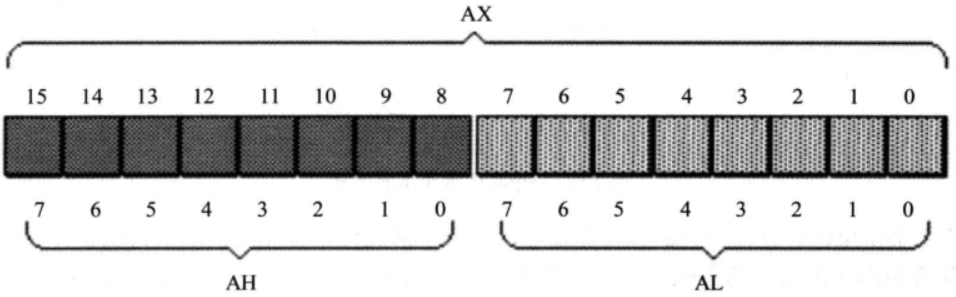

AX的逻辑结构

这是16位寄存器,为了兼容上一代的8位寄存器,通用寄存器可分为两个独立8位寄存器

AX可分为AH和AL;

BX可分为BH和BL;

CX可分为CH和CL;

DX可分为DH和DL。

AX的低8位(0位~7位)构成了AL寄存器,高8位(8位~15位)构成了AH寄存器。

AH和AL寄存器是可以独立使用的8位寄存器。图2.4展示了16位寄存器及它所分成的

两个8位寄存器的数据存储的情况。

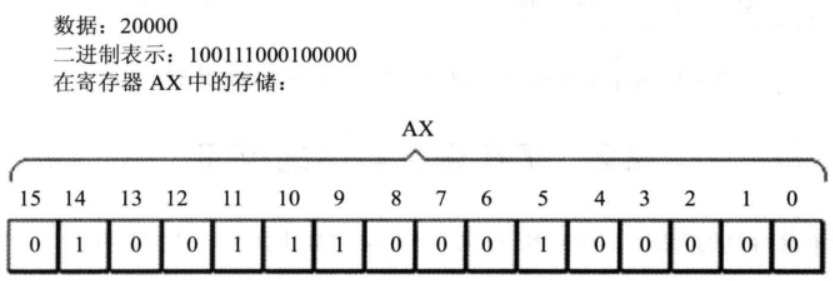

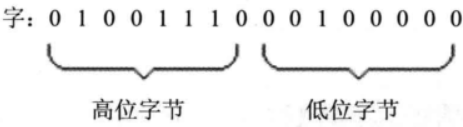

存储器中的字

字节(byte)由8bit组成,可存于8位寄存器中

字(word),一个字由两个字节组成。分别为这个字的高位字节和低位字节

例:20000的二进制是100 1110 0010 0000

AH寄存器存储高8位:100 1110

AL寄存器存储低8位::0010 0000

合起来是20000,拆分来看AH为78 AL为32

简单汇编指令

注意:

AX:9999H BX:9876H

执行add ax,bx后,因为AX是16位存储器,只能存放4位16进制,所以AX的值为320F(计算结果为1320F)

物理地址

内存单元逻辑上为一个存储空间,每个内存单元在这个空间中的地址被称为物理地址

8086cpu有20位地址总线,可以传送20位地址,寻址能力为1MB

8086使用两个16位地址合成20位物理地址,cpu内部相关部件提供两个16位地址后通过内部总线送到cpu内部的地址加法器

之后再输出到地址总线

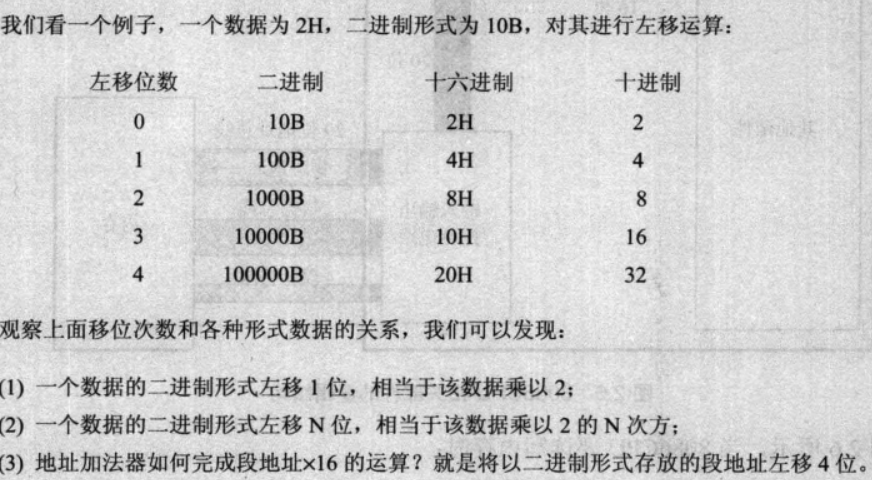

地址加法器采用物理地址=段地址*16+偏移地址的方法来合成

当段地址是十六进制时,左移一位(4EH变4E0H,20H变200H)

当段地址时十进制时,乘以16

当段地址是二进制时,左移四位或者说直接*10000 (4EH二进制为100 1110 左移四位就是100 11100000,转为十六进制就是4E0H)

访问123C8H的内存单元

注意,这里的1230是十六进制

段地址*16也叫左移4位

注意,是十进制换算成二进制后左移的规律

段地址中的段,并不是值内存分段了,而是cpu划分了内存单元,相当于给了编号

可将地址连续,起始位置为16的倍数的一组内存定义为一个段

数据在21F60H内存单元,对于8086cpu的描述为:

数据存在内存2000:1F60单元中

数据存在内存的2000段中的1F60单元中

段寄存器

段地址在8086cpu的段寄存器中存放

8086cpu有四个段寄存器:CS,DS,SS,ES

CS和IP

8086cpu中最关键的两个寄存器,指示了cpu当前读取指令的地址

CS为代码段寄存器,IP为指令指针寄存器

两个寄存器的内容通过地址加法器合成内容(CS*16+IP)

而CS:IP指向的内容被当作指令处理

修改这两个寄存器内容不能用MOV

而是

jmp 段地址:偏移地址,如

jmp 2AE3:3,执行后: CS= 2AE3H, IP=0003H, CPU将从2AE33H处读取指令。

jmp 3:0B16,执行后: CS=0003H, IP=0B16H, CPU 将从00B46H处读取指令。

只改变IP的内容

jmp ax, 指令执行前: ax=1000H, CS=2000H,IP=0003H

指令执行后: ax=1000H, CS= 2000H,IP=1000H

jmp bx, 指令执行前: bx=0B16H,CS=2000H, IP=0003H

指令执行后: bx=0B16H,CS =2000H,IP=0B16H

代码段

可以将长度为N(N<=64KB)的一组代码,存放一组连续、起始地址为16的倍数的内存单元中

这段内存是用来存放代码的,名叫代码段

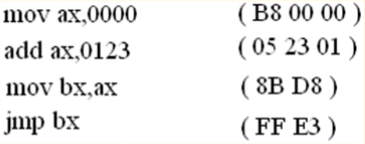

例子:

这段长度是十个字节的指令,存放在123B0H~123B9H的一组内存单元中

可以认为这是一个段地址为123BH,长度为10个字节的代码段

要想执行这个代码段。得让CS=123BH,IP=0000H

让物理地址指向代码段开头

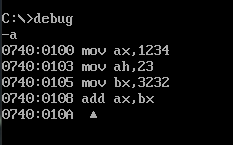

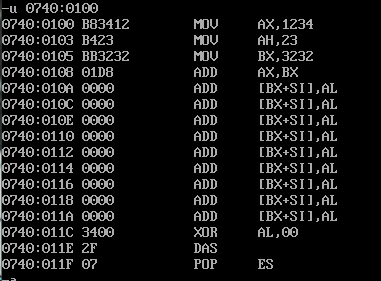

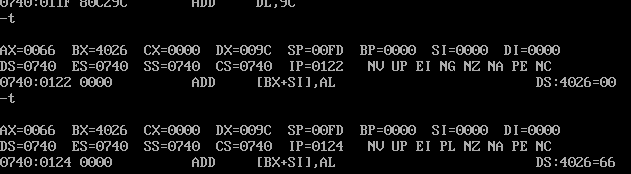

debug

R命令查看、改变CPU寄存器的内容;

D命令查看内存中的内容:

E命令改写内存中的内容;

U命令将内存中的机器指令翻译成汇编指令;

T命令执行一条机器指令;

A命令以汇编指令的格式在内存中写入一条机器指令。

左边是CS:IP

mov ax,1234为3个字节。所以下个IP地址是103

右边是转换成ASCII码

查看内容可以指定起始位置

d 1000:0 9表示1000:0~1000:9

t执行命令需要指定地址

使用r来改变CS:IP

按一下执行一个指令

小结

(1)汇编指令是机器指令的助记符,同机器指令一一对应。

(2)每一种CPU都有自己的汇编指令集。

(3) CPU可以直接使用的信息在存储器中存放。

(4)在存储器中指令和数据没有任何区别,都是二进制信息。

(5)一个存储单元可以存储8个bit(8位二进制数)

(6)CPU芯片有许多管脚,这些管脚和脚引出总线。

地址总线的宽度决定了CPU的寻址能力;

数据总线的宽度决定了CPU与其它器件进行数据传送时一次数据传送量;

控制总线宽度决定了CPU对系统中其它器件的控制能力。

参考: 王爽 - 汇编语言 和 小甲鱼零基础汇编