Jesd204b调试理解

JESD204B是一种新型的基于高速SERDES的ADC/DAC数据传输接口。随着ADC/DAC采样速率的不断提高,数据的吞吐量也越来越大,对于500MSPS以上的ADC/DAC,动辄就是几十个G的数据吞吐率,而采用传统的CMOS和LVDS已经很难满足设计要求;

优点:JESD204B接口相对于LVDS的优势包括:数据接口布线所需电路板空间更少,以及转换器和逻辑器件的封装更小 ;支持多芯片同步;

关键变量

M:converters/device,转换器(AD/DA)数量

L:lanes/ device(link),通道数量

F:octets/frame(per lane),每帧的8位字节数

K:frames/multiframe,每个多帧的帧数

N:converter resolution,转换器分辨率

N’:total bits/sample,4的倍数,N’=N+控制和伪数据位。

S:samples/converter/frame cycle,每个转换器每帧发送的样本数。当S=1时,帧时钟=采样时钟

CS:control bits/sample

三种子类工作模式:

- subclass0:只进行通道对齐,不具确定性延时;

- subclass1:支持确定性延时,SYSREF;支持多芯片同步;

- subclass2:支持确定性延时,SYNC

SYSREF与LFMC的关系:

Note :sysclk周期需要大于等于本地多帧时钟周期LFMC的大小

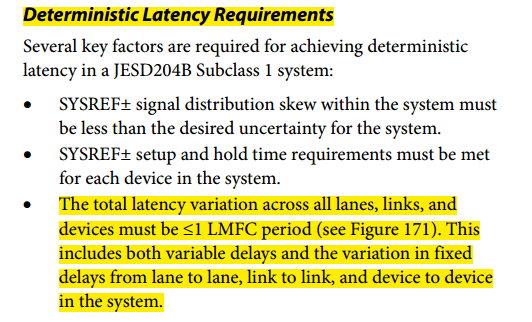

子类1确定性延时需要满足的条件:

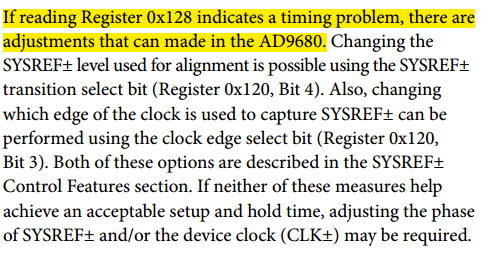

其中第二点在高采样率条件下显得特别重要,其对时序要求更高,因此需要满足sysclk与device clk的建立保持时间条件;在AD9680中,可以通过读取寄存器0x128观察是否满足条件,若不满足,可以通过调整sysclk相关控制寄存器0x120,改变上升 沿或者下降沿等手段,或者通过调整9680的clock fine delay,改变时序;详细说明见下图;

浙公网安备 33010602011771号

浙公网安备 33010602011771号