AHB总线

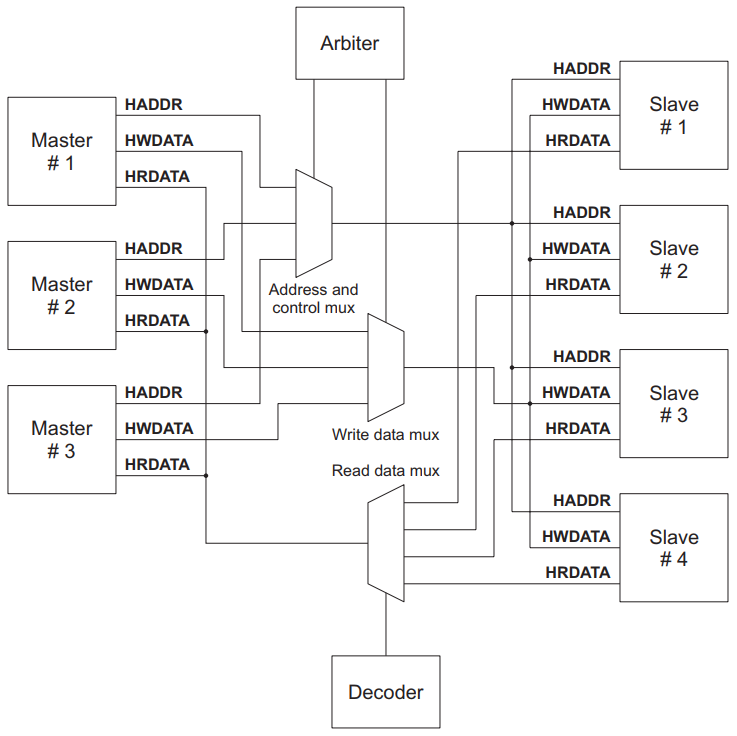

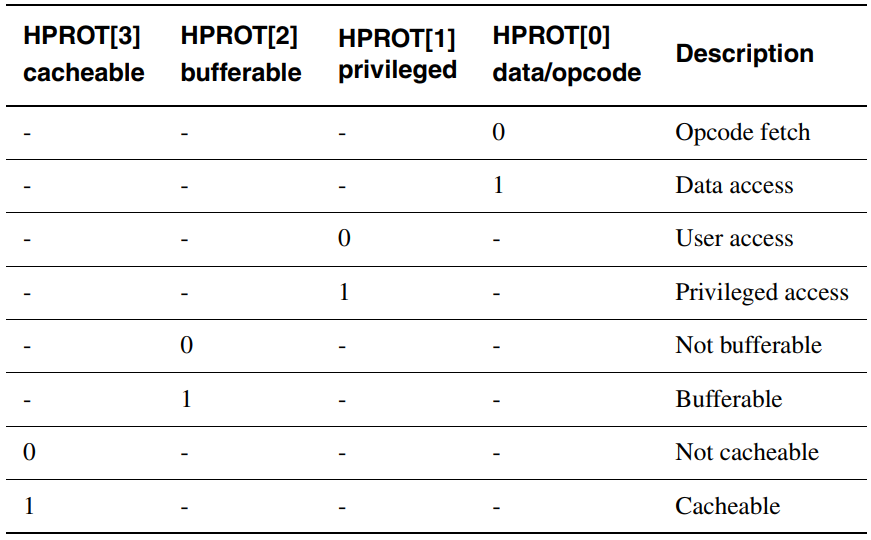

图示一个3主机,4从机的AHB interconnection 示意图

通过多路复用器multiplexor连接多个主机或从机,所有的从机的RDATA通过MUX连接到每个主机,所有主机的WDATA通过MUX连接到每个从机。同时读操作的MUX由Decoder控制合适的所选从机进行数据和相应传输(rdata & response)。写操作的MUX由Arbiter控制,决定哪一个主机获得BUS的使用权(granted address & control signals routed all slaves)。

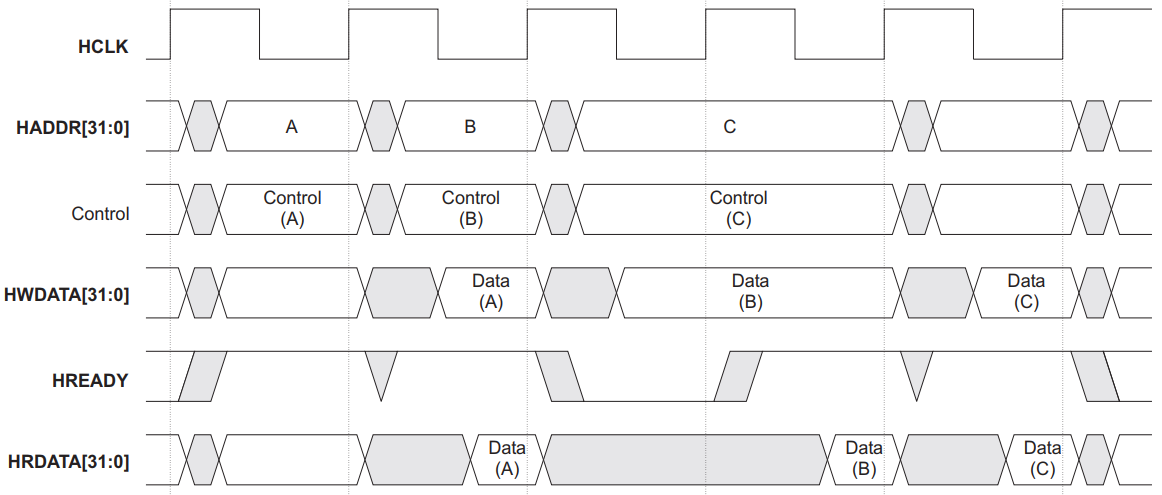

总线操作——主机发起总线申请,Arbiter授权后主机获得address和control(方向,传输宽度,burst种类等) signals。一次transfer包括——一个周期的地址和控制;一个或多个周期的数据

主机向某个从机传输时,所有从机都要采样address(address cannot be extended);而数据可以通过HREADY进行扩展,它LOW时是在transfer中插入等待状态,从机可以进行数据收发。

从机HRESP[1:0]

- OKAY——当前传输正常,如果遇到HREADY表示传输结束

- ERROR——当前出错

- SPILT,RETRY——当前传输是未完成的,主机需要继续尝试传输

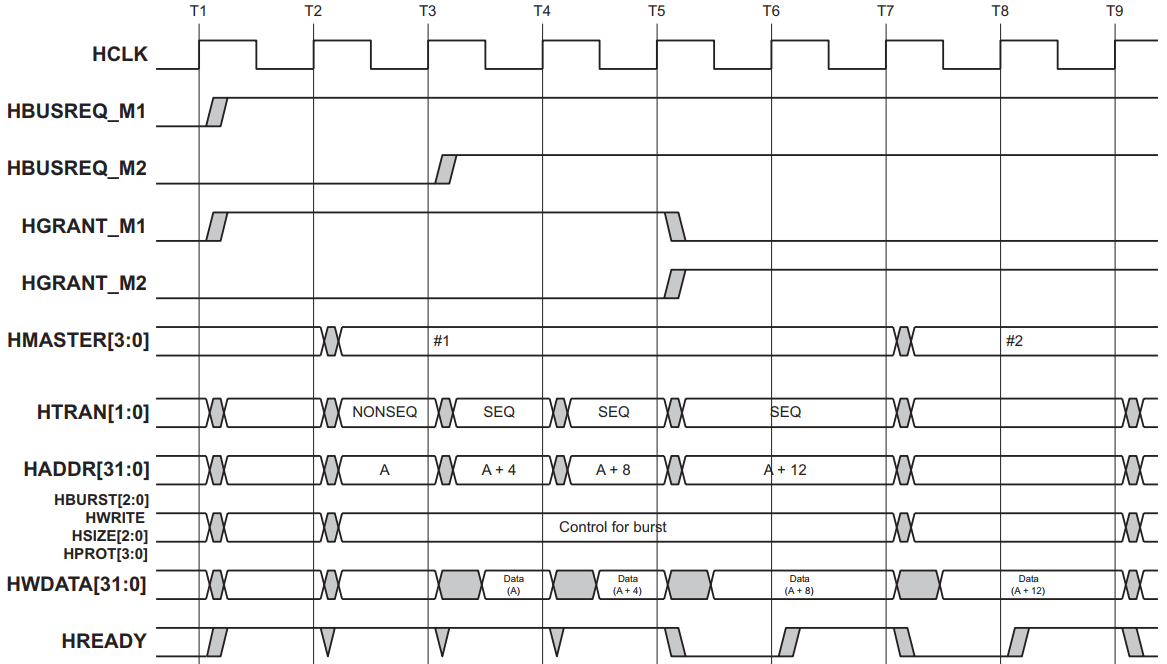

通常主机可以完成burst在仲裁机将权限授予下一次主机之前。但为了防止过长的仲裁延时打断了一次burst行为,那么当事主机必须重新申请仲裁授权以继续完成中断你的burst。

Transfer特性

在传输中,从机可以进行等待,如果从机发生等待那么主机必须一致保持数据直到这cycle数据被接收(在单cycle transfer中,[此时HRESP应该是OKAY] 时序图上就是取决于HREADY)。并且当多个transfer发生时,从机等待会造成主机address & control signal phase与 data phase交织。(实际上这是流水线总线传输的特性,保证了传输的性能,图中C的address & control phase和 B data phase交织了)

TRANSFER 传输类别

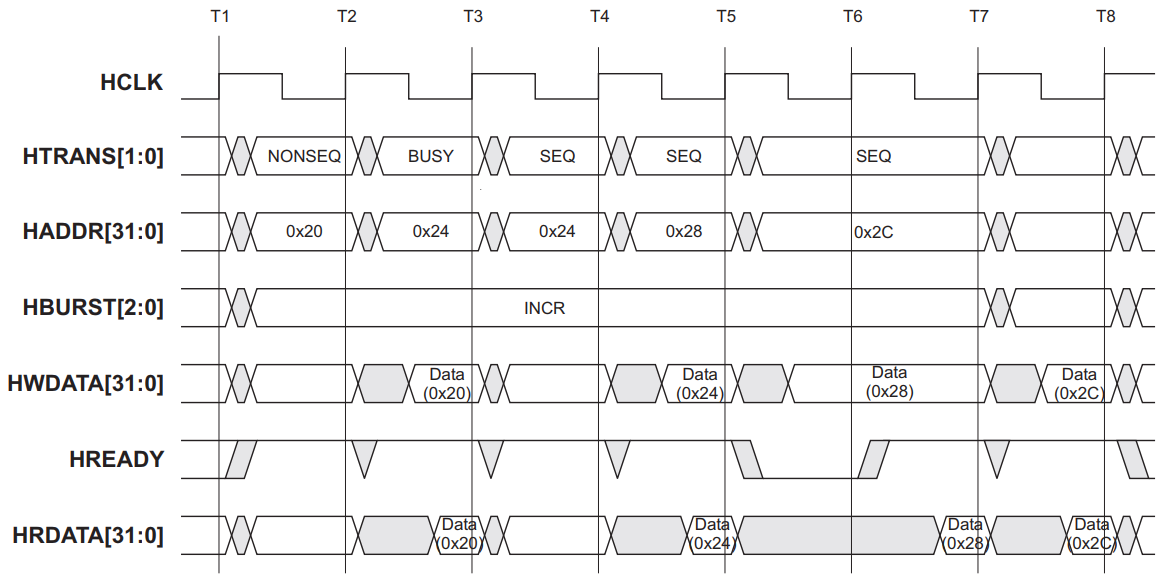

分为IDIE,BUSY,NONSEQ,SEQ

- IDIE——主机granted后,没有给从机传输的意思,就要以IDIE transfer type发送。从机必须响应zero-wait state OKAY response(HRESP,HREADY),并且无视data

- BUSY——主机在进行BURST传输中(未完成),无法继续data transfer的时候,要以BUSY type发送表示空数据,上一个transfer必然是SEQ,NONSEQ。从机必须响应zero-wait state OKAY response(HRESP,HREADY),并且无视data

- NONSEQ——主机进行burst传输的第一个transfer和非burst的transfer 都要用NONSEQ;它标志新的开始,与上一个transfer类别无关

- SEQ——主机在Burst中的第二次到结束的有效transfer用SEQ,上一个transfer必然是SEQ,BUSY,NONSEQ。并且这次transfer的控制信号不变,地址信号与上一次关联(递增或wrap循环)

(后续会解释如何以32bits位宽总线发16bits数据)

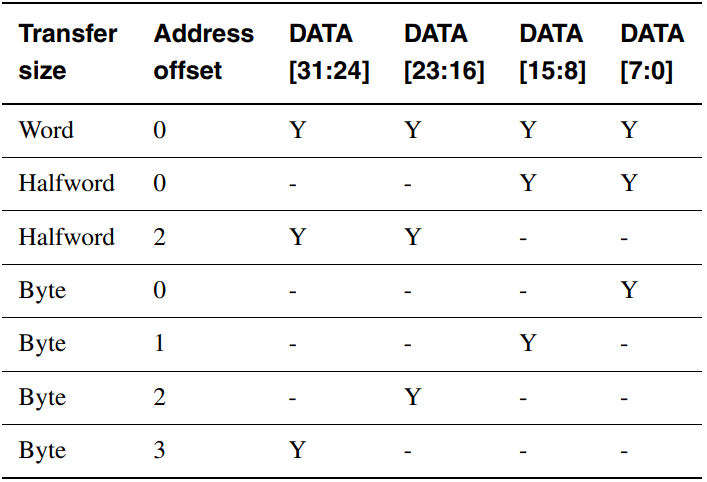

Burst种类

| HBURST[2:0] |

Type | Description |

| 000 | SINGLE | Single transfer |

| 001 | INCR | Incrementing burst of unspecified length |

| 010 | WRAP4 | 4-beat wrapping burst |

| 011 | INCR4 | 4-beat incrementing burst |

| 100 | WRAP8 | 8-beat wrapping burst |

| 101 | INCR8 | 8-beat incrementing burst |

| 110 | WRAP16 | 16-beat wrapping burst |

| 111 | INCR16 | 16-beat incrementing burst |

burst中的transfer必须有,transfer size和address boundary 对齐。例如word(4byte)要和HADDR[1:0]==00,half word(16bits)要和HADDR[0]==0。Burst的地址边界是1KB,进行burst传输不能超过这个地址范围

如果主机的burst过早结束了,从机可以通过transfer type判断下一次主机再进行transfer的情况。如果是SEQ或者BUSY则可以认为主机继续进行了中断burst的transfer;如果主机transfer type是NONSEQ或者IDIE说明上一次提前终止的burst已经截止了。如果主机因为失去BUS授权中断了burst,那下一次获取BUS ownership应该重建burst传输。e.g. 在4-beats burst由于arbiter中断了,下一次granted时候,主机可以用INCR进行3次transfer 完成burst。

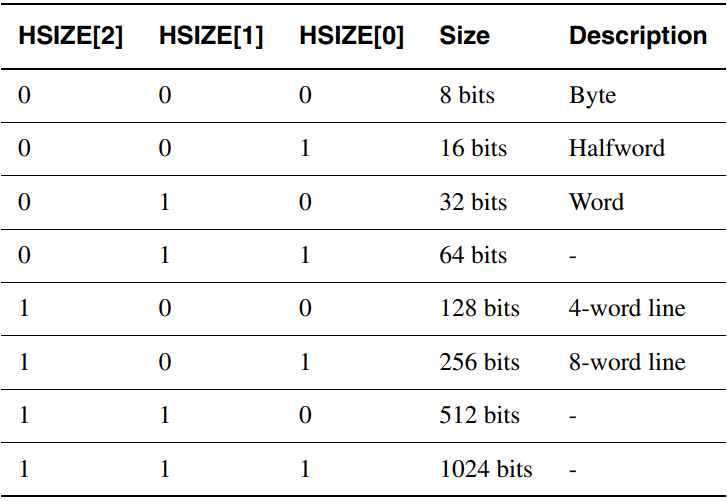

Control 信号

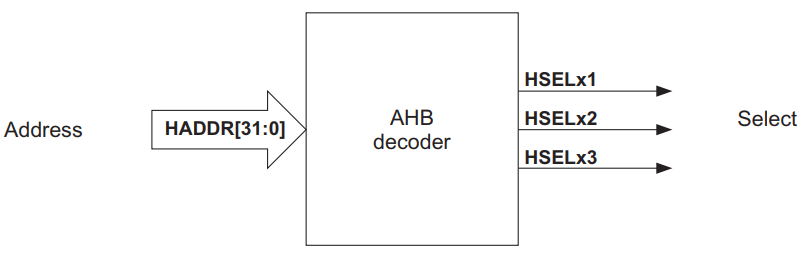

Address Decoding

从机被分配的最小地址空间是1KB,因此主机进行burst不能超过地址范围是1KB。e.g. 写到0x3FC(1020),下一次不能写8Byte,要先写4Byte,超过0x400(1020)再写。如果主机的transfer以SEQ,NONSEQ的type访问了从机不存在的地址空间,从机返回ERROR response;如果主机transfer type以IDIE,BUSY访问不存在的地址空间,从机回复OKAY response。

所谓地址解码,实际上就是通过主机transfer访问不同的address 范围,确定出不同从机对应的address范围,生成HSELx 从机选择信号。

Slave Response

AHB总线没有机制说,主机开始transfer就立刻取消它。

从机响应采用HRESP和HREADY结合的方法,HREADY HIGH表示当前transfer是正常的,LOW表示进行等待(extend transfer)

• complete the transfer immediately 立刻完成

• insert one or more wait states to allow time to complete the transfer 插入等待

• signal an error to indicate that the transfer has failed 错误

• delay the completion of the transfer, but allow the master and slave to back off the bus, leaving it available for other transfers. 延时完成传输,允许主从退出总线,令总线进行其他传输

从机挂起总线前,必须预知到要插入的wait state的数量。推荐但不强制,不要超过16个

除了OKAY,剩余的ERROR,RETRY,SPLIT 3个response都是至少2-cycle response。OKAY响应可能在HREADY是LOW的情况下。RETRY是没有完成传输,主机必须进行重传。SPLIT是主机授权中断,再次获取总线后应该继续传输;当传输完成时,从机可以代表主机访问BUS。2-cycle response就是通过控制HREADY来完成的,倒数第二个cycle,从机HREADY LOW,HRESP[1:0]显示ERROR,SPLIT或者RETRY;倒数第一个cycle,从机HREADY HIGH,HRESP[1:0]继续保持。而2-cycle以上的 response,同样需要HREADY LOW操作,但除最后2个response为ERROR等状态外必须是OKAY。

2-cycle机制是因为流水线总线的特性,这样给主机足够的时间在检测到差response后,进行address和HTRANS[1:0]调整(下一次transfer为IDIE)。

当SPLIT、RETRY响应出现时,主机必须取消接下来的下一次transfer。因为下一次transfer禁止在当前transfer完成后发生。二者都可以使得transfer从BUS中释放,让其他高优先设备访问BUS。但区别在于RETRY下,arbiter只会给更高优先级的设备;SPLIT不同,arbiter可能也会让低优先级设备使用BUS。SPILT使得从机和arbiter的设计更复杂。主机应该用同种机制处理SPILT和RETRY;再次申请BUS并发起transfer直到完成,或者收到ERROR响应。

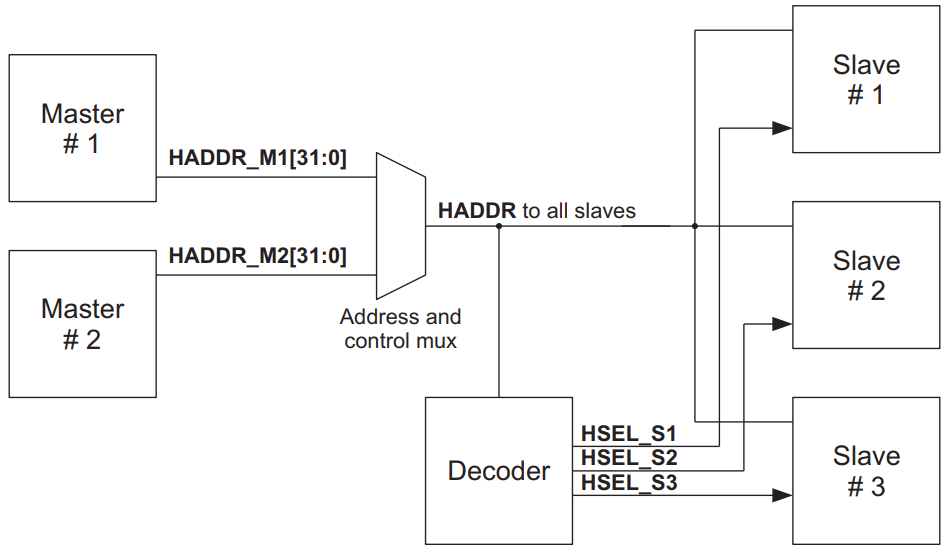

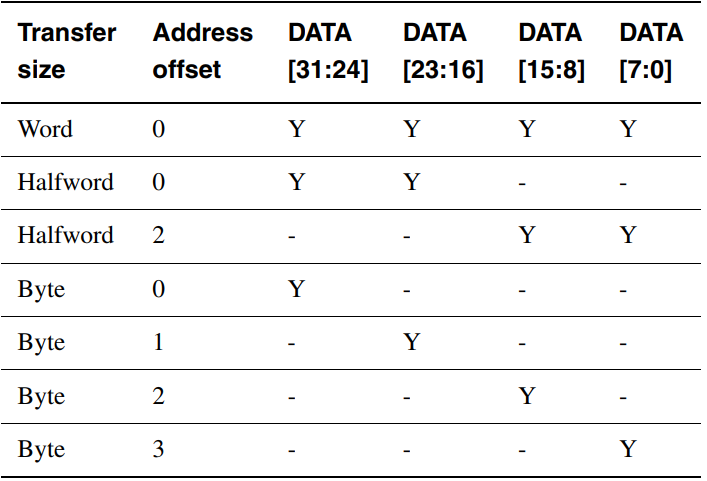

DATA BUS

在宽总线位宽进行小于位宽的数据transfer的时候,依据字节序进行byte lane选择。如果是burst的话,每个beat的byte lane都不同。在W/R的时候,相应有从机/主机在接收端对byte lane进行有效选择。在设计中所有数据路由、所有模块、桥都应该保持相同的字节序。动态调整字节序是不支持的,因为对绝大多数嵌入式设计而言,这带来了冗余。

小端——little-endian

大端——big-endian

在从机进行transfer,主机读取数据HRDATA时,主机如果需要wait state,只需HREADY LOW,并且wait state的时候不需要保持HRDATA,只需要在结束wait state的下一个cycle提供有效HRDATA并HREADY HIGH就可以了。从机的response为SPLIT, RETRY and ERROR 时,不需要提供有效HRDATA数据。

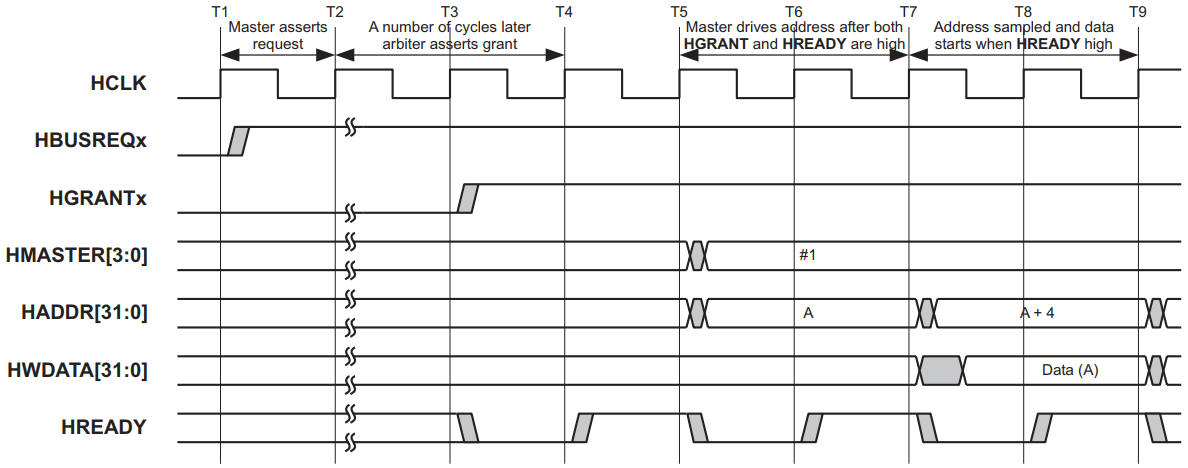

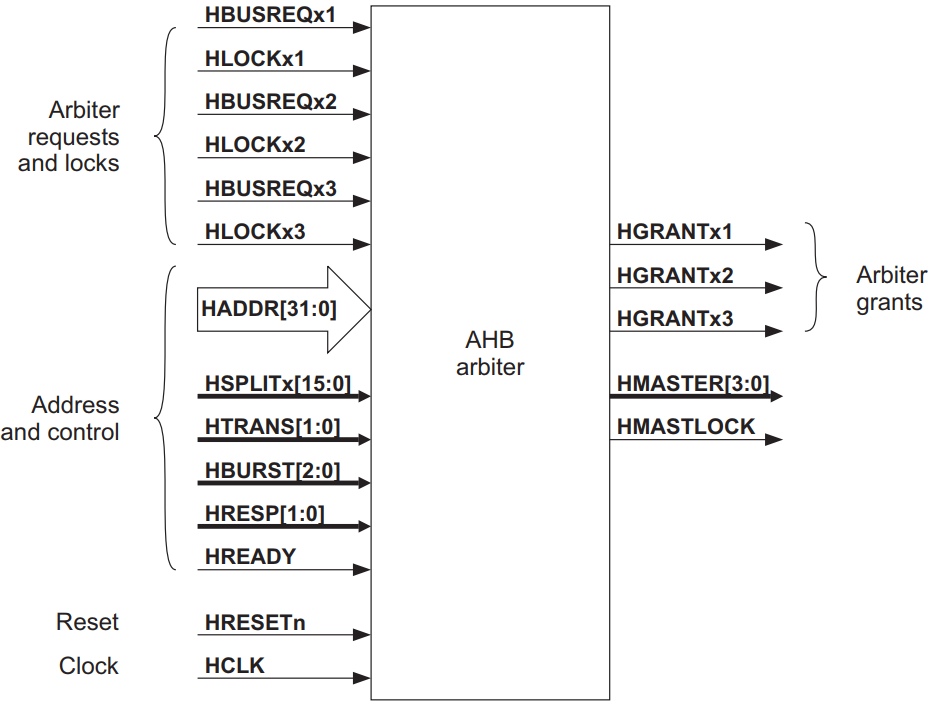

Arbitration

仲裁机的意义就是让任一时刻只有一个master使用BUS。仲裁机会扫描所有master发起的request来决定谁有最高的总线访问优先级,并且也会处理来自slave进行SPLIT transfer的请求。从机不支持SPLIT则无需了解arbitration过程,但他们需要关注由于总线所有变化时导致的burst中止。

- 在AHB中最多有16个master,每个master有一个用于发起仲裁请求的HBUSREQx;

- master在进行不可分割的传输时,需要通过HLOCKx标记总线申请(在HBUSREQx HIGH的同时),为了防止仲裁机改变BUS所有权,必须在第一次transfer发出address之前一个cycle先有HLOCKx HIGH;

- master在自己所属的HGRANTx HIGH时获得了总线最高优先级的仲裁——在HREADY,HGRANTx为HIGH并且HCLK为上升沿的时候

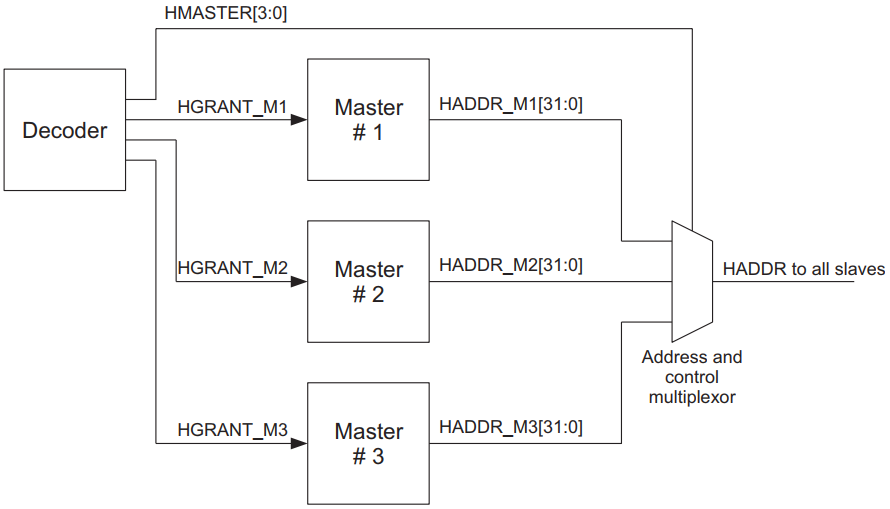

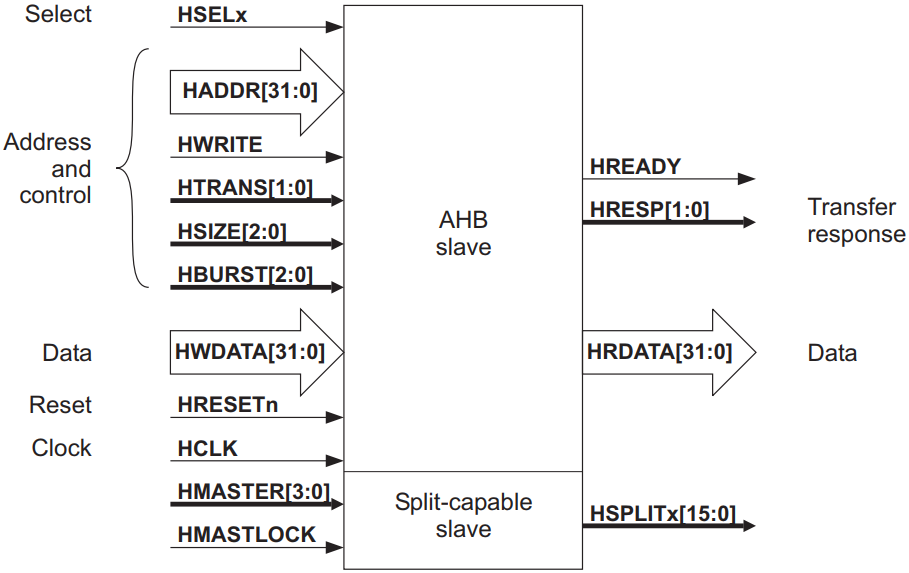

- HMASTER[3:0]标记了仲裁机将哪个主机的优先级置为最高,以控制地址和控制多路复用器。同时进行SPLIT的slave也需要HMASTER[3:0]标记哪个主机需要进行SPLIT transfer

- HMASTLOCK被仲裁机用来表示当前BUS的transfer是被锁定用来不可分割transfer的,该信号时序与address和control信号一样

- HSPLIT[15:0] 是从机用来指示需要SPLIT传输的主机,从而仲裁机可以决定让相应主机完成SPLIT

master在进行一个固定burst的时候,不必担心总线授权的中断,因为仲裁机会检测HBURST[2:0]信号。如果master进行非固定长度burst被中断了(仲裁机不会预测unfixed-length burst),它必须持续申请总线直到开始最后一次transfer。如果master burst时候中断,同样必须持续HBUSREQx 为HIGH申请总线完成burst。master完成一次burst后,通常需要再次申请总线。可能存在没有主机需要使用BUS,仲裁机会将权限给一个默认主机,此时无需transfer但获取了ownership的主机,必须进行HTRANS[1:0]为IDIE的传输。

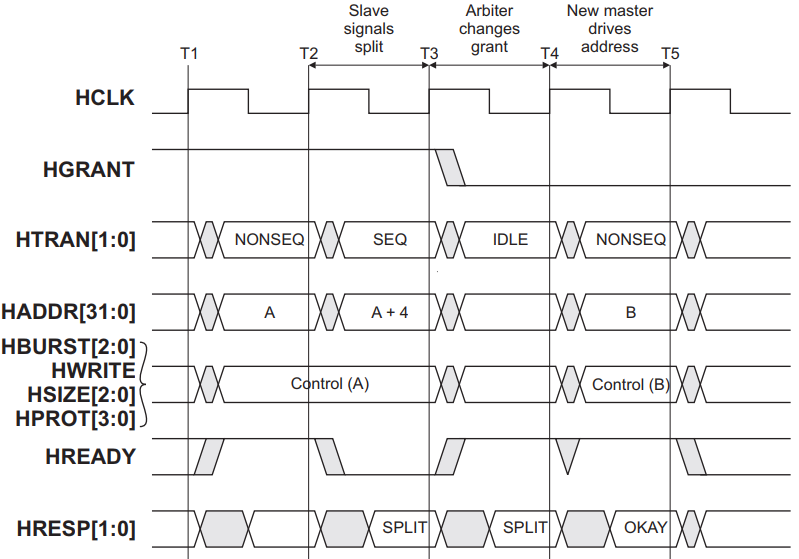

这个图画错了,Decoder应该Arbiter。图示了HGRANTx与HMASTER怎么进行控制master和multiplexor的。

主机在HREADY和HGRANTx同时HIGH获的授权。

仲裁机在master之间切换总线授权时,master获取grant的时候比address变更要晚,因为上一个master的地址和数据还在传输。

通常一个主机在burst中不会被仲裁机中断,但防止单个主机过度占有BUS,仲裁机可能会提前中止主机的总线。一旦中止,主机需要重新申请仲裁,并且体现在HBURST和HTRANS中表明不是一次完整的burst。e.g. 如果8-beat的busrt在3个transfer以后断了,那么重新开始的burst要么是length==5的unfixed-length busrt,要么是4-beat busrt再加一个single burst。仲裁机应该在HLOCKx的场合,多分配一个transfer给主机,以保证最后一个transfer被顺利响应而不是SPILT或者RETRY。仲裁机还应该发起HMASTLOCK确保所有从机知道当前transfer是lock。

默认主机必须被授权当所有其他主机等待SPLIT transfer完成时。默认主机在不需访问BUS却被授权时,要发IDIE transfer。

SPLIT

当从机发起SPLIT response时,仲裁机不会给匹配主机BUS权限。因此仲裁机会检测所有的response信号。仲裁机会在每个周期扫描HSPLITx,如果从机能够进行SPLIT传输,会发起HSPLITx bit为HIGH,仲裁机应该在检测到这种情况时授予相应主机BUS权限。

从机应该检测HMASTER并记录,以确保从机响应SPLIT的时候,能够在恢复SPLIT传输时对应到相关主机。如果仲裁机打算恢复一个收到SPLIT响应主机,使其继续传输时,如果有更高优先级的主机申请BUS,那么SPLIT传输的主机或许会被搁置。SPLIT传输被继续完成后,从机应该进行OKAY response。

总线协议要求一个主机只允许有一个未完成的事物(SPLIT RETRY),如果主机可以有多个未完成的事物(outstanding transaction),那么主机需要多条BUS REQ信号表示不同的transaction。一个模块可能在一个总线网络上是多个不同BUS的主机,但它允许有一个outstanding transaction。SPLIT能力的从机可能同时收到多个主机的请求,但它只需要响应SPLIT无需几率主机的地址、控制数据;该从机需要记录被响应SPLIT的主机数字。当合适的时候,从机需要设置要回复SPLIT传输主机所对应的HSPLITx bit就可以了。如果主机被仲裁机授权进行BUS传输,那主机需要传输之前SPLIT后续的地址和控制信号;完成SPLIT传输之前,主机可能被多次授权(SPLIT好几次)。

防止死锁——当多个主机访问一个从机,而从机响应SPLIT或RETRY response时却没有能力处理这么多个主机,可能发生死锁。

为了防止SPLIT导致死锁,从机需要能够接收来自16个主机的请求,从机无需记录主机控制和地址信号,只需要知道有transfer被SPLIT响应了。最终所有主机的优先级都是低的,而从机可以依次和仲裁机解决每个主机的请求。从机可以以任何顺序进行与主机的outstanding transaction,但必须先进行LOCK transaction再进行其他transaction。

响应了RETRY的从机只能在一个时刻被一个主机访问。但防止多个主机访问响应RETRY从机的硬件保护不是本协议强制的。而这种硬件保护可以被从机自身所实现,从机可以检测连接的主机是不是发出RETRY响应的主机(通过主机序号),如果发生重传行为从机就检测主机序号,如果不是同一个主机,从机可以响应ERROR、触发系统中断,触发完全系统复位,发信号给Arbiter。

当发生SPLIT或者RETRY response时,主机应该在下一个周期发送IDIE transfer,以保证BUS handover(这使得HGRANTx变更后new master会遇到IDIE引起的HREADY,顺利变更BUS ownership )。如图

一般来说建议最小32bit,最大256bit的AHB总线

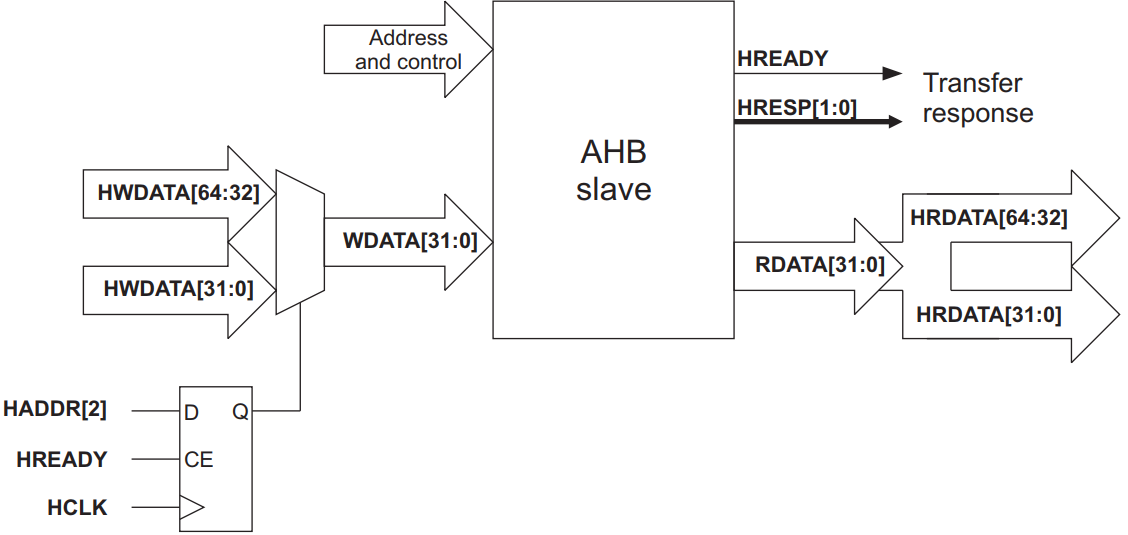

宽总线实现窄从机

例如一个原先32bit总线的从机要移植到64bit总线上,只需要补充外部逻辑即可,无需内部修改从机设计。

输出把32bit复制到64bit的两半中;补充逻辑确保只有64bit合适的一半被改变

一旦收到64bit的数据就返回一个ERROR response(从HSIZE上来判断)。

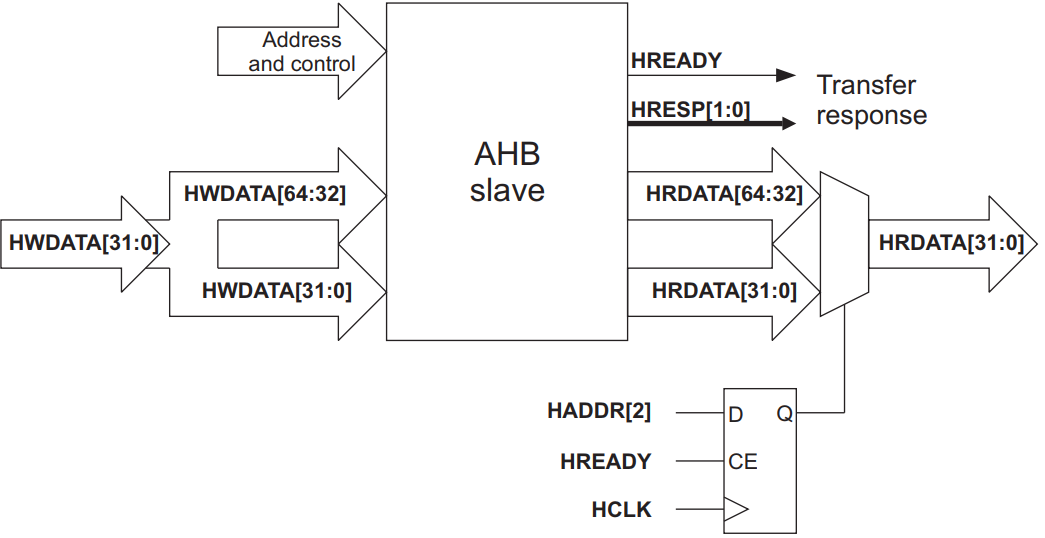

窄总线上实现宽从机

需要把主机的输出复制,然后把主机的输入以多路复用选择。由于主机位宽低,所以主机transfer从机的时候数据都是32bit的,不会影响写入。读取加上选择器不会影响输出。

AHB从机

AHB主机

AHB仲裁机

AHB解码器