关于Xilinx FPGA/ZYNQ的引脚定义

器件的引脚定义如何获得?

在官网找到Pin-Out文件,网址:https://www.xilinx.com/support/package-pinout-files.html

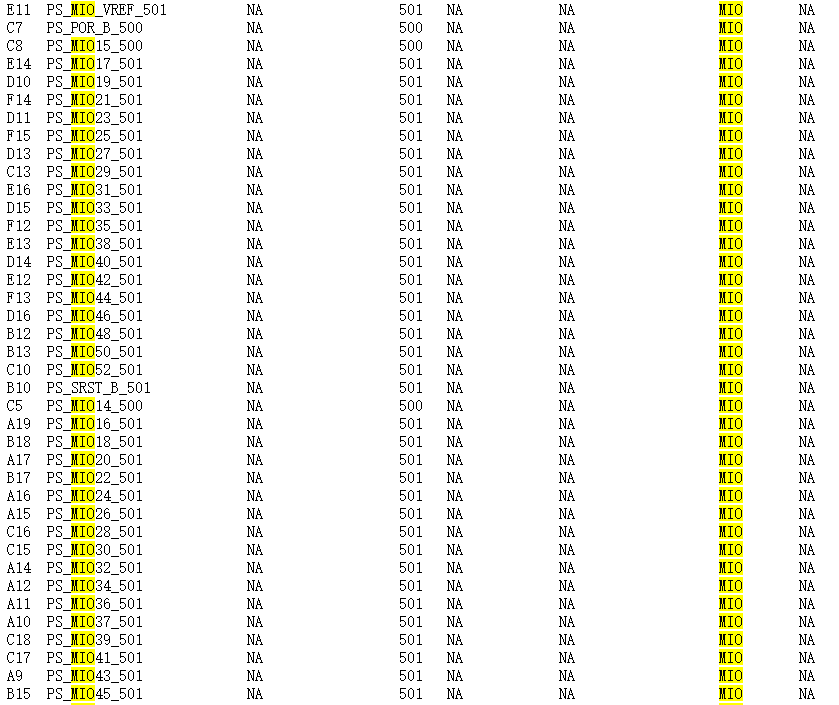

文件里面给出了引脚编号对应的引脚名称、IO Bank分组、IO种类(MIO,High Rate通用IO,DDR等)。

这些封装对应到Processing System 7 IP中的MIO设定,就可以得到MIO的固定引脚。

另外,ZYNQ7000系列的引脚定义文件在这里(CSV和TXT):https://www.xilinx.com/support/packagefiles/z7packages/z7all.zip

//**********************************************************************************************************************************

//**********************************************************************************************************************************

//**********************************************************************************************************************************

例如,IP核中选择以太网MAC控制器的引脚是MIO[27:16],

则在下表中寻找MIO[16],……,MIO[27]即可,最左边即是引脚编号。(电路设计时注意Bank500和Bank501的IO电压分配)

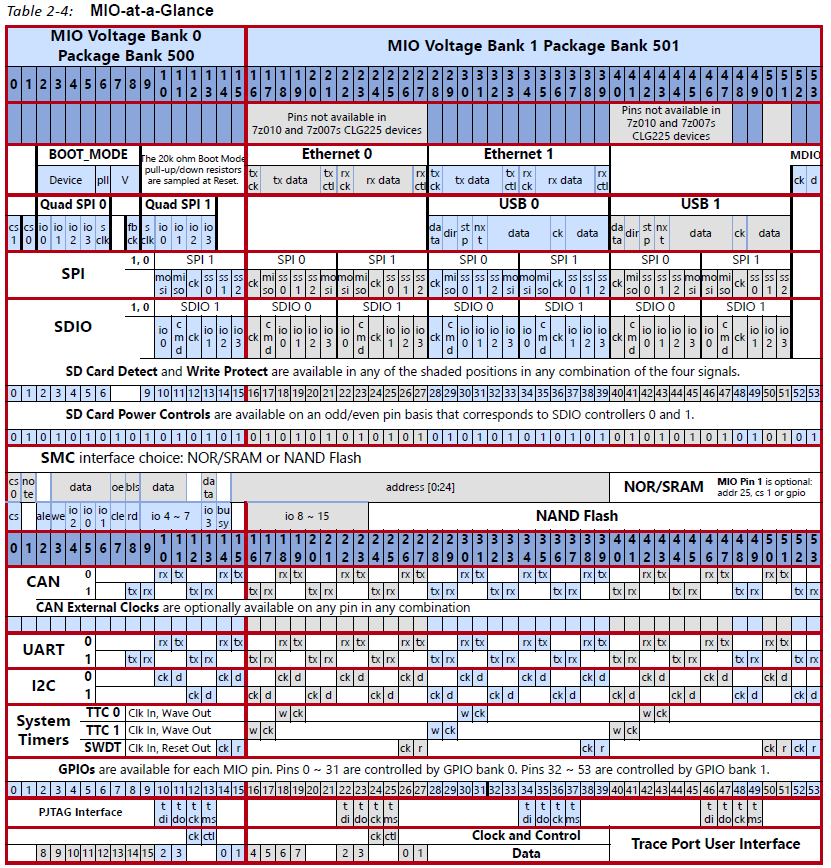

在UG585(v1.12.2)中的Table 2-4:MIO-at-a-Glance中,对MIO的功能进行了详细的描述:

表中信息包括了MIO编号、所在的IO Bank、引脚复用情况、引脚对应外设的功能。

如果使用以太网控制器ETH0,则MIO16是TX_CLK,MIO17~MIO20是TX_DATA[0]~TX_DATA[3],MIO21是TX_CTRL

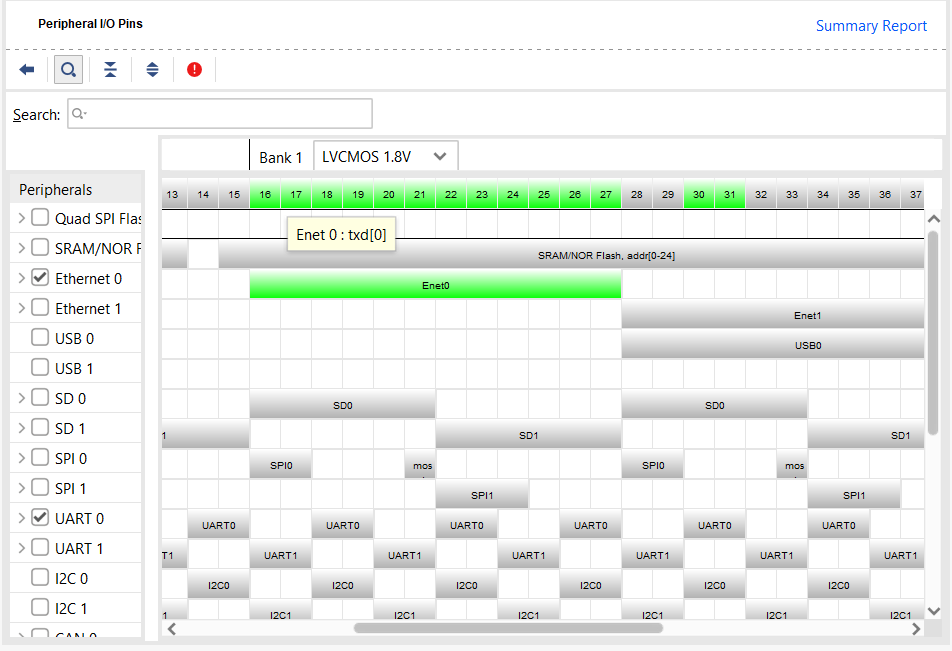

对于不明确的MIO引脚定义,将鼠标悬停在MIO编号栏就可以看到信号定义:

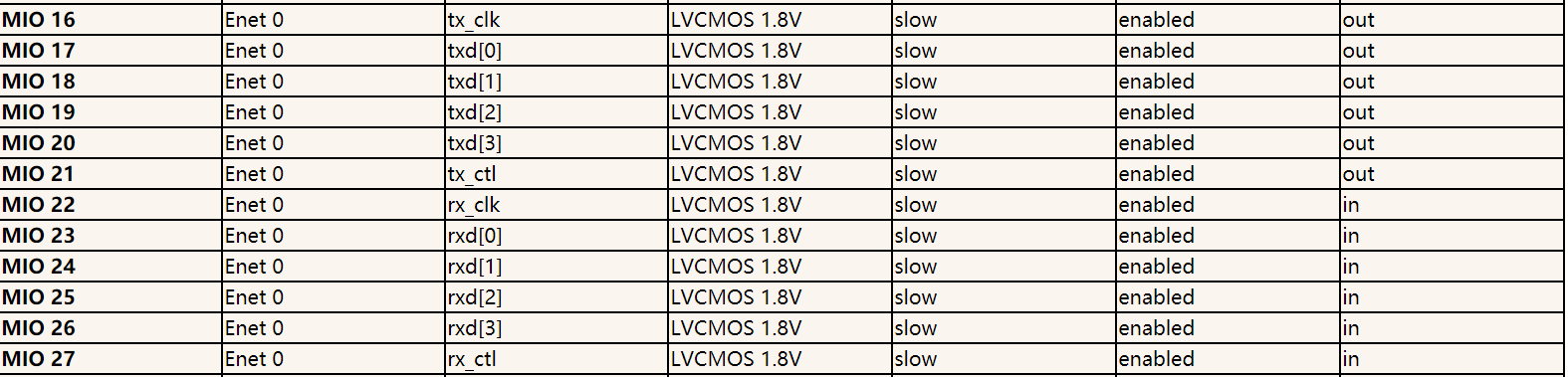

我们还通过Block Diagram综合后的报告查看,目标位于:${Vivado Project Path}\eth_mac_01.srcs\sources_1\bd\block_01\ip\block_01_processing_system7_0_2,

是以html格式呈现的:

这样就完成了MIO功能到封装引脚的映射过程。

浙公网安备 33010602011771号

浙公网安备 33010602011771号