modelSIM仿真应用笔记-Tcl文件执行仿真

利用modelSIM环境+Altera仿真库进行乘法器的仿真。

(建立工程、添加仿真文件、设定仿真参数这些还没有用Tcl实现)

在modelSIM中建立Project,添加模块源文件(功能模块和DUT定义)、Testbench文件(tb)、和Simulation Config文件。

建立tcl文件来执行编译、仿真和波形查看:

#*** do_sim.tcl Script #*** Compile the Module in the Order vlog complex_mult.v vlog tb_complex_mult.v #*** Launch the Simulation Engine(VSIM) #*** Search the Library: verilog #*** Incremental Mode, without Optimization #*** Verbose the Process vsim -L verilog -novopt work.tb_complex_mult -vopt_verbose #*** Add the Waveforms #*** Append Each Signal in the Group Tail #*** Decimal -> Signed, Unsigned -> Itself #*** Clock and Reset add wave -position end -radix binary -height 10 -format logic sim:/tb_complex_mult/rst_n add wave -position end -radix binary -height 10 -format logic sim:/tb_complex_mult/clk #*** Input Signal: RealA, ImagA, RealB, ImagB add wave -position end -radix decimal -height 80 -format analog-step -min -512 -max 511 sim:/tb_complex_mult/a_real add wave -position end -radix decimal -height 80 -format analog-step -min -512 -max 511 sim:/tb_complex_mult/a_imag add wave -position end -radix decimal -height 80 -format analog-step -min -512 -max 511 sim:/tb_complex_mult/b_real add wave -position end -radix decimal -height 80 -format analog-step -min -512 -max 511 sim:/tb_complex_mult/b_imag #*** Input Value Control Counter add wave -position end -radix unsigned -height 80 -format analog-step -min 0 -max 255 sim:/tb_complex_mult/cnt #*** Output Result add wave -position end -radix decimal -height 80 -format analog-step -min -524288 -max 524287 sim:/tb_complex_mult/dout #*** Run the Simulation run 100ms #*** View Zoom ??? view wave #*** Stop the Simulation puts "Simulation Done, Press Anything and Press Enter to Terminate Sim." set foo_01 [gets stdin] # puts &foo_01 quit -sim

然后在modelSIM的Transcript命令窗口,执行do命令:

do do_sim.tcl

仿真、波形查看完成后,在Transcript输入回车即可结束本次仿真。

一些说明:

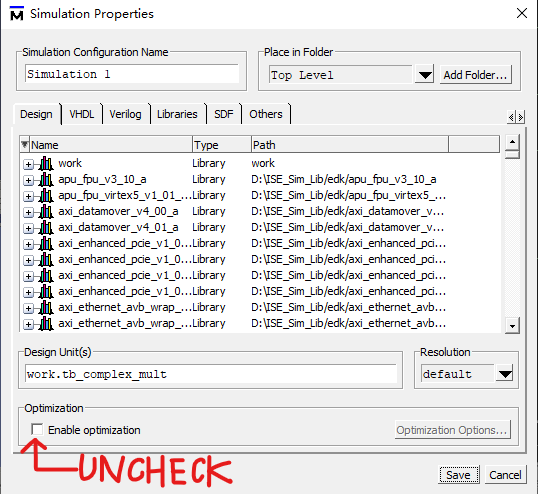

1、modelSIM的工程中,仿真设定需要取消设计优化(Enable Optimization),否则工作区的Objects窗口可能没有对应的模块和信号来观测:

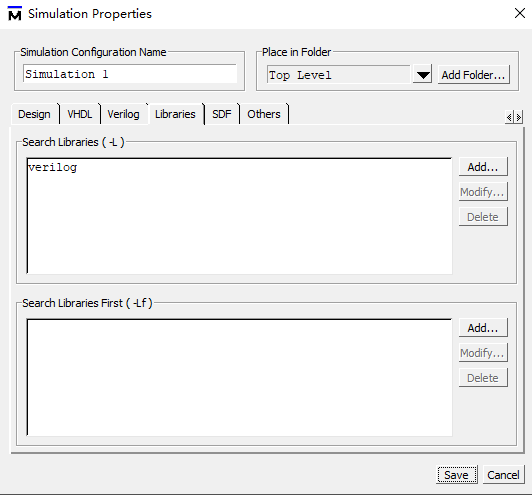

2、如果需要ipcore仿真库,需要在Search Libraries中添加库文件,并且在modelsim.ini添加库的路径:

浙公网安备 33010602011771号

浙公网安备 33010602011771号