在不使用外延层的同轴半绝缘衬底材料上制作4H-SIC横向双重注入金属氧化物半导体场效应晶体管

在不使用外延层的同轴半绝缘衬底材料上制作4H-SIC横向双重注入金属氧化物半导体场效应晶体管

- 杂志:日本应用物理杂志

在不使用外延层在同轴的半绝缘SIC衬底上制作4H-SIC横向双重注入金属氧化物半导体场效应晶体管。LDIMOSFET使用离子注入工艺从而形成电流通路层。共面波导作为栅极和漏极之间的漂移区。通过使用同轴半绝缘衬底和最优化的共面波导参数,1093伏特下的击穿电压和89.8兆欧姆·厘米2的特定导通电阻从20微米长的共面波导器件中被获得到。实验中得到的场效应晶体管的沟道迁移率为21.7cm2V-1S-1,品质因数(BV2/Ron,sp)为13.3 MW/cm2。

碳化硅材料因为高迁移率和高击穿电场,成为了高功率器件的一种有吸引力的材料。许多垂直高压器件,例如碳化硅双重注入场效应晶体管(DMOSFETs)和U形场效应晶体管(UMOSFETs) 已经被证明。相比之下,研究横向碳化硅器件的并不多与垂直器件相比来说。最近,在单个芯片上实现高压功率器件和低压电路对横向器件的需求已经增加了。

通常来说,横向碳化硅金属氧化物半导体场效应晶体管被制造在生长在远离轴心的导电衬底上的碳化硅外延层上的。对于4H-SiC,4-off向<1120>基质被广泛使用为了避免多晶型夹杂物。然而,阶梯群聚经常发生在外延生长和高温活化过程中。阶梯群聚使表面粗糙,并导致载流子在表面散射。因此,与远离轴心的晶片相比,同轴晶片在改善电流特性方面具有优势。

然而,仍有可能在同轴晶片上产生多晶型缺陷在外延生长过程中,并且在许多方面消除外延层是优选的。在本文中,4H-碳化硅横向双重注入金属氧化物半导体场效应晶体管已经被设计和制造在同轴高纯度半绝缘(HPSI)衬底上。为了避免上面提到的问题,我们使用了同轴碳化硅衬底。我们的设备显示出与传统设备类似的静态特性。

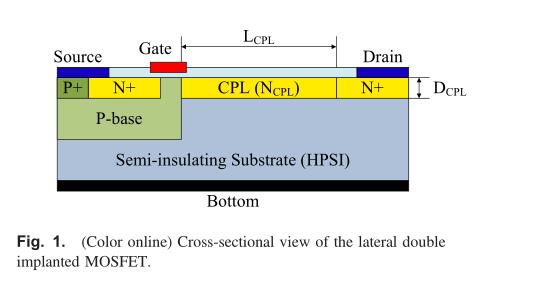

图1显示了我们的设备上的横截面视图。我们使用设备模拟器Silvaco-ATLAS模拟静态特性。如图所示,所提出的器件采用了电流通路层,而不是传统器件中使用的外延层。共面波导区通过离子注入工艺形成。图中的n+和p区也是通过离子注入工艺实现的。共面波导区在获得场效应晶体管特性方面起着重要作用。在正偏时,共面波导用作电流路径,在反偏时,共面波导用于支持击穿电压。没有CPL区,器件的p-基极和n+漏极之间只存在半绝缘层。在这种情况下,由于半绝缘衬底中载流子密度很低,因此正向电流将非常小。

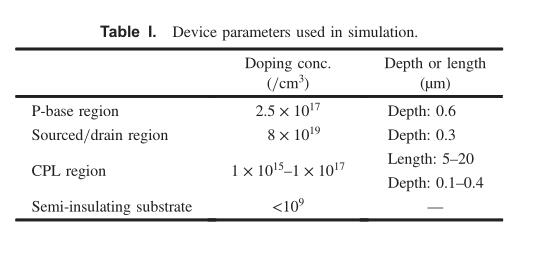

优化共面波导参数(掺杂浓度和深度) 非常重要,为了获得所需的正向和反向特性。为了优化,使用Silvaco-ATLAS进行器件模拟。通过改变共面波导区域的掺杂浓度(NCPL)、深度(DCPL)和长度(长径比)来进行模拟。p-基极和n+源极/漏极的掺杂浓度分别固定在2.5×1017 /cm3和8 × 1019/cm3。使用2微米的沟道长度和55纳米的栅极氧化物厚度。模拟中使用的器件参数如表一所示。

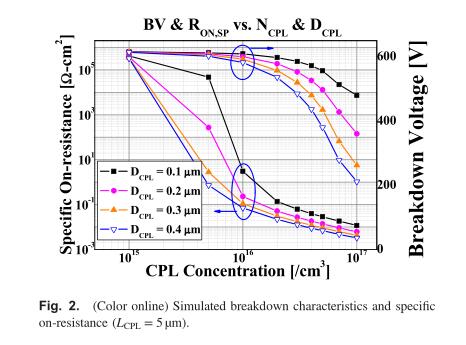

图2显示了所提出器件的模拟特性(击穿电压和特定导通电阻)NCPL和DCPL的函数关系。在该图中,LCPL固定在5 微米。当DCPL在图2中从0.1到0.4 微米变化时,该器件表现出210–615伏的击穿电压。当NCPL和DCPL增加时,击穿电压减小。特别是当NCPL>4×1016/cm3,DCPL> 0.3 μm时,击穿电压急剧下降。在给定的掺杂密度下,深度(DCPL)的增加促使耗尽层中的电场呈三角形,并且最大电场变得更高。这就解释了为什么击穿电压越来越低。图3显示了模拟电压为300伏时,DCPL 为0.1和0.4μm处器件的表面电场分布。如图所示,DCPL为0.4μm的器件的耗尽层没有到达漏极,最大电场较高。如图2所示,当NCPL低于2 × 1016/cm3时,特定导通电阻显著增加。因此,为了获得高击穿电压和较低特定导通电阻,NCPL和DCPL应分别在2 × 1016≤NCPL≤4×1016/cm3和0.2≤DCPL≤0.3 μm的范围内。在器件制作方面,考虑到模拟结果,我们分别采用了NCPL= 2×1016/cm3,DCPL= 0.3 μm。

我们制作了LDIMOSFET器件利用上面的参数。在器件制造中,使用了同轴的HPSI 4H-SiC晶片。进行铝(Al+)和氮(N)的高温(500℃)多次注入,以获得p-基极、N+源极/漏极和CPL区域。对于p-基极区,铝离子注入深度为0.6 μm,注入深度为2.73×1013/cm2。对于共面波导区,在0.3μm深度进行氮注入,注入量为3.38 × 1012/cm2。对于N-源极/漏极(N/N+)和P-源极(Al/P+)分别以2.81×1015 /cm2和2.38×1015 /cm2的量进行欧姆接触的离子注入。考虑到HPSI衬底的激活比(氮:25.2%,铝:27.9%,实验可以证明)和由于HPSI衬底中的深陷阱引起的浓度下降,选择了每个区域的注入量)。共焦平面区域的预期的共焦平面分别为2×1016 /cm3和0.3 μm。

LCPL变化为5至20μm。55纳米厚的栅氧化层通过热生长得到,然后进行一氧化氮处理。在此之后,为栅电极沉积700纳米厚的n+多晶硅。然后沉积200纳米厚的二氧化硅钝化层。钝化后,形成用于欧姆接触的镍硅化物,并在950℃下退火90 s。最后,沉积用于电极的焊盘金属。硅化物n+源极和漏极的接触电阻为6×10-5欧姆·厘米2。为了说明共面波导区的影响,还制作了不含共面波导区的LDIMOSFET。

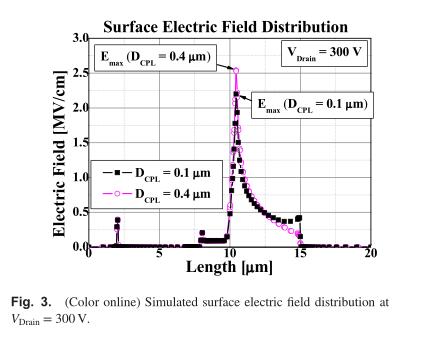

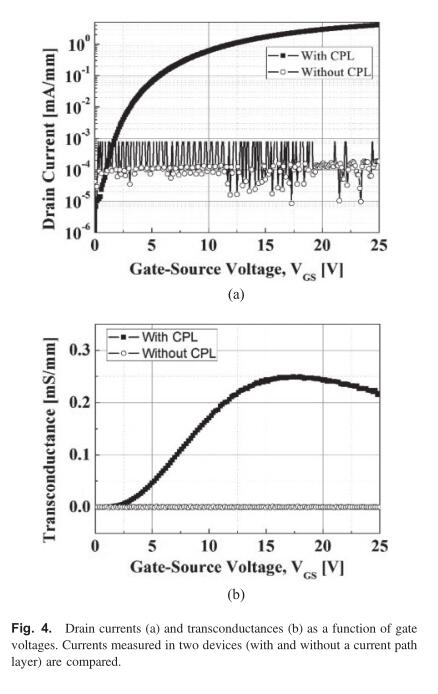

图4显示了在VDrain=1V (LCPL= 5μm,WChannel= 150μm)下测量的器件电流特性。此图显示,只有带CPL的器件才能起到晶体管的作用。该器件的最大跨导(gm)为0.244 mS/mm。器件在最大跨导下的提取沟道迁移率为21.7 cm2·V-1·S-1。

在远离轴心的外延层上制作的铝注入金属氧化物半导体场效应晶体管的迁移率范围是6到9 cm2V-1S-1。相反,在轴外延层上制作的铝注入金属氧化物半导体场效应晶体管的迁移率范围是9到19 cm2V-1S-1,这解释了迁移率的增加是由于较低的表面粗糙度。在我们的器件中,我们使用同轴衬底来避免阶梯群聚引起的表面粗糙度散射,我们观察到的迁移率与在轴上晶片上生长的外延层上实现的器件中测量的迁移率相当。结果表明,我们的迁移率增加与轴上衬底的较低表面粗糙度有关。

使用gm-max方法提取的器件阈值电压为7 V。没有CPL的器件显示出非常低的漏极电流由于高电阻漂移区。在半绝缘衬底中有非常多的的本征深陷阱,例如Z1/2和EH6/7,其在没有共面波导的情况下去除了器件中的自由载流子。图4显示共面波导可以代替LDIMOSFET结构中的外延层。

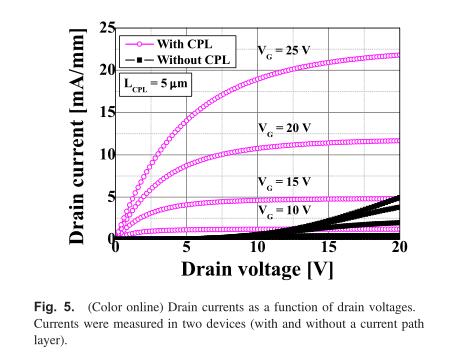

图5显示了测量的漏极电流与漏极电压的函数关系。带CPL的器件表现出晶体管特性(LCPL= 5 μm)。栅极电压从0变为25伏,增量为5伏。在图中,最高漏极电流为22mA/毫米。虽然电流限于薄层(0.3μm深),但器件显示出大电流,这是由于共面波导中有较高载流子浓度。当漏极电压超过10 V时,没有共面波导的器件中的电流有稍微增加。这种小电流增加来自电子的漂移流动,这是由于p-基极和n+漏极之间的高电场。该器件的特定导通电阻为17.2兆欧cm2,电压VG= 25伏,电压VD= 1伏。当LCPL从5增加到20μm时,该器件的特定导通电阻也从17.2增加到89.8兆欧cm2。

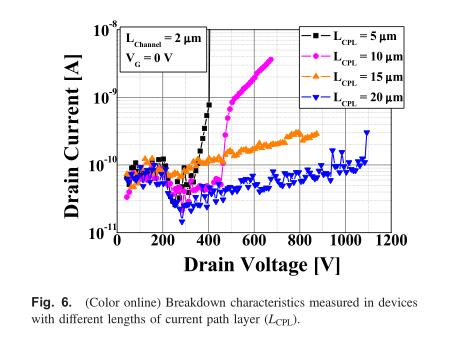

在导电衬底上实现的传统横向器件的最大击穿电压由外延层的厚度和掺杂浓度决定。在漂移区下需要厚的轻掺杂外延层来防止垂直方向上的击穿。换句话说,击穿电压受到垂直方向上耗尽的限制。在我们的器件中,传统器件的外延层和漂移区被半绝缘衬底和共面波导区取代。因为半绝缘衬底的掺杂浓度极低,所以器件的最大击穿电压由CPL区的耗尽决定。因此,我们的器件击穿电压依赖于LCPL,DCPL和NCPL。图6显示了不同LCPL的测量击穿电压。在高漏极电压下,电流会急剧上升,我们将此电压定义为击穿电压。

如图所示,长LCPL显示出较高的击穿电压,在长LCPL = 20 μm的器件中观察到最大电压为1093伏。观察到的击穿电压与长LCPL几乎呈线性关系,这表明在这种配置中整个CPL区域都被耗尽。我们的模拟结果还证实,即使在LCPL= 20 μm的器件中,CPL的整个区域也被耗尽。

最大击穿电压(BV)为1093 V,特定导通电阻(Ron,sp)为89.8兆欧·cm2在LCPL= 20 μm时。本文所制备器件的品质因数(BV2/Ron,sp)为13.3 MW/cm2。使用场板可以提高器件的击穿电压。由于p-基极和n+漏极底角的二维效应,场拥挤出现在导致场尖峰的边缘,因此击穿电压降低。这可以通过使用放置在栅极和漏极顶部的场板来避免。

器件的特定导通电阻可以通过采用RESURF原理来改善。通过模拟可以找到在共面波导区域中具有较高掺杂的全耗尽的参数。场板和RESURF原理的影响正在研究中。

总之,4H-SIC场效应晶体管已经被设计和制造在同轴HPSI衬底上,而不使用外延层。我们证实,共面波导可以取代传统器件的外延层,而不会牺牲它们的性能。测得的有效沟道迁移率为21.7 cm2·V-1·S-1,获得了高击穿电压和特定导通电阻。当LCPL= 20μm时,我们的器件显示出89.8兆欧·cm2的特定导通电阻,阈值电压为7 V。测得的最大击穿电压为1093 V,品质因数(BV2/Ron,sp)为13.3 MW/cm2。这些结果表明,在没有外延层的半绝缘衬底上制作的4H-SiC LDIMOSFET是功率集成电路的一个有前途的候选器件。

本文来自博客园,作者:shihao_Yang,转载请注明原文链接:https://www.cnblogs.com/Yang-shihao/p/14474685.html