AXI4协议

AXI4协议

参考资料:

1、arm axi官方文档:https://developer.arm.com/documentation/ihi0022/latest?_ga=2.145967412.1021591712.1586156324-1048184626.1580228297

<IHI0022C_amba_axi_v2_0_protocol_spec.pdf>、<IHI0022H_c_amba_axi_protocol_spec.pdf>

<IHI0051A_amba4_axi4_stream_v1_0_protocol_spec.pdf>

2、xilinx axi文档:UG1037<Vivado AXI Reference>、UG934<AXI4-Stream Video IP and System Design Guide>

一、AXI4总线简介

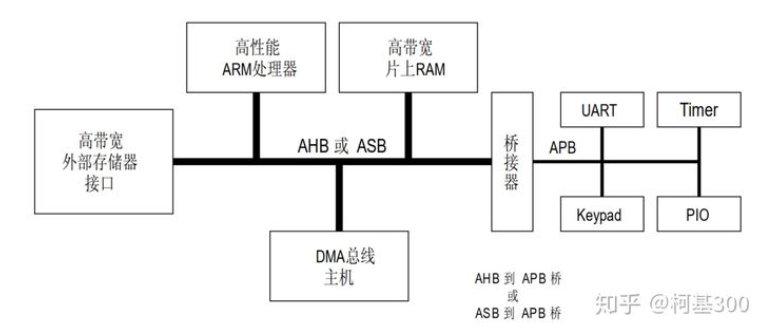

AXI是高性能、高带宽、低延迟的片内总线。AXI总线是在AMBA3.0的协议中增加的,AMBA是由ARM公司研发推出的一种高级微控制器总线架构(Advanced Microcontroller Bus Architecture)。其中AMBA包含了四种不同的总线标准,分别是:AHB、ASB、APB、AXI。AHB是高级高性能总线,通常用于CPU和高性能设备之间的交互ASB常用于高性能系统模块间的交互,APB是高级外设总线,通常和AHB相连接,来访问一些低速的外设。如STM32中就AHB、ASB、APB总线。有下图展示了一个典型的基于AMBA的微控制器架构。

AXI4总线分为三种:

图1.1 axi总线读事务

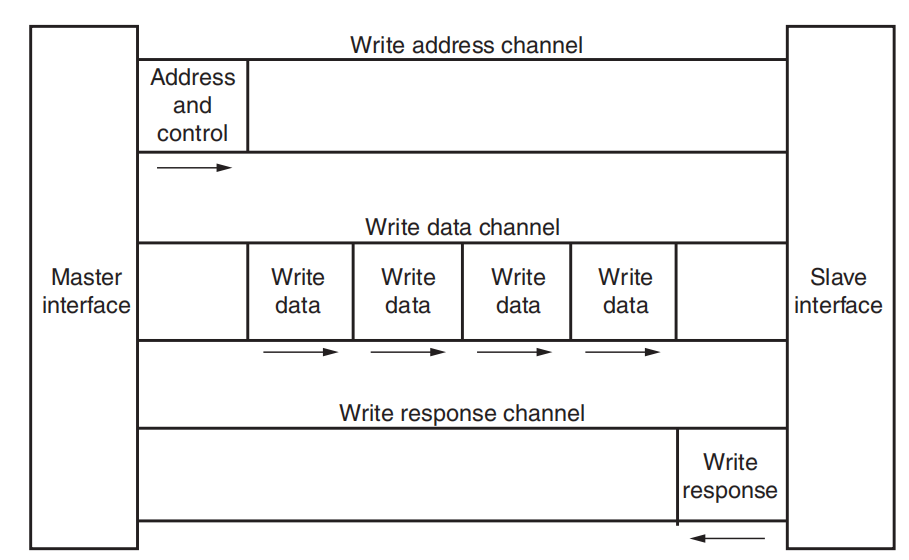

图1.2 axi总线写事务

二、AXI4总线接口信号及时序

2.1 AXI总线接口定义

AXI总线的写地址信号以AW开头,写数据通道以W开头,写响应通道以B开头,读地址通道以AR开头,读数据通道以R开头。

表2.1 写地址通道信号

表2.2 写数据通道信号

表2.2 写响应通道信号

表2.4 读地址通道信号

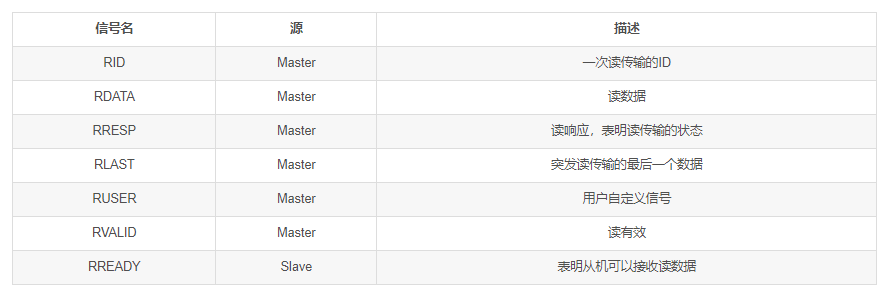

表2.5 读数据通道信号

2.2 握手协议

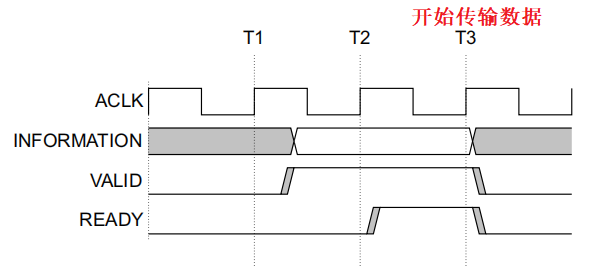

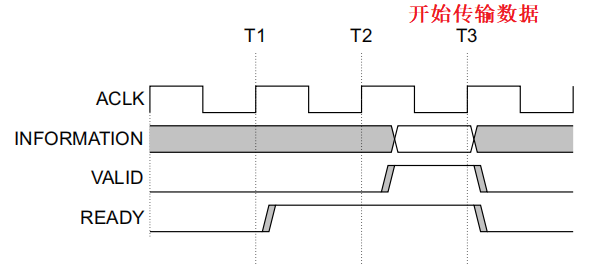

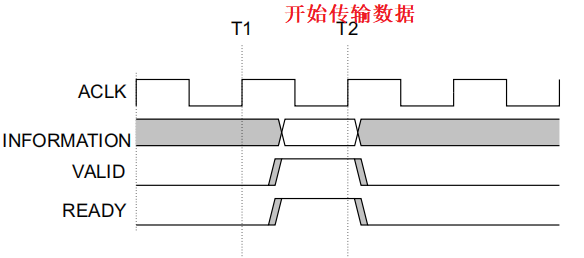

axi主从机之间在正式传输数据之前需要进行握手,axi的握手是通过VALID和READY信号完成的,每个通道都有这两个信号。VALID信号由传输发起方产生,表示传输发起方已经准备好数据,可以开始传输。READY信号有传输的接受放产生,表示接受方已经准备好接受数据,只有VALID和READY信号都为高电平时,才能进行数据传输。握手情况分为三种,分别是VALID先高然后READY变高、READY先高然后VALID变高、READY和VALID同时变高。如下图所示:

图2.1 VALID先高然后READY变高

图2.2 READY先高然后VALID变高

图2.3 READY和VALID同时变高

2.3 读/写地址信号

1、突发长度

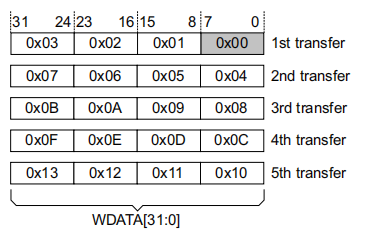

ARLEN 和 AWLEN分别是读地址通道和写地址通道的突发长度,表示读事务和写事务传输总共有多少个传输事务。axi4这两个信号有8位,可见一次最大读写事务的数据大小是256事务。

ARLEN[7:0]: 读事务的事务个数

图 2.4 突发长度和大小

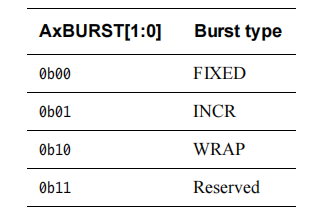

表2.5 突发类型

FIXED:固定突发类型,表示主机对从机的读写地址是固定的。

NNCR:自增突发类型,主机给从机一个读写的首地址,从机根据首地址和突发大小自动增加。

WRAP:回环突发类型,这种类型与自增突发类型相似,不一样的是回环突发类型在地址自增到一个上线地址后,会回到低地地址重新开始。

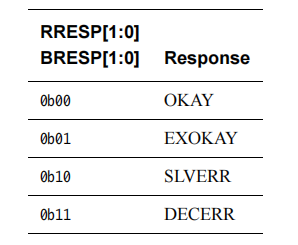

4、读/写响应

AXI的写响应是个单独的通道,读响应包含在读数据通道中。RRESP 和 BRESP信号是读写响应的主要信号,表示读写响应的状态。如表2.6所示:

OKAY:正常访问成功

EXOKAY:独占访问成功

SLAVERR:从设备给主设备返回的错误信号

DECERR: 解码错误,在axi互联系统中,通常是主机反问了一个不存在的从设备地址

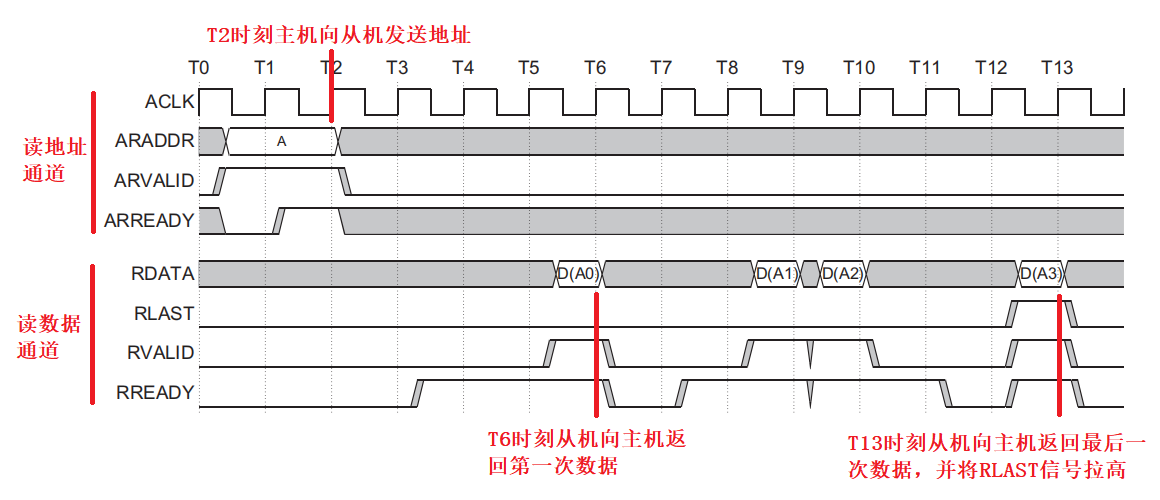

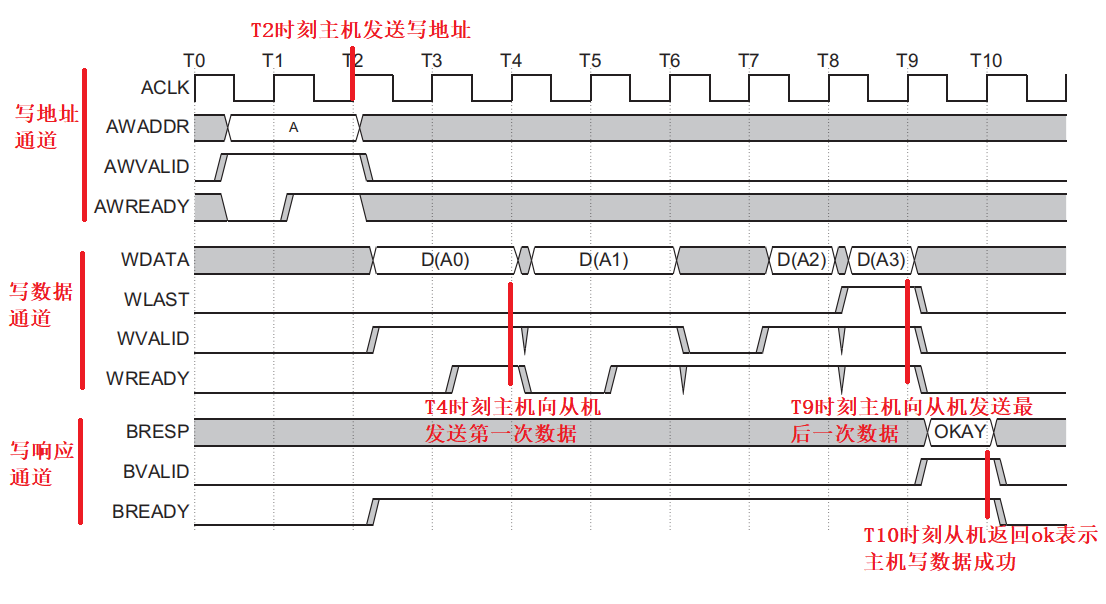

2.4、AXI4读写时序

axi总线主机和从机基本的读写时序如下图所示:

图2.5 读数据时序

图2.6 写数据时序

三、AXI4-Stream接口信号及时序

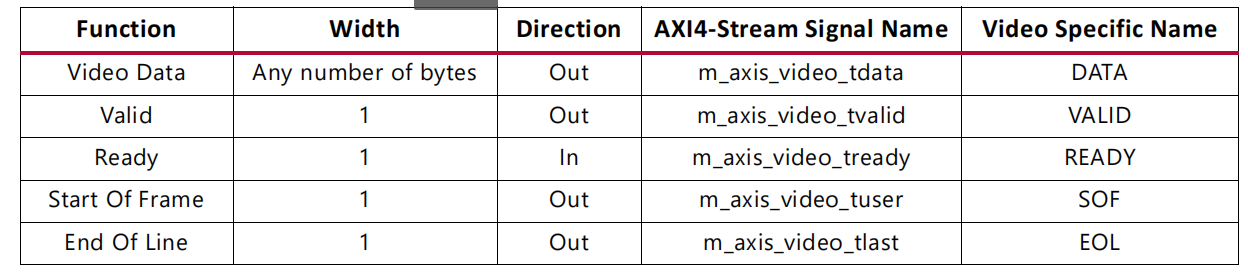

3.1 AXI4-Stream接口信号定义

图3.1 AXI4-Stream接口信号定义

3.2 AXI4-Stream握手协议

AXI4-Stream握手协议与AXI4的握手协议一致

3.3 AXI4-Stream信号时序

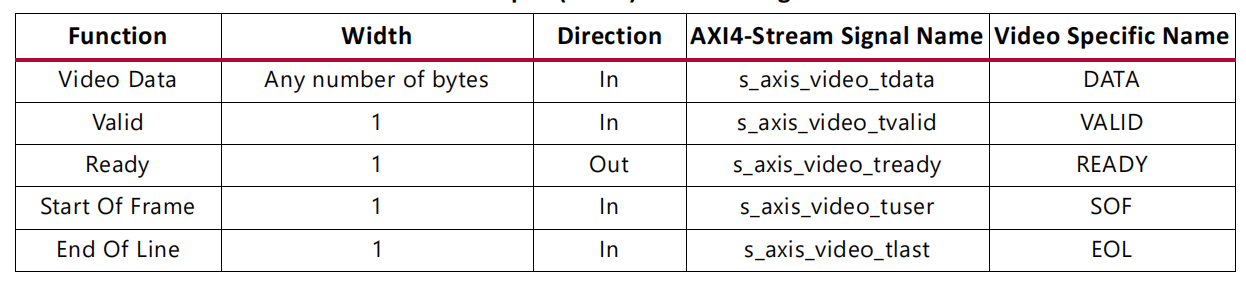

下面以xilinx的AXI4-Stream接口传输视频流为例说明AXI4-Stream接口时序。xilinx的AXI4-Stream主从机接口如图3.2和图3.3所示,图中并没有给出全部接口说明。

图 2.3 从机接口

图2.4 主机接口

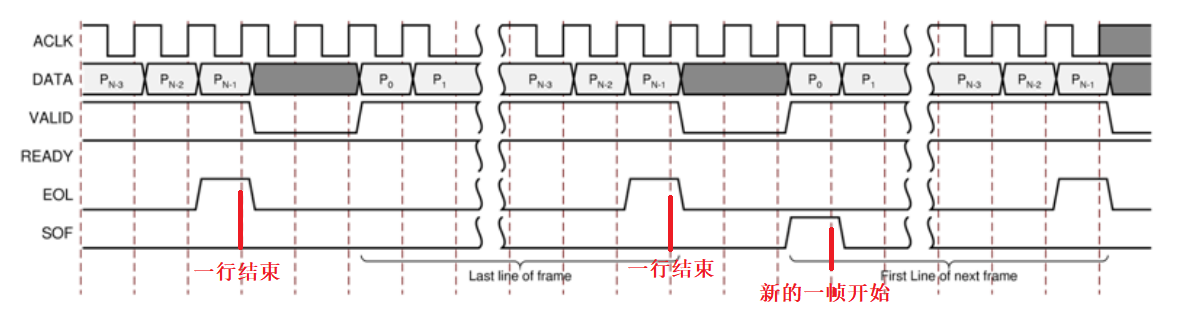

从图中可以看出,AXI4-Stream的TUSER和TLAST接口在xilinx中定义为视频帧的开始信号和视频行的结束信号。如图2.5所示:

图2.5 EOL信号与SOF信号

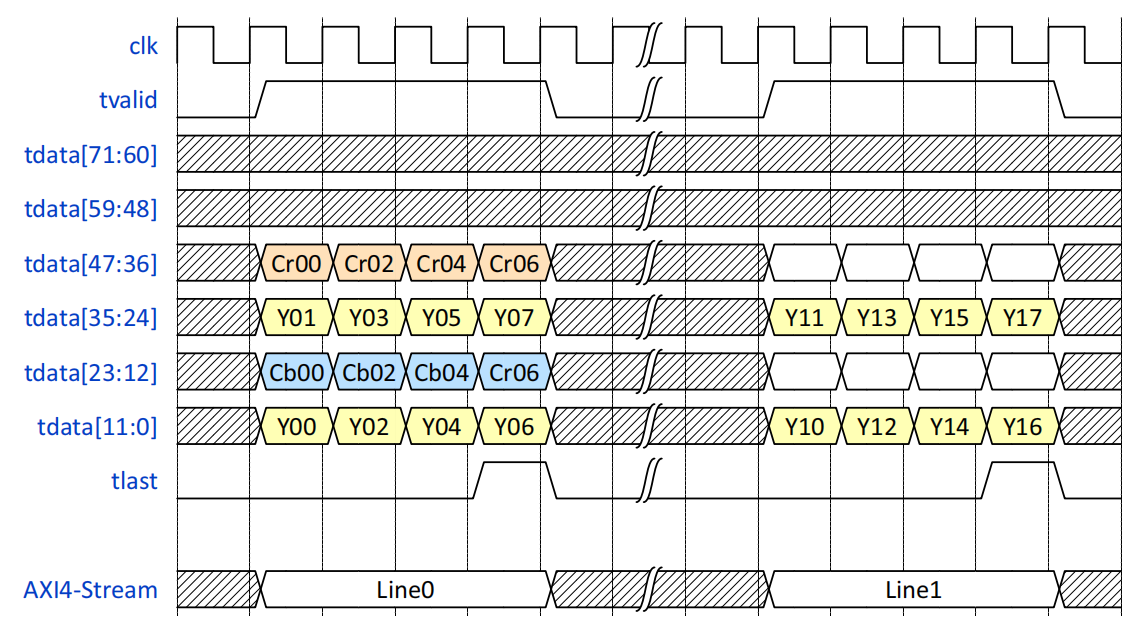

传输YUV420,每个时钟传输两个像素实现如图2.6所示:

图2.6 YUV420,每个时钟两个像素

浙公网安备 33010602011771号

浙公网安备 33010602011771号