关于 AXI协议的学习解释说明

AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持Outstanding传输访问和乱序访问,并更加容易进行时序收敛。

AXI的特点

单向通道体系结构。信息流只以单方向传输,简化时钟域间的桥接,减少门数量。当信号经过复杂的片上系统时,减少延时。

支持多项数据交换。通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

独立的地址和数据通道。地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。

增强的灵活性。AXI技术拥有对称的主从接口,无论在点对点或在多层系统中,都能十分方便地使用AXI技术。

AXI总线还定义了在进出低功耗节电模式前后的握手协议,规定如何通知进入低功耗模式,何时关断时钟,何时开启时钟,如何退出低功耗模式。这使得所有IP在进行功耗控制的设计时,有据可依,容易集成在统一的系统中。

总之,AXI 能够使SoC 以更小的面积、更低的功耗,获得更加优异的性能。AXI获得如此优异性能的一个主要原因,就是它的单向通道体系结构。单向通道体系结构使得片上的信息流只以单方向传输,减少了延时。

AXI的工作模式

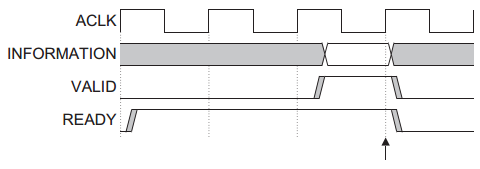

A. 握手机制

AXI所采用的是一种READY,VALID握手通信机制,即主从模块进行数据通信前,新根据操作对各所用到的数据、地址通道进行握手。主要操作包括传输发送者A等到传输接受者B的READY信号后,A将数据与VALID信号同时发送给B。根据READY和VALID拉高的先后顺序,可分为如下3种情况:

Valid before Ready handshake

Ready before Valid handshake

Valid with Ready handshake

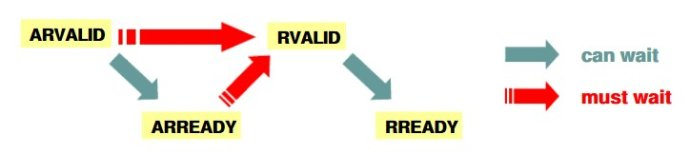

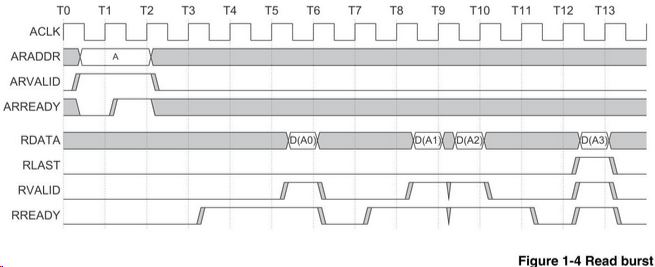

每个channel内的valid和ready之间没有严格的先后顺序,但是channel间的valid和ready信号有依赖关系。对于读操作,spec要求读data必须出现在读addr之后,因此读操作的两个channel之间存在如下的依赖关系,即必须等到ARVALID和ARREADY同时为High后,RVALID才能拉高。

Read transaction handshake dependencies

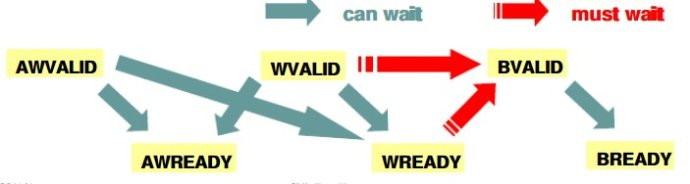

对于写操作,addr和data两个channel之间不存在依赖关系,但是只能等最后一次transfer结束后,才能拉高BVALID。从下图中看不出AWVLAID, AWREAY与BVALID之间的关系,但是,隐含条件是slave只有接收到addr和data后,才能做出响应,因此AWAVLID, AWREADY为High,且最后一次transfer结束后才能拉高BVALID.

Write transaction handshake dependencies

B. axi总线的五个通道:

- 读地址通道,包含ARVALID, ARADDR, ARREADY信号;

- 写地址通道,包含AWVALID,AWADDR, AWREADY信号;

- 读数据通道,包含RVALID, RDATA, RREADY, RRESP信号;

- 写数据通道,包含WVALID, WDATA,WSTRB, WREADY信号;

- 写应答通道,包含BVALID, BRESP, BREADY信号;

另外,还有两个global signal,ACLK,ARESETN信号;

其中ACLK为axi总线时钟,仅上升沿有效,ARESETN是axi总线复位信号,低电平有效,异步复位同步释放;所有master和slave共用ACLK和ARESETn。

READY与VALID是对应的通道握手信号;WSTRB信号为1的bit对应WDATA有效数据字节,WSTRB宽度是32bit/8=4bit;BRESP与RRESP分别为写回应信号,读回应信号,宽度都为2bit,‘h0代表成功,其他为错误。

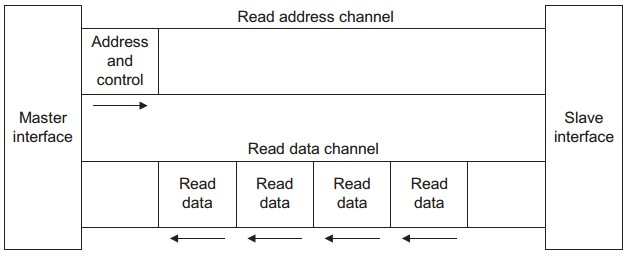

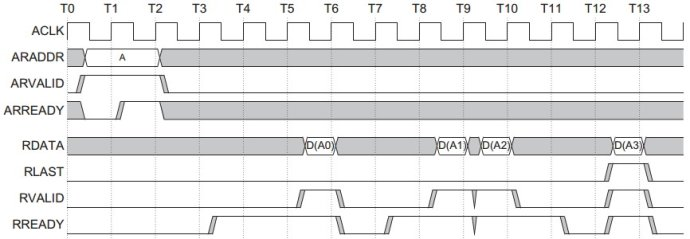

a. 读操作:

顺序

- 主与从进行读地址通道握手并传输地址内容,

- 读数据通道握手并传输所读内容以及读取操作的回应。

对于读操作,slave必须先知道master想要读取的地址,因此,slave必须先接收到command后再回数据。normal的操作如图所示:

Channel architecture of READ TRANSACTION

READ Burst

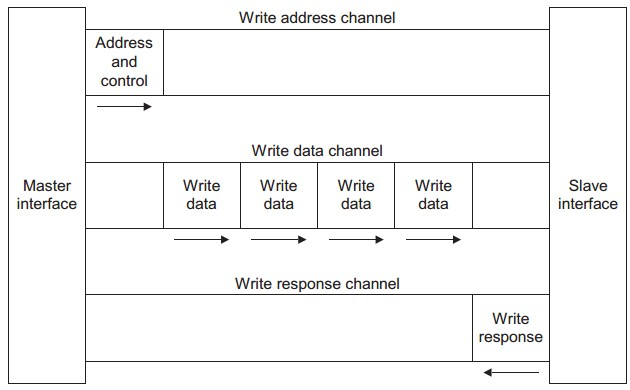

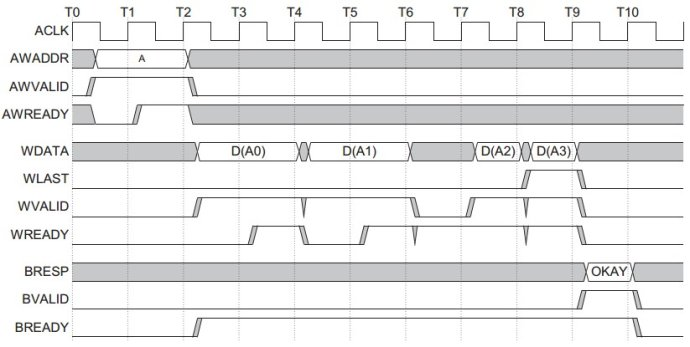

b. 写操作:

顺序

- 主与从进行写地址通道握手并传输地址内容,

- 写数据通道握手并传输所读内容,

- 写回应通道握手,并传输写回应数据。

对于写操作,command和数据都是master发给slave的,因此command和data没有顺序,可以先发command,再发data,也可以先发data,在发送data过程中发送command。normal的操作如图所示:

Channel architecture of writeTRANSACTION

Write Burst

什么是支持 outstanding

Outstanding 支持的多少是需要设定的。举个例子,如果 outstanding设为5,对于写来说,可以连续发送5个写操作而不用等待bresponse的响应,否则必须等待有一个responese回来才能发送下一个写操作,对于读来说,是通过rlast信号来看是否有respone,也类似于写操作;也就是说,如果没有respone的操作超过了outstanding的值,则会通过拉低响应的ready信号,从而不能发送有效操作;

三、 各个通道的时序关系:

1、读地址通道:

output [0: 0] master_axi_arid; // axi read command ID

output [35: 0] master_axi_araddr; // axi read command address

output [3:0] master_axi_arlen; // axi encoded read command length

output [2:0] master_axi_arsize; // axi encoded read command size

output [1:0] master_axi_arburst; // axi read command burst type.

output [1:0] master_axi_arlock; // axi atomic access indicator

output [3:0] master_axi_arcache; // axi cache control os for the read.

output [2:0] master_axi_arprot; // axi read command protection type.

output master_axi_arvalid; // axi read command valid indicator.

input master_axi_arready; // indicates that axi is ready to accept the read command.

2、读数据通道:

Input [0:0] master_axi_rid; // axi read data ID.

Input [255:0] master_axi_rdata ; // axi read data.

Input [1:0] master_axi_rresp ; // aix read data response a response is sent with each burst indicating the status of the burst.

input master_axi_rlast; // Indicates that this is the final world of the data for the command.

input master_axi_rvalid; // axi read data valid indicator.

output master_axi_rready; // indicates that the axi master is ready to accept read data.

4.写地址通道:

output [ 0: 0] master_axi_awid; // axi write command ID

output [35: 0] master_axi_awaddr; // axi write command address

output [ 3:0] master_axi_awlen; // axi encoded write command length

output [ 2:0] master_axi_awsize; // axi encoded write command size

output [ 1:0] master_axi_awburst; // axi write command burst type.

output [ 1:0] master_axi_awlock; // axi atomic access indicator

output [ 3:0] master_axi_awcache; // axi cache control os for the read.

output [ 2:0] master_axi_awprot; // axi read command protection type.

output master_axi_awprot; // axi read command valid indicator.

input master_axi_awready; // indicates that aix is ready to accept the read command.

5.写数据通道:

output [ 0:0] master_axi_wid; // axi write data ID.

output [255:0] master_axi_wdata ; // axi write data.

output [ 31:0] master_axi_wstrb ; // axi write data strobe.

output master_axi_wlast; // Indicates that this is the final world of the data for the command.

output master_axi_wvalid; // axi write data valid indicator.

input master_axi_0_wready; // indicates that the axi master is ready to accept write data.

6.写响应通道:

input [0:0] master_axi_bid; // AXI write respone ID.

input [1:0] master_axi_bresp; // AXI write respone A responese is sent for the entire burst.

input master_axi_bvalid; // AXI write response valid indicator.

input master_axi_bready; // Indicates that the AXI master is ready to accepta write respone.

7.写地址、写数据、写响应的时序关系

四.传输顺序说明

AXI 协议可以完成按照固定顺序的传输操作,其通过接口给每一个传输操作一个ID标记,协议要求具有相同的ID标记的传输要按照指定顺序完成,但是不同的ID的传输可以不按照制定的顺序进行传输; 完成乱序传输的能力意味着可以完成向快速内存的传输,不用等待之前向慢速内存的传输,这样可以提高系统的性能,减少不必要的等待时间;