Verilog——入门进程学习(三)

Verilog HDL语言的运算符范围很广,其运算符按其功能可分为以下几类:

-

算术运算符(+,-,*,/,%)

-

赋值运算符(=,<=)

-

关系运算符(>,<,>=,<=)

-

逻辑运算符(&&,||,!)

-

条件运算符(?)

-

位运算符(,|,^,&,^)

-

移位运算符(<<,>>)

-

连接运算符({ })

-

其它

在Verilog HDL语言中运算符所带的操作数是不同的,按其所带操作数的个数运算符可分为三种:

-

单目运算符(unary operator):可以带一个操作数,操作数放在运算符的右边。

-

二目运算符(binary operator):可以带二个操作数,操作数放在运算符的两边。

-

三目运算符(ternary operator):可以带三个操作,这三个操作数用三目运算符分隔开。

算术运算符:

算术的运算都比较简单,这里不再赘述。这里需要注意的两点是:

- 算术表达式结果的长度由最长的操作数决定。在赋值语句下,算术操作结果的长度由操作符左端目标长度决定。

- 有符号数与无符号数

a = 4’b1111 //15

b = 3’b011 //3

计算a*b,普通来算结果是101101,但是在verilog中要求结果的位宽要和操作数中最长的那一个等宽,也就是要和a等宽,所以高位截断,运算结果是4’1101。

关系运算符:

- < 、 > 、 <= 、 >= 如果关系运算结果是假的,则返回值是0,如果声明的关系是真的,则返回值是1。 如果操作数中有一位为X或Z,那么结果为X。

- 如果操作数长度不同,长度较短的操作数在最重要的位方向(左方)添0补齐。

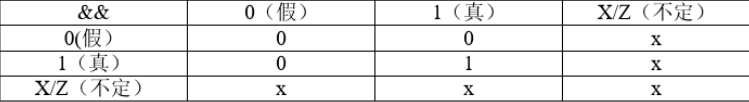

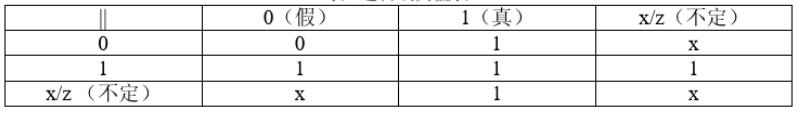

逻辑运算符:

条件运算符:

条件操作符是根据其条件表达式的值来进行选择表达式,形式如下所示:

compare?A:B;

如果compare为真(即值为1,),选择A。反之选择B。其结果是按照以下逻辑A和B按位操作的值:0与0得0,1与1得1,其余情况为X。

位运算符:

按位取反~ 、按位与 & 、按位或 | 、按位异或 ^ 、按位同或 ^~

在不同长度的数据进行位运算时,系统会自动的将两个数右端对齐,位数少的操作数会在相应的高位补0,一时的两个操作数按位进行操作。

移位运算符:

<< 、 >> a>>n其中a代表要进行移位的操作数,n代表要移几位。这两种移位运算都用0来填补移出的空位。

a >> n;//a右移n位

a << n;//a左移n位

a代表要进行移位的操作数,n代表要移几位。这两种移位运算都用0来填补移出的空位。

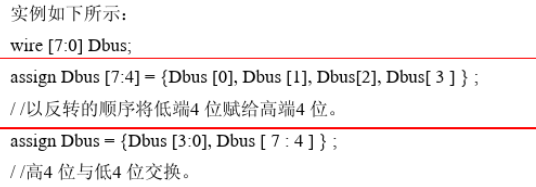

连接运算符:

用这个运算符可以把两个或多个信号的某些位拼接起来进行运算操作。其使用方法如下:

{expr1,expr2,..,..,exprN}

浙公网安备 33010602011771号

浙公网安备 33010602011771号