Verilog——入门进程学习(二)

标识符:

- Verilog语言本身区分大小写,对于Verilog语言本身来说,其关键字都是小写,如always语句等等。

- 标识符用于定义模块名、端口名、信号名等一系列需要定义的。对于Veriolg来说,其标识符可以是任意的一组字母、符号、数字以及和下划线的组合,但是在这里要注意的一点是,标识符的第一位字符必须是字母或者下划线。

注释:

两种注释方式:

- 以 /* 开始,*/ 结束,此类注释可以扩展到多行。

- 以 // 开始至本行结束都是注释语句,不可扩展到多行。

数字值集合:

值集合:

在Verilog语言中,规定了四种基本的值类型:

- 0:逻辑0或假。

- 1:逻辑1或真。

- X:未知值。

- Z:高阻。

在语句中,X和Z是不区分大小写的,即0x1z与0X1z值是相同的。

常量:

常量在Verilog中可划分为三大类:整型、实型、字符串型。

整型:

整数型可以按照如下的两种方式进行书写:

- 简单的十进制数格式:这种形式的整数定义为带有一个可选的“+”或“-”操作符的数字序列。

- 基数格式:如同 [size]'base value

size定义以位计的常量的位长;

base则表示进制,有以下几种表示方式:

- 二进制(b或B)

- 八进制(o或O)

- 十进制(d或D)

- 十六进制(h或H)

value是基于base的值得数字序列。值X和Z以及十六进制中的A到F不区分大小写。

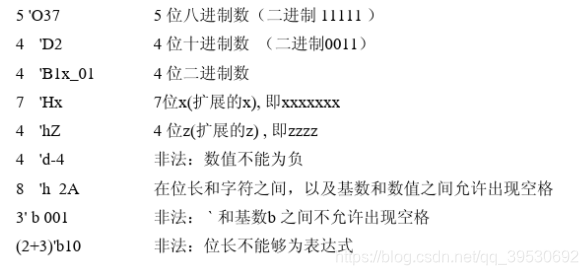

实例如图:

假设当定义的长度比为常量指定的长度长,通常在左边填0补位。但是如果数最左边一位为x或z,就相应地用x或z在左边补位。

如:

- 10‘b10 左边添0占位,0000000010

- 10’bx0x1 左边添x占位,xxxxxxx0x1

实型:

支持小数或者科学型表示,例如:3.14 2.0e3

字符串型:

字符串是双引号内的字符序列。字符串不能分成多行书写。用一串8位二进制ASCⅡ码的形式表示,每一个8位二进制ASCⅡ码代表一个字符。例如:字符串 “ab” 等价于16’h5758。如果字符串被用作Verilog表达式或复制语句的操作数,则字符串被看做无符号整数序列。变量需要8*n位,n表示字符串的长度。

/*字符串变量的声明。*/

//存储12个字符的字符串“Hello China!”需要8*12(即96位)宽的寄存器。

reg [8*12:1] str1;

initial

begin

str =“Hello China!”;

end

数据类型:

在Verilog中,主要是两种数据类型:线网类型(net type)和寄存器类型(reg type)

线网类型:

- 线网型还有其他数据类型,包括 wand,wor,wri,triand,trior,trireg 等。这些数据类型用的频率不是很高,这里不做介绍。在Verilog中,wire是最常用的线网类型。

- wire 类型表示硬件单元之间的物理连线,因此不存储逻辑值,由其连接的器件输出端连续驱动。如果没有驱动元件连接到 wire 型变量,缺省值一般为 “Z”。

- 信号没有定义数据类型时,缺省为wire类型。

- tri其实和wire在用法上是一模一样的,不过有时候,我们需要定义一些会被三态门驱动的硬件连线,用tri来命名会让代码更具有可读性,让人一看就知道这根连线上会出现Z状态。

寄存器类型:

- Verilog中规定,凡是在程序块中被赋值的变量,都必须是寄存器类型的。(程序块:例如always块)

- reg是最常用的寄存器类型,寄存器类型通常用于对存储单元的描述,如D型触发器、ROM等。存储器类型的信号在某种出发机制下分配了一个值,在分配下一个值之时保留原值。但必须注意的是,reg类型的变量,不一定都是存储单元。

reg [3:0] counter ; //声明4bit位宽的寄存器counter

reg [0:31] data ; //声明32bit位宽的寄存器变量data, 最高有效位为0,建议对于数组类型,按照降序方式进行,如[31:0]

reg A; //1位寄存器。

浙公网安备 33010602011771号

浙公网安备 33010602011771号