Verilog——入门进程学习(一)

数字电路设计方法:

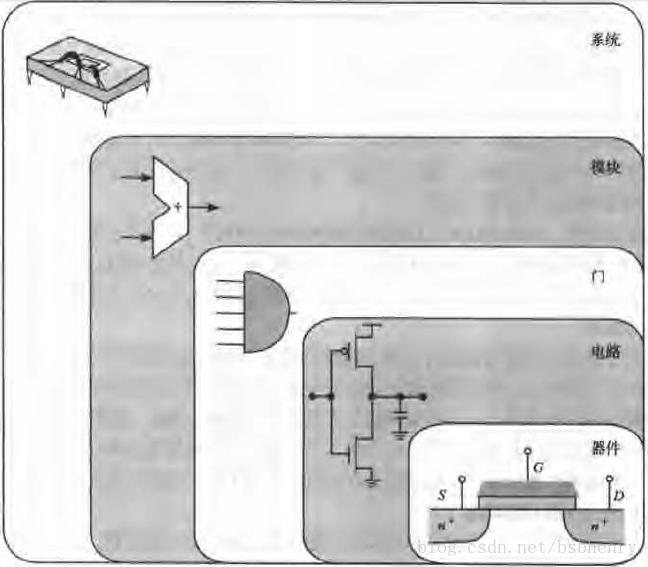

对于数字电路设计从上至下可分为大概以下几个层次:

- 算法级设计:利用高级语言及一些系统分析工具对设计从系统方面的算法级方式进行描述,其不需要包含时序信息。

- RTL(逻辑)设计:用数据流在寄存器间传输的模式来对设计进行描述。

- 门级:使用与、或、非们等门级之间的连接来对设计进行描述。

- 开关级:使用晶体管和寄存器及他们之间的连线关系来对设计进行描述。

算法级是高级的建模,一般旨在对特大型设计或有较复杂的算法时使用,特备是通讯方面的一些系统,通过算法级的建模来保证设计的系统性能。在算法级通过之后,再把算法级用RTL级进行描述。门级一般对小型设计可适合。开关级一般是在版图级进行。

上面是华为自己对数字电路的设计进行的划分,但是对于我们来说,以下这种还是众所周知的设计层次,可划分为器件、电路、门、功能模块、系统。

Verilog语言具有下述描述能力:

设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延4和波形产生机制。

主要功能:

- 基本逻辑门,例如and、or 和nand等都内置在语言中。

- 开关级基本结构模型,例如pmos和Inmos等也被内置在语言中。

- Verileg HDL中有两类数据类型,分别为线网数据类型、寄存器数据类型。线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

- 能够描述层次设计,可使用模块实例结构描述任何层次。

- 设计的规模可以是任意的:语言不对设计的规模(大小)施加任何限制。

- Verilog HDL不再是某些公司的专有语言而是IEEE标准。

- 人和机器都可阅读Verilog语言,因此它可作为EDA的工具和设计者之间的交互语言。

- 设计能够在多个层次上加以描述,从开关级、门级、寄存器传送级(RT L )到算法级。

- 能够使用内置开关级原语在开关级对设计完整建模。

- 同一语言可用于生成模拟激励和指定测试的验证约束条件,例如输入值的指定。

- Verilog HDL 能够监控模拟验证的执行,即模拟验证执行过程中设计的值能够被监控和显示。这些值也能够用于与期望值比较,在不匹配的情况下,打印报告消息。

- 在行为级描述中,Verilog HDL 不仅能够在RT L 级上进行设计描述,而且能够在体系结构 级描述及其算法级行为上进行设计描述。

- 能够使用门和模块实例化语句在结构级进行结构描述。

- 对高级编程语言结构,例如条件语句、情况语句和循环语句,语言中都可以使用。

HDL的建模方式:

在FPGA设计中,有四种HDL的建模方式,主要有结构化描述方式、数据流描述方式、行为描述方式和混合设计描述:

-

结构化描述方式:结构化的建模方式就是通过对电路结构的描述来建模,即通过对器件的调用(HDL概念为例化),并使用线网来连接各器件的描述方式。这里的器件包括Verilog HDL的内置门器件如与门and,异或门xor等,也可以是用户的一个设计。结构化的描述方式反映了一个设计的层次关系。

-

数据流描述方式:数据流的建模方式就是通过对数据流在设计中的具体行为的描述的来建模。最基本的机制就是用连续的赋值语句。在连续的赋值语句中,某个值被赋值给某个线网变量(信号),语法如:assign [delay] net_name = expression; (assign #2 A = B;)。在数据流描述方式中,还必须借助于HDL提供的一些运算符,如按位逻辑运算符:逻辑与(&),逻辑或(|)等。

-

行为描述方式:行为方式的建模是指采用对信号行为级的描述(不是结构级的描述)的方法来建模。在表示方面,类似数据流的建模方式,但一般是把用initial块语句或always块语句描述的归为行为建模方式。行为建模方式通常需要借助一些行为级的运算符如加法运算符(+),减法运算符(-)等。

-

混合设计描述:在实际的设计中,往往是多种设计模型的混合。一般地,对顶层设计,采用结构描述方式,对低层模块,可采用数据流、行为级或两者的结合。

浙公网安备 33010602011771号

浙公网安备 33010602011771号