具有快表的地址变换机构

1.操作系统的概念与功能2.操作系统的特征3.操作系统的发展与分类4.操作系统的运行机制5.中断和异常6.系统调用7.计算机系统体系结构8.操作系统引导 (Boot)9.虚拟机10.进程的概念、组成、特征11.进程的状态与转换、进程的组织12.进程控制13.进程通信14.线程的概念、作用和属性15.线程的实现方式和多线程模型16.线程的状态与转换、组织与控制17.调度的概念与层次18.进程调度的时机、方式、切换与过程19.闲逛进程20.调度算法的评价指标21.调度算法22.调度算法(一)23.调度算法(二)24.调度算法(三)25.进程同步与进程互斥26.进程互斥的软件实现方法27.进程互斥的硬件实现方法28.互斥锁29.信号量机制30.信号量实现进程互斥、同步、前驱关系31.生产者-消费者问题32.多生产者-多消费者问题33.吸烟者问题34.读者-写者问题35.哲学家进餐问题36.管程37.死锁38.死锁的处理策略39.(一)预防死锁40.(二)避免死锁41.(三)死锁检测和解除42.内存的基础知识43.内存管理的概念44.覆盖与交换45.连续分配管理方式46.动态分区分配算法47.基本分页存储管理的基本概念48.基本地址变换机构

49.具有快表的地址变换机构

50.两级页表51.基本分段存储管理方式52.段页式管理方式53.虚拟内存的基本概念54.请求分页管理方式55.页面置换算法56.页面分配策略57.内存映射文件58.初识文件管理59.文件的逻辑结构60.文件目录61.文件的物理结构(文件分配方式)62.逻辑结构与物理结构63.文件存储空间管理64.文件的基本操作65.文件共享66.文件保护67.文件系统的层次结构68.文件系统的全局结构(布局)69.虚拟文件系统&文件系统挂载(安装)70.IO设备的概念和分类71.IO控制器72.IO控制方式73.IO软件层次结构74.IO应用程序接口&设备驱动程序接口75.IO核心子系统76.假脱机技术(SPOOLing技术)77.设备的分配与回收78.缓冲区管理79.磁盘的结构80.磁盘调度算法81.减少延迟时间的方法82.磁盘的管理83.固态硬盘具有快表的地址变换机构

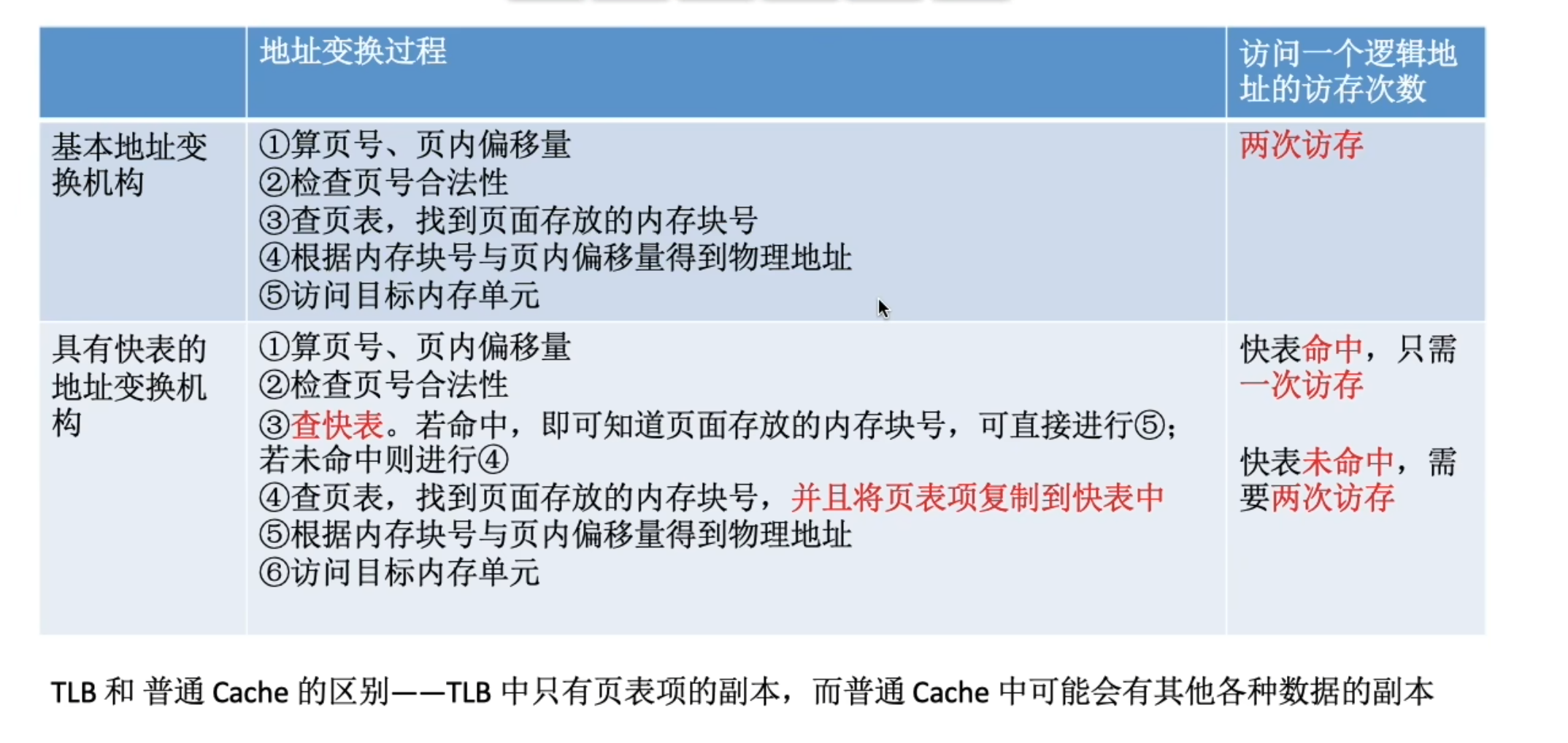

理解:是对基本地址变换机构的优化,减少访存次数来提高效率。

一、快表的概念

快表,又称联想寄存器(TLB ,translation lookaside buffer),是一种访问速度比内存快很多的高速缓存 (TLB 不是内存,类比 Cache ,但与 Cache 有所不同) ,用来存放最近访问的页表项的副本,可以加速地址变换的速度。与此对应,(上两节提到的与页面同样放在内存中的页表)内存中的页表常称为慢表。

理解:TLB 作用在逻辑地址到物理地址的转换阶段,而 Cache 作用在得到物理地址后要访存存取数据的阶段。二者都是高速缓存,设置的目的都是为了减少访存次数,提高机器效率。TLB 中只有页表项的副本,而普通 Cache 存放的是具体的指令(指令Cache)或数据(数据Cache)副本。

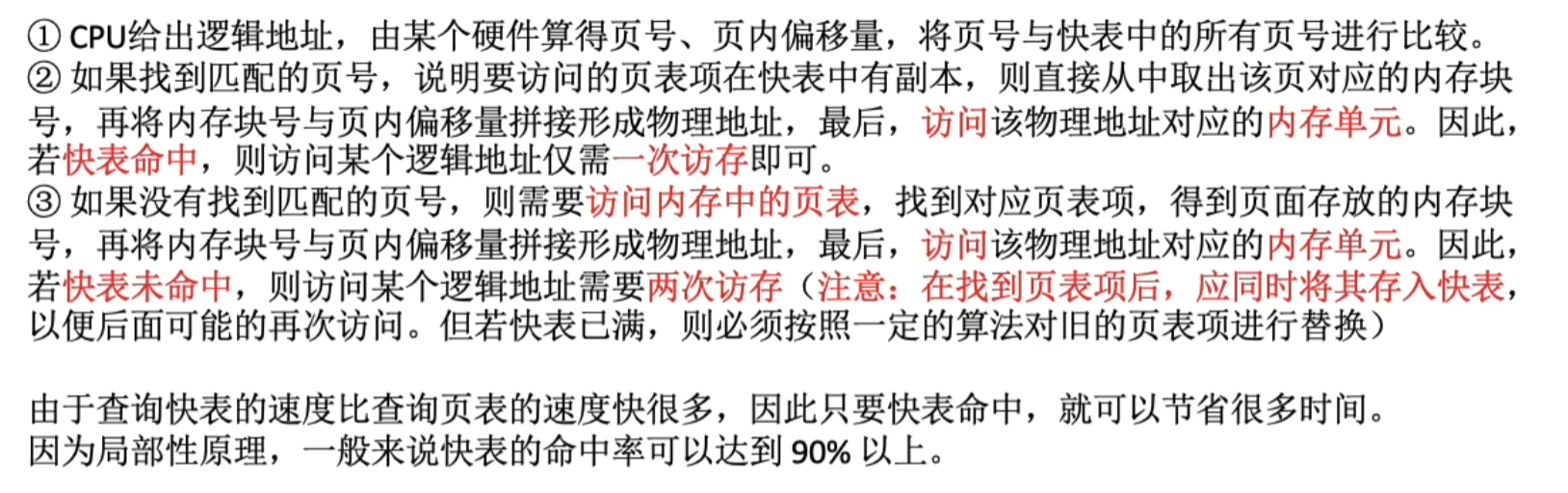

二、引入快表后的地址变换过程

——补充例题(区分两种方式的计算:快表查不到再查慢表和快慢表同时查询)

(甘特图)

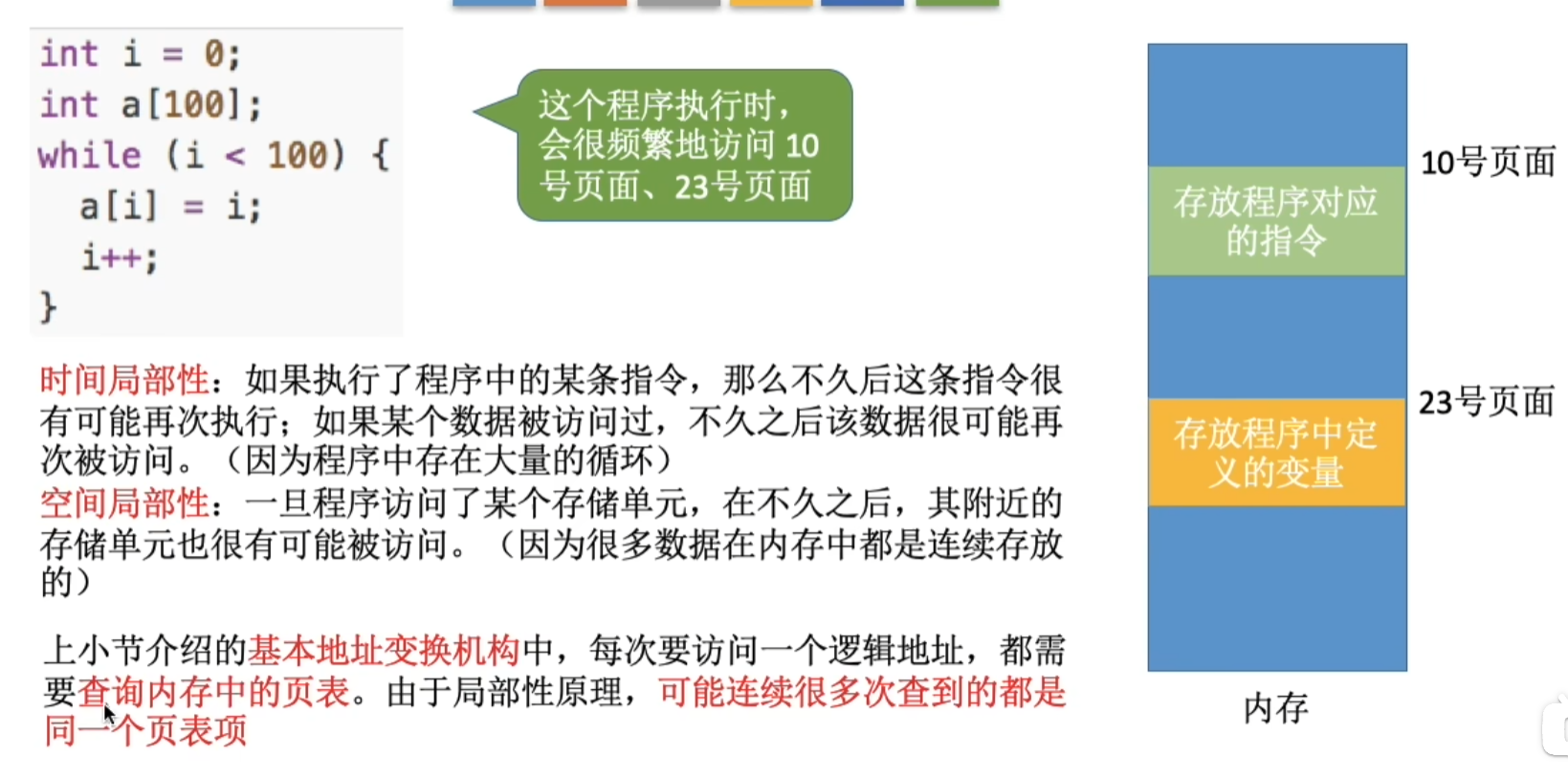

三、局部性原理

- 时间局部性

- 空间局部性

在这个案例中时间局部性体现于每一次的 while,空间局部性体现于数组 a 的连续存储。在同一进程下,局部性原理体现显著。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 分享一个免费、快速、无限量使用的满血 DeepSeek R1 模型,支持深度思考和联网搜索!

· 25岁的心里话

· 基于 Docker 搭建 FRP 内网穿透开源项目(很简单哒)

· ollama系列01:轻松3步本地部署deepseek,普通电脑可用

· 按钮权限的设计及实现