数电基础---MOS管,三极管和门电路

摆烂和勇敢面对也不矛盾

MOS管,三极管与门电路

MOS管

MOS管是金属-氧化物-半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor),MOS管组成的电路是CMOS电路。

P型材料是空穴型材料,空穴为多子,电子为少子。

N型材料是电子型材料,电子为多子,空穴为少子。

N沟道增强型MOS管

在P型半导体衬底上,制造两个高掺杂浓度的N型区,形成MOS管的源极S(Source)和漏极D(Drain),第三个电极称为栅极G(Gate)。(箭头指向电子聚集的地方???)

如果在漏极和源极之间加上了电压\(v_{DS}\),而令栅极和源极之间的电压\(V_{GS}=0\),则由于漏极和源极之间相当于两个PN结背向地串联(因为栅极和源极之间没有电压差,衬底的电子不发生运动,这时的衬底的电阻很大),所以\(D-S\)间不导通,\(i_{D}=0\)。

当栅极和源极之间加上正电压\(v_{GS}\),而且\(v_{GS}\)大于某个电压值\(V_{GS(th)}\)时,由于栅极与衬底间电场的吸引,使衬底中的少数载流子——电子聚集到栅极下面的衬底表面,形成一个N型的反型层。这个反型层就构成了D——S间的导电沟道,于是有\(i_D\)流通。\(V_{GS(th)}\)称为MOS管的开启电压。

因为导电沟道属于N型,而且在\(v_{GS}=0\)时不存在导电沟道,必须加以足够高的栅极电压才能有导电沟道形成,所以将这种类型的MOS管称为N沟道增强型MOS管。

随着源极和漏极之间的电压\(v_{GS}\)的升高,导电沟道的截面积也将加大,\(i_D\)增加,因此可以通过改变\(v_{GS}\)控制\(i_D\)的大小。

总结:N沟道增强型MOS管在\(v_{GS}=0\)时没有导电沟道,开启电压\(V_{GS}\)为正。工作时使用正电源,同时应将衬底接源极或者接到系统的最低电位上。

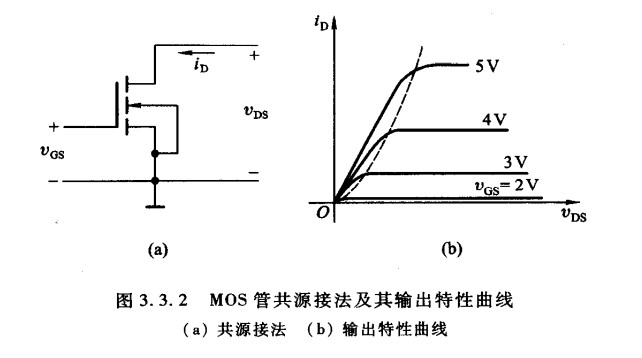

将栅极-源极之间的回路为输入电路(控制端),以漏极-源极之间的回路为输出回路(被控制端),这种称为共源接法。如图所示。

因为栅极和衬底间被二氧化硅绝缘层所隔离,在栅极和源极之间加上电压\(v_{GS}\)后,虽然会发生电子的迁移,导电沟道截面积的改变,但是不会有栅极电流流通,可以认为栅极电等于零。栅极和源极之间的输入电路没有电流,也就不存在所谓的输入电流的特性曲线。不过虽然栅极和源极之间没有电流,但是由于\(v_{GS}\)的存在,导电沟道的形成,所以漏极和源极之间存在电流,输出电路存在电流,所以我们可以研究输出电流的特性曲线。图里面给出了共源接法下的输出特性曲线,这个曲线也成为MOS管的漏极特性曲线。

漏极特性曲线分为三个工作区。

当\(v_{GS}<V_{GS(th)}\)时,漏极和源极之间没有导电沟道(电压不够大,没有充分的吸引电子的移动,就导电沟道没法形成),\(i_D \approx 0\),这时D-S间的内阻非常大。所以将曲线上\(v_{GS}<V_{GS(th)}\)的区域称为截止区。

当\(v_{GS} > V_{GS(th)}\)时,D-S间出现导电沟道,有\(i_D\)产生,这时又可以分成两个区域。

漏极特性曲线上虚线左边称为可变电阻区。在这个区里面当\(v_{GS}\)一定时,\(i_{D}\)与\(v_{DS}\)之比近似地等于一个常数,具有类似与线性电阻的性质,等效电阻的大小和\(v_{GS}\)的数值有关。

漏极特性曲线上虚线以右的区域称为恒流区。恒流区里漏极电流\(i_D\)的大小基本上由\(V_{GS}\)决定,\(V_{DS}\)的变化对\(i_D\)的影响很小。

P沟道增强型MOS管

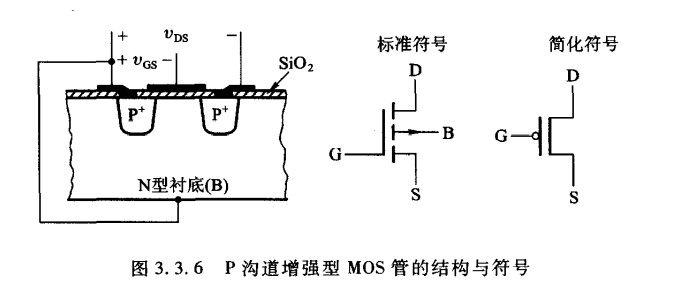

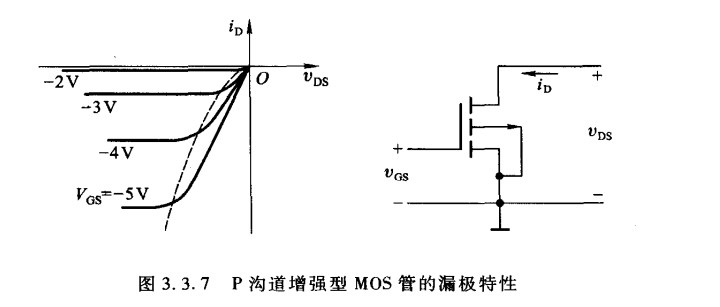

P沟道增强型MOS管衬底是N型衬底,导电沟道是P型。因为衬底N型,电子多,导电沟道为P型,需要空穴作为载流子(这么看作吧),所以需要在栅极上加上足够大的负电压,才能把N型衬底上的少子空穴吸引到栅极下方的衬底表面,形成P型导电沟道,所以P沟道增强型MOS管的开启电压\(V_{GS(th)}\)为负值,这种MOS管工作时使用负电源,同时需要将衬底接源极或者接到系统的最高电位上。下图就是P沟道增强型MOS管的结构和符号(箭头指向电子多的地方)

P沟道增强型MOS管和N沟道增强型MOS管的特性差不多,但由于P沟道增强型MOS管采取的是负电源,所以他的输出特性曲线相较于N沟道来说是反着的。

N沟道耗尽型MOS管

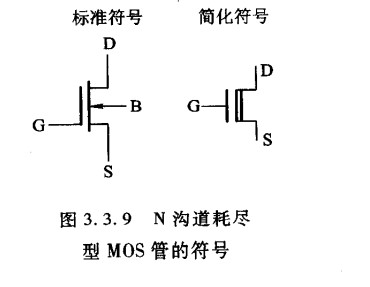

耗尽型MOS管的结构和增强型MOS管类似,区别在于耗尽型MOS管中,栅极下面的二氧化硅绝缘层中掺进了一定浓度的正离子,着写正离子所吸引的电场足以将衬底中的少数载流子--电子吸引到栅极下面的衬底表面,在D-S间形成导电沟道。所以在\(v_{GS}=0\)时就已经由导电沟道存在了。\(v_{GS}\)为正时导电沟道变宽,\(i_D\)增大。\(v_{GS}\)为负时导电沟道变窄,\(i_D\)减小。直到\(v_{GS}\)小于某一个负电压值时导电沟道才消失,MOS截止。\(V_{GS(off)}\)称为N沟道耗尽型MOS管的夹断电压。

下图是N沟道耗尽型MOS管的符号,图中D—S是连通的,表示\(v_{GS}=0\)时已有导电沟道存在。

在正常工作时,N沟道耗尽型MOS管的衬底同样应该连接到源极或系统的最低电位上。

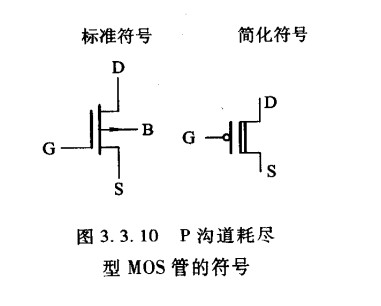

P沟道耗尽型MOS管

P沟道耗尽型MOS管与P沟道增强型MOS管的结构相同,不同的是在\(v_{GS}=0\)时已经由导电沟道的存在了。当\(v_{GS}\)为负时导电沟道进一步加宽,\(i_D\)的绝对值增加,而\(v_{GS}\)为正时导电沟道变窄,\(i_D\)的绝对值减小。,当\(v_{GS}\)的正电压大于夹断电压\(V_{GS(off)}\)时,导电沟道消失,管子截止。

如图是P沟道耗尽型MOS管的符号,工作时应将它的衬底和源极相连,或将衬底连接到系统的最高电位上。

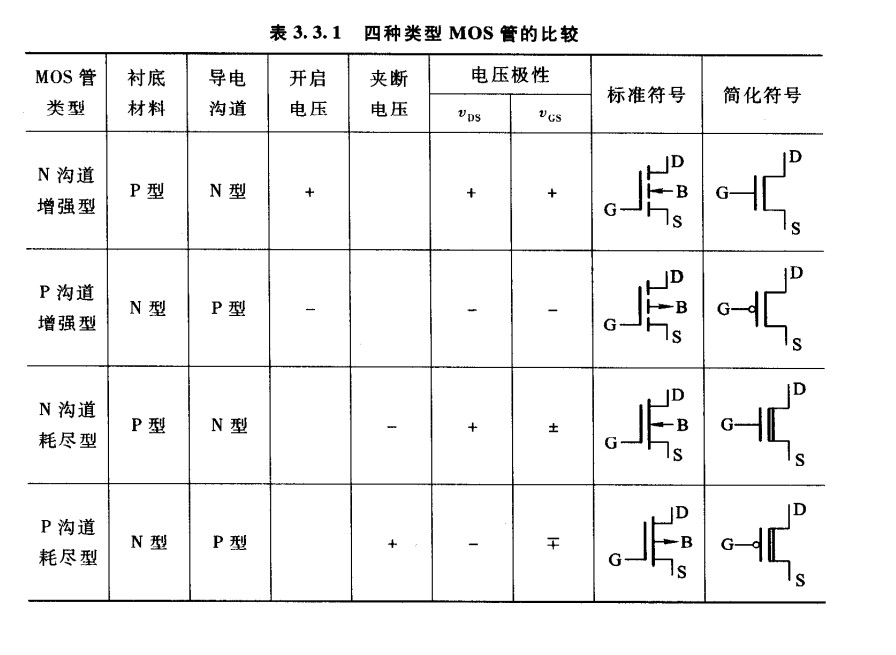

四种MOS管的比较:

三极管

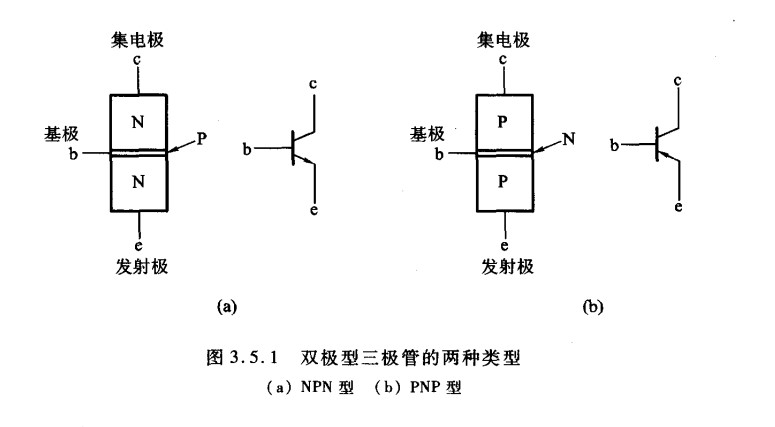

一个独立的双极型三极管由管芯,三个引出电极和外壳组成。

三个引出电极分别称为基极(base),集电极(collector)和发射极(emitter)。

外壳的形状和材料不尽相同。

管芯由三层P型和N型半导体组合在一起而构成,有NPN型和PNP两种。

因为在工作时有电子和空穴两种载流子参与导电过程,所以称为双极型三极管。

(从图上可以看出箭头指向N型材料)

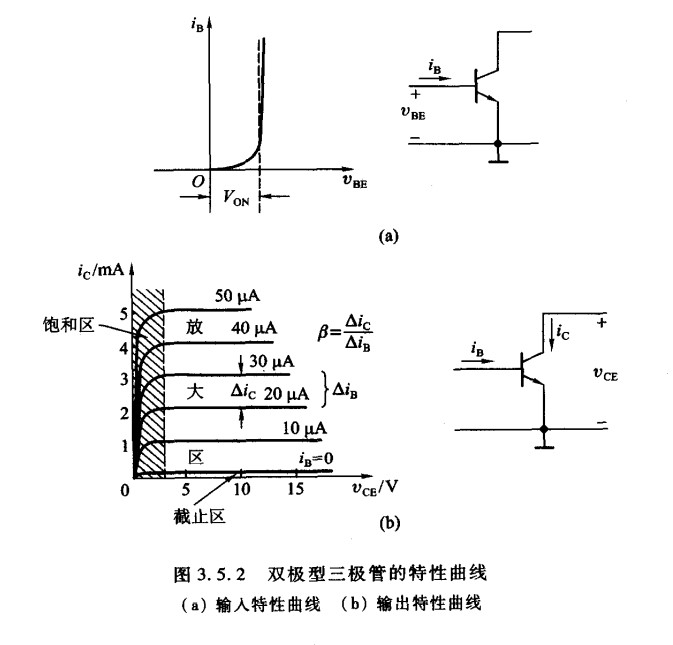

如果以基极b和发射极e之间的发射结作为输入回路,则可以测出表示输入电压\(v_{BE}\)和输入电流\(i_B\)之间关系的特性曲线,这个曲线称为输入特性曲线,如(a)所示。图中的\(V_{ON}\)称为开启电压。

如果以集电极c和发射极e之间的回路作为输出回路,则可以测出在不同的\(i_B\)值下表示集电极电流\(i_C\)和集电极电压\(v_{CE}\)之间关系的曲线,称为输出特性曲线。

从图上可以看出集电极电流\(i_C\)不仅受\(v_{CE}\)的影响,还受输入的基极电流\(i_B\)的控制。可以把b-e之间看作控制端,c-e之间看作被控制端,通过控制\(v_{BE}\)来控制\(i_B\)进而控制\(i_C\)。

输出特性曲线可以分成三个区域。

特性曲线右边水平的部分称为放大区(或者叫线性区),特点是\(i_C\)随\(i_B\)成正比变化,而几乎不受\(v_{CE}\)变化的影响。

曲线靠近纵坐标轴的区域称为饱和区。特点是\(i_C\)不再随\(i_B\)以一定的比例增加,而趋于饱和(这里应该至这个比例区域饱和,无限大了)。

\(i_B=0\)的曲线以下称为截止区。截止区的特点是\(i_C\)几乎等于0。

门电路

开关电路

CMOS开关电路

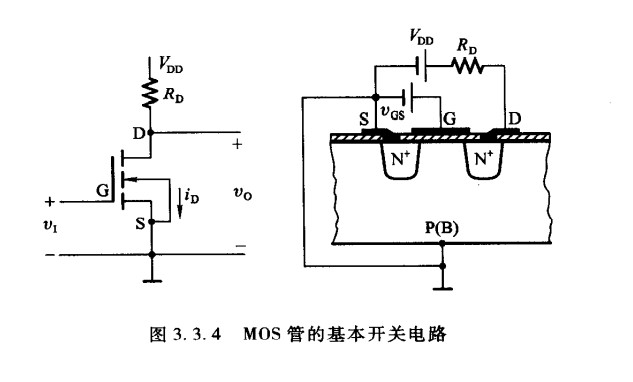

用MOS管和三极管可以各自组成开关电路

如上图就是N沟道增强型MOS管组成的开关电路,源极和栅极接在低电平的位置,漏极接一上拉电阻接在系统的高电位位置上。

当\(v_1=v_{GS}<V_{GS(th)}\)时,输入电路的电压小于MOS管的开启电压,所以MOS管工作在截止区,只要负载电阻\(R_D\)远远小于MOS的截止内阻,则输出端即为高电平\(V_{OH} \approx V_{DD}\),这时MOS管D-S之间就相当于一个断开的开关。

当\(v_1>V_{GS(th)}\)时,MOS管导通,当MOS的内阻远远小于负载电阻\(R_D\)时,输出端将为低电平\(V_{OL} \approx 0\),这时MOS管的D-S间相当于一个闭合的开关(当然MOS的内阻在恒流区随输入电压的改变而改变,这时电路工作在放大状态,可以看作开关电路的中间状态)。

所以只要电路参数选择的合理,就可以使输入为低电平时MOS管截止,开关电路输出为高电平,当输入为高电平时,MOS管导通,输出电平为低电平。

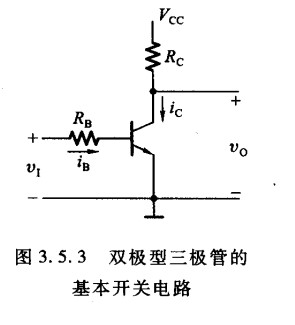

TTL开关电路

有三极管的特性可以知道,当输入电压\(v_1\)为低电平时三极管工作在截止状态,输出为高电平,当\(v_1\)为高电平时三极管工作在饱和状态,输出为低电平。

所以,合理的选择参数,保证\(v_1\)为低电平时小于开关电压\(V_{ON}\)三极管工作在截止状态,输出电压为高电平。当\(v_1\)为高电平时保证\(i_B\)大于基极饱和电流,三极管工作在深度饱和状态,输出电压为低电平。三极管c-e间就相当于一个受\(v_1\)控制的开关。(具体的开关电压和基极饱和电流怎么算就不是数电要考虑的问题了吧......那是模电的任务应该😂)

非门

CMOS非门

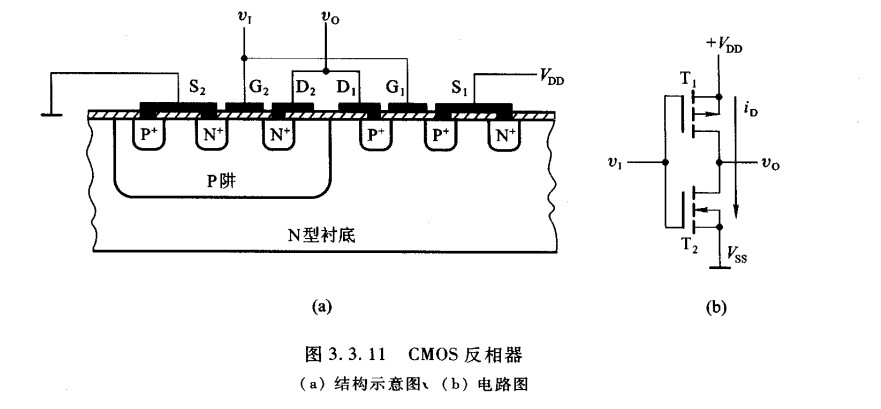

CMOS反相器(非门)结构如图所示,由一个P沟道增强型MOS管(\(T_1\))和一个N沟道增强型MOS管(\(T_2\))构成。

当输入电压\(v_I\)为高电平时,\(T_1\)截止,\(T_2\)导通,输出电压\(v_o\)为低电平。

当输入电压\(v_I\)为低电平时,\(T_2\)截止,\(T_1\)导通,输出电压\(v_o\)为高电平。

所以输出与输入是逻辑非的关系,通常也将非门称为反相器(inverter)。

无论输入电压\(v_I\)是高电平还是低电平,两个MOS管总有一个导通另一个截止。即所谓的互补状态。所以这种电路结构形式又称为互补对称式金属-氧化物-半导体电路(Complementary-Symmetry Metal-Oxide-Semiconductor Circuit),简称CMOS电路。

由于静态下无论输入电平的高低,两个MOS管总有一个截止另一个导通,而且截止内阻很大,所以流过两个MOs管的静态电流很小,所以CMOS反相器的静态功耗极小。这也是CMOS电路的一大特点。

TTL非门

与非门,或非门

CMOS与非门,或非门

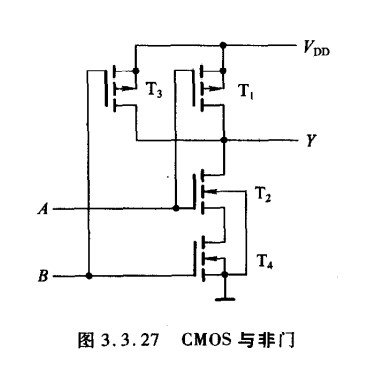

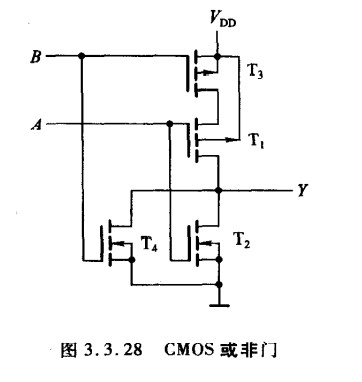

根据MOS管的特性和互补结构,也可以设计出与非门和或非门的结构。

对于CMOS与非门,只有当输入电压\(A\),\(B\)都为高电平时,\(T_1\),\(T_3\)截止,\(T_2\),\(T_4\)导通。输出电压\(Y\)为低电平,其他情况下,\(T_1\)和\(T_3\)中有一个导通,\(T_2\)和\(T_4\)中有一个截止,输出电压\(Y\)为高电平。

对于CMOS或非门,只有当输入电压\(A\),\(B\)都为低电平时,\(T_1\),\(T_3\)导通,\(T_2\),\(T_4\)截止。输出电压\(Y\)为高电平,其他情况下,\(T_1\)和\(T_3\)中有一个截止,\(T_2\)和\(T_4\)中有一个导通,输出电压\(Y\)为低电平。

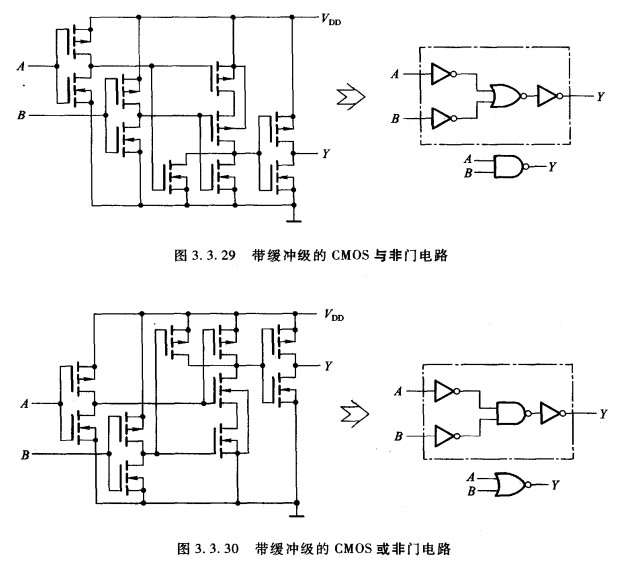

上面门电路的结构很简单,但缺点也很明显,输出电阻随输入状态的变化很大(会出现MOS管内阻的串联和并联),那这样就导致输出特性的不稳定,所以在实际生产的CMOS电路中都会在输出带有缓冲级,就是在门电路的每个输入端输出端各增设一级反相器。

这些带缓冲级的门电路其输出电阻,输出的高低电平以及电压传输特性将不受输入端状态的影响。(只与反相器的特性有关)。

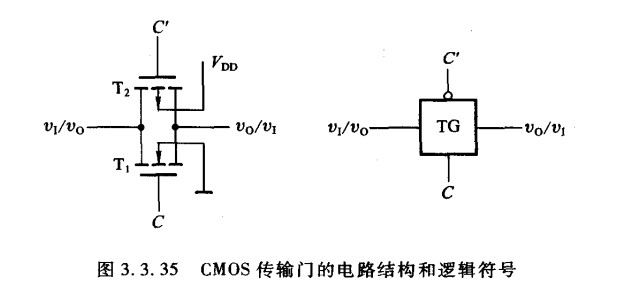

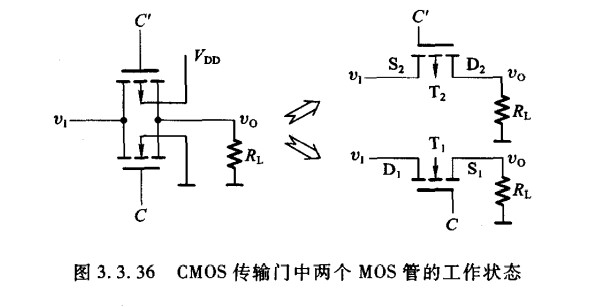

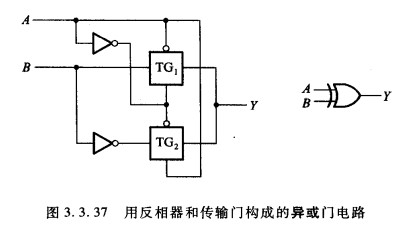

传输门

利用P沟道MOS管和N沟道MOS管的互补性可以接成如图结构的CMOS传输门。\(T_1\)是N沟道增强型MOS管,\(T_2\)是P沟道增强型MOS管。

因为\(T_1\)和\(T_2\)的源极和漏极在结构上是完全对称的,所以将传输门画成这种形式。

当\(C^{\prime}\)接低电平,\(C\)接高电平时,两个MOS管导通,传输门导通。当\(C^{\prime}\)接高电平,\(C\)接低电平时,两个MOS管截止,传输门截止。

利用CMOS传输门和CMOS反相器可以组合成各种复杂的逻辑电路。

传输门的另一个重要用途是作模拟开关,用来传输连续变化的模拟电压信号。

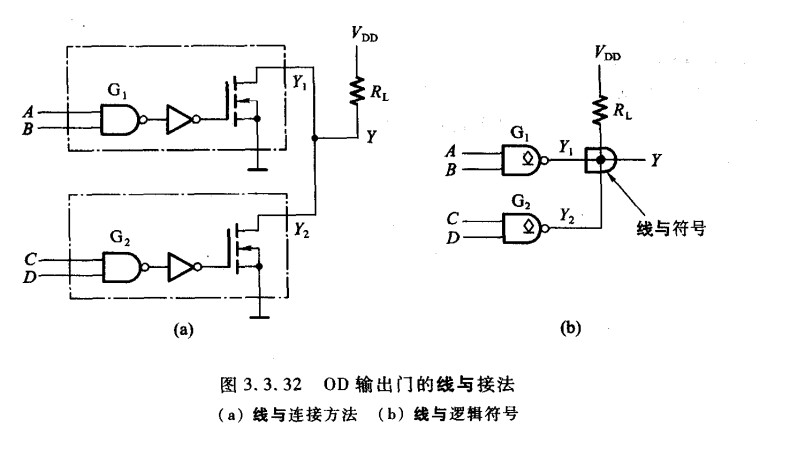

线与

线与逻辑,即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能。

就是说可以在不用与门器件的情况下实现"与"的逻辑,两条连线直接相连,不借助于逻辑器件实现与的功能。比如现在由两个输出A和B,经A与B直接相连,只有两个输出都为高电平,这条线的输出才为高电平,否则为低电平。一般用OC门或OD门实现线与逻辑。

线与的逻辑符号是画在线与连接点处的与门轮廓。

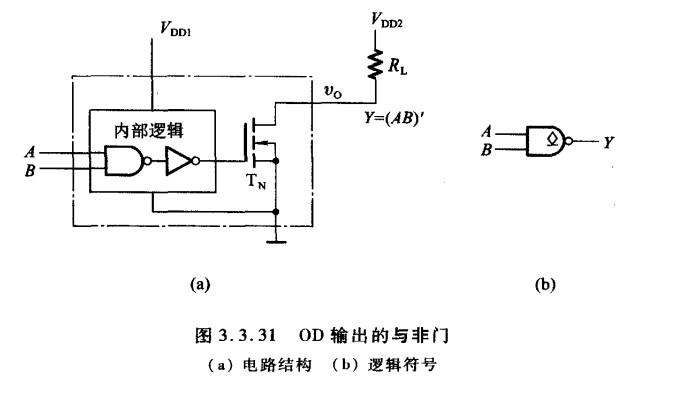

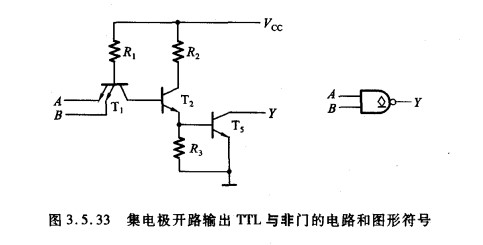

OD门

在CMOS电路中,为了满足输出电平变换,吸收大负载电流以及实现线与连接等需要,有时将输出级电路结构改为一个漏极开路输出的MOS管,构成漏极开路输出(Open-Drain Output)门电路,简称OD门。

如图是一个OD输出与非门,逻辑符号里面的菱形记号表示OD输出结构。

只要满足\(T_N\)的截止内阻远远大于负载电阻\(R_L\)远远大于\(T_N\)的导通电阻,就可以使\(T_N\)截止时,输出电压\(v_o=V_{OH} \approx V_{DD2}\),输出高电平,当\(T_N\)导通时,\(v_o=V_{OL} \approx 0\),输出低电平。

OD门的作用:

一方面因为\(V_{DD2}\)可以选为不同于\(V_{DD1}\)的数值,所以就很容易将输入的高、低电平(\(V_{DD1}\)/0)转化为输出的高、低电平(\(V_{DD2}\)/0)了。

另一方面可以将几个OD门的输出端直接相连,实现线与逻辑。

从图上可以看出,只有当\(Y_1\)、\(Y_2\)都为高电平时输出\(Y\)才为高电平,否则输出为低电平,所以\(Y_1\),\(Y_2\)和\(Y\)之间使与逻辑的关系,即

OC门

推挽结构(推拉结构)一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止。

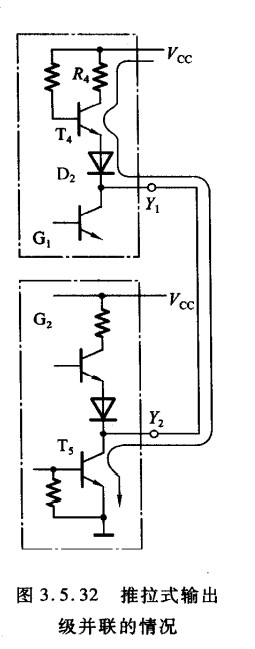

推拉式输出电路虽然输出电阻很低,但是不能把他们的输出端直接并联接成线与结构。

倘若一个门的输出式高电平而另一个门的输出是低电平,则输出端并联之后必然有很大的负载电流同时流过这两个门的输出级。这个电流的数值将远远超过正常工作电流,可能还是门电路损坏。

三态门

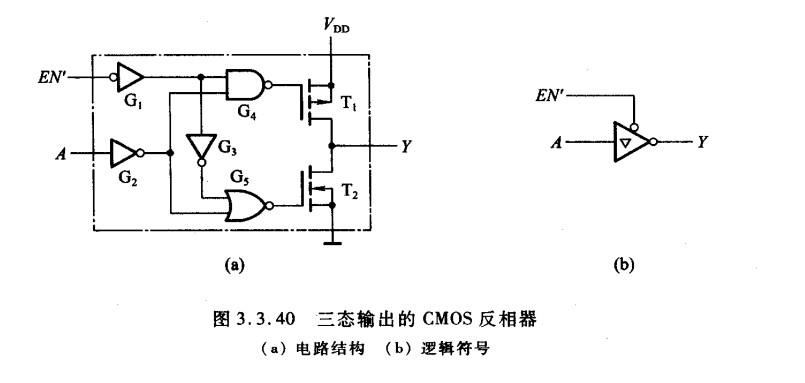

三态输出门电路的输出除了有高,低电平这两个状态以外,还有第三个状态-高阻态。因为这种电路结构总是接在集成电路的输出端,所以也将这种电路称为输出缓冲器。

当\(EN^{\prime}=0\)时,若A=1,Y=0,若A=0,Y=1;所以\(Y=A^{\prime}\),反相器处于正常工作状态。

若\(EN^{\prime}=1\)时,不管A的状态如何,\(G_4\)输出高电平而\(G_5\)输出低电平,\(T_1\)和\(T_2\)同时截止,输出呈现高阻态。

反相器符号内的三角形记号表示三态输出结构。

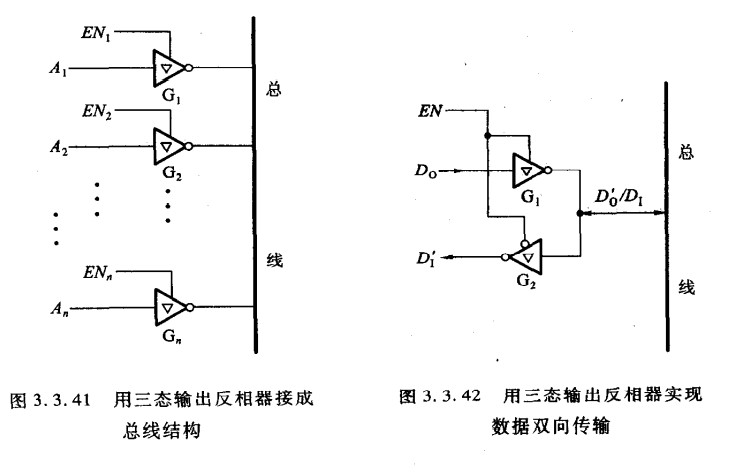

三态门可以用于总线的连接。

CMOS电路与TTL电路

CMOS电路

两个MOS管总有一个导通另一个截止。即所谓的互补状态。所以这种电路结构形式又称为互补对称式金属-氧化物-半导体电路(Complementary-Symmetry Metal-Oxide-Semiconductor Circuit),简称CMOS电路。

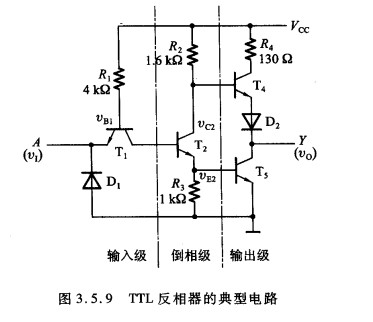

TTL电路

电路的输入端和输出端均为三极管结构,称为三极管-三极管逻辑电路(Transistor-Transistor Logic),简称TTL电路。

CMOS电路TTL电路优缺点

1.CMOS是场效应管构成(单极性电路),TTL为双极晶体管构成(双极性电路)

2.COMS的逻辑电平范围比较大(5~15V),TTL只能在5V下工作

3.CMOS的高低电平之间相差比较大、抗干扰性强,TTL则相差小,抗干扰能力差

4.CMOS功耗很小,TTL功耗较大(1~5mA/门)

5.CMOS的工作频率较TTL略低,但是高速CMOS速度与TTL差不多相当

6.CMOS的噪声容限比TTL噪声容限大

7.通常以为TTL门的速度高于“CMOS门电路。影响 TTL门电路工作速度的主要因素是电路内部管子的开关特性、电路结构及内部的各电阻阻数值。电阻数值越大,工作速度越低。管子的开关时间越长,门的工作速度越低。门的速度主要体现在输出波形相对于输入波形上有“传输延时”tpd。将tpd与空载功耗P的乘积称为“速度-功耗积”,做为器件性能的一个重要指标,其值越小,表明器件的性能越 好(一般约为几十皮(10-12)焦耳)。与TTL门电路的情况不同,影响CMOS电路工作速度的主要因素在于电路的外部,即负载电容CL。CL是主要影响器件工作速度的原因。由CL所决定的影响CMOS门的传输延时约为几十纳秒。

8.TTL电路是电流控制器件,而coms电路是电压控制器件。

浙公网安备 33010602011771号

浙公网安备 33010602011771号