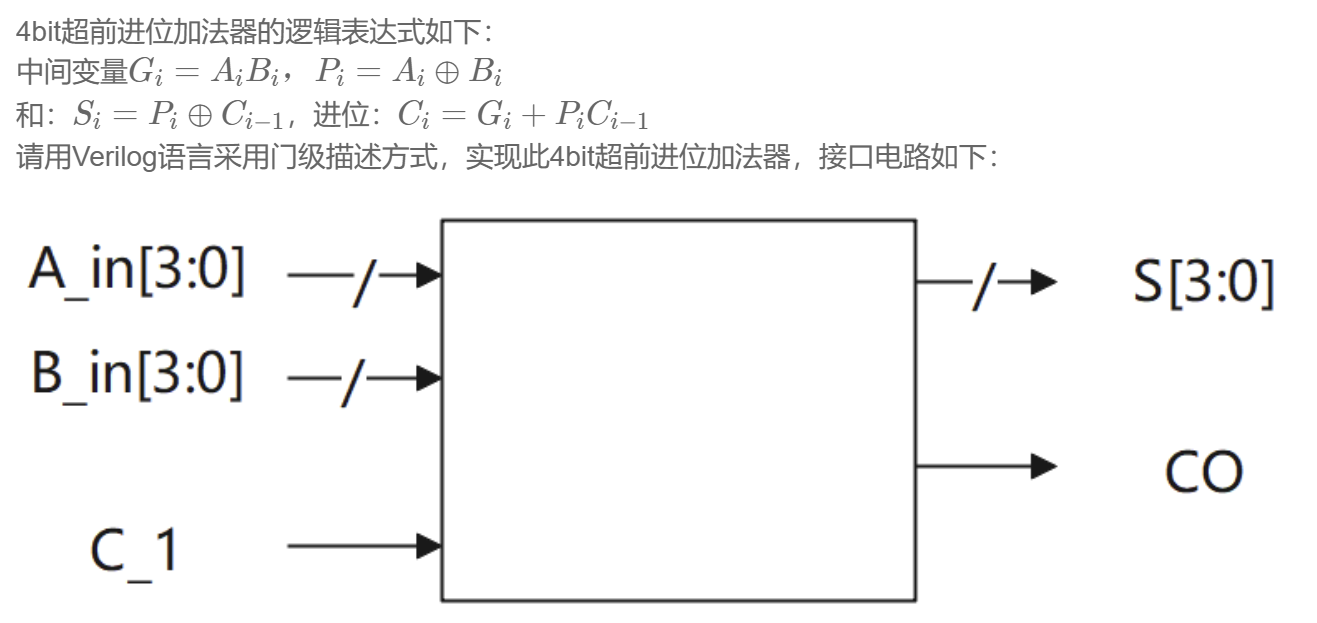

VL12 4bit超前进位加法器电路

`timescale 1ns/1ns

module lca_4(

input [3:0] A_in ,

input [3:0] B_in ,

input C_1 ,

output wire CO ,

output wire [3:0] S

);

reg [3:0] C;

reg [3:0] G;

reg [3:0] P;

reg [3:0] rS;

integer i;

always @(*)begin

for(i=0;i<4;i=i+1)begin

G[i]=A_in[i] & B_in[i];

P[i]=A_in[i] ^ B_in[i];

C[i]=i>0 ? (G[i] | P[i] & C[i-1]) : (G[i] | P[i] & C_1);

rS[i]=i>0 ? (P[i] ^ C[i-1]) : P[i] ^C_1;

end

end

assign S=rS;

assign CO=C[3];

endmodule

注意点:

使用always语句因此CGPS需要定义为reg而不是wire,也因此最终结果需要执行assign S=rS;

题目要求使用门级语言,因此需要将乘法运算转化为与操作,加法运算转为或操作。

技巧在于i>0 ? (*):(*),有效解决了C[-1]的特殊情况

浙公网安备 33010602011771号

浙公网安备 33010602011771号