vivado使用TCL脚本无工程方式生成固件及报告

做IC一般都是使用linux系统进行编写代码,综合仿真等操作。因此没有图像化界面只跑脚本是提高效率的一种方式,笔者以前一直使用图像化界面的方式对Vivado工程进行编译综合,后来学会了windows下也可以使用脚本直接无工程生成bit文件,时序报告等。

步骤大致如下,rtl.list在上文有提及,这里不重复讲具体怎么写。

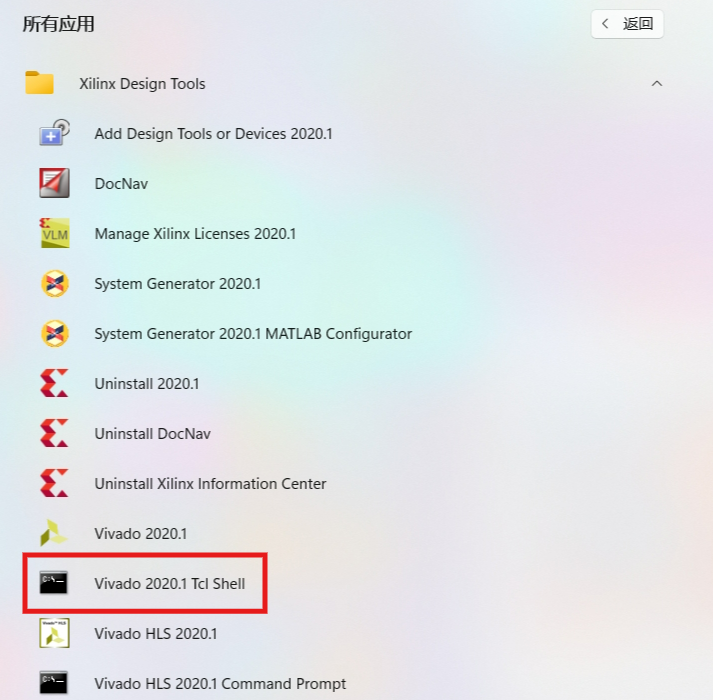

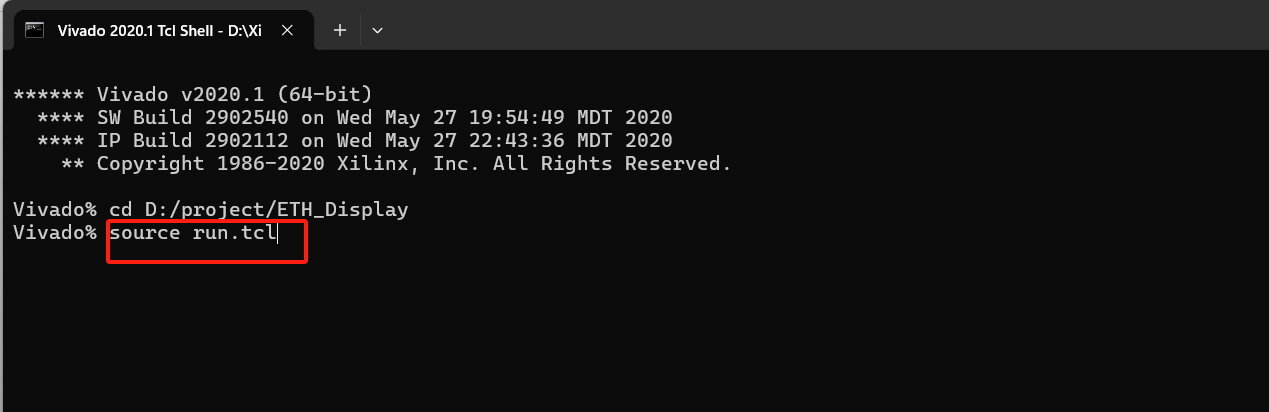

1. 首先是打开vivado在windows下的shell

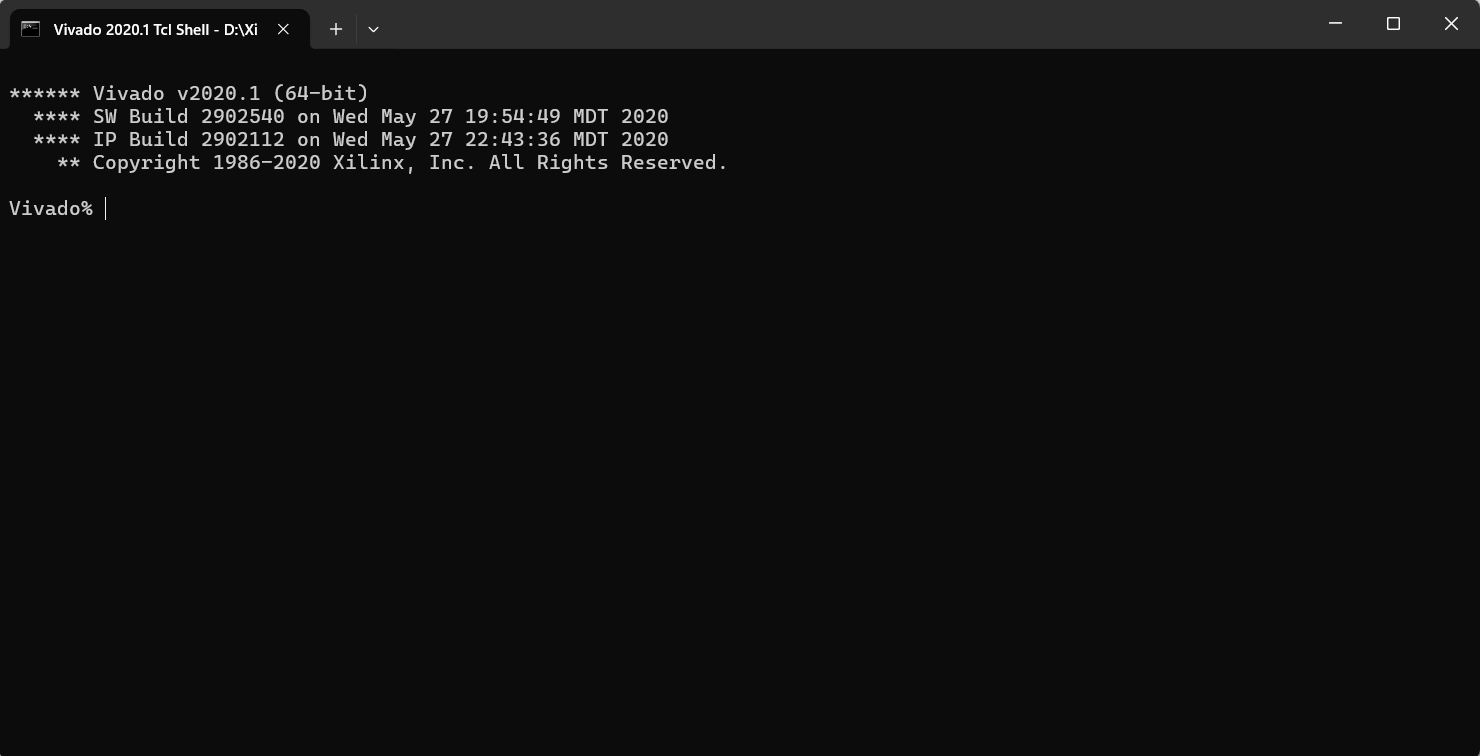

接着跳出指令画面

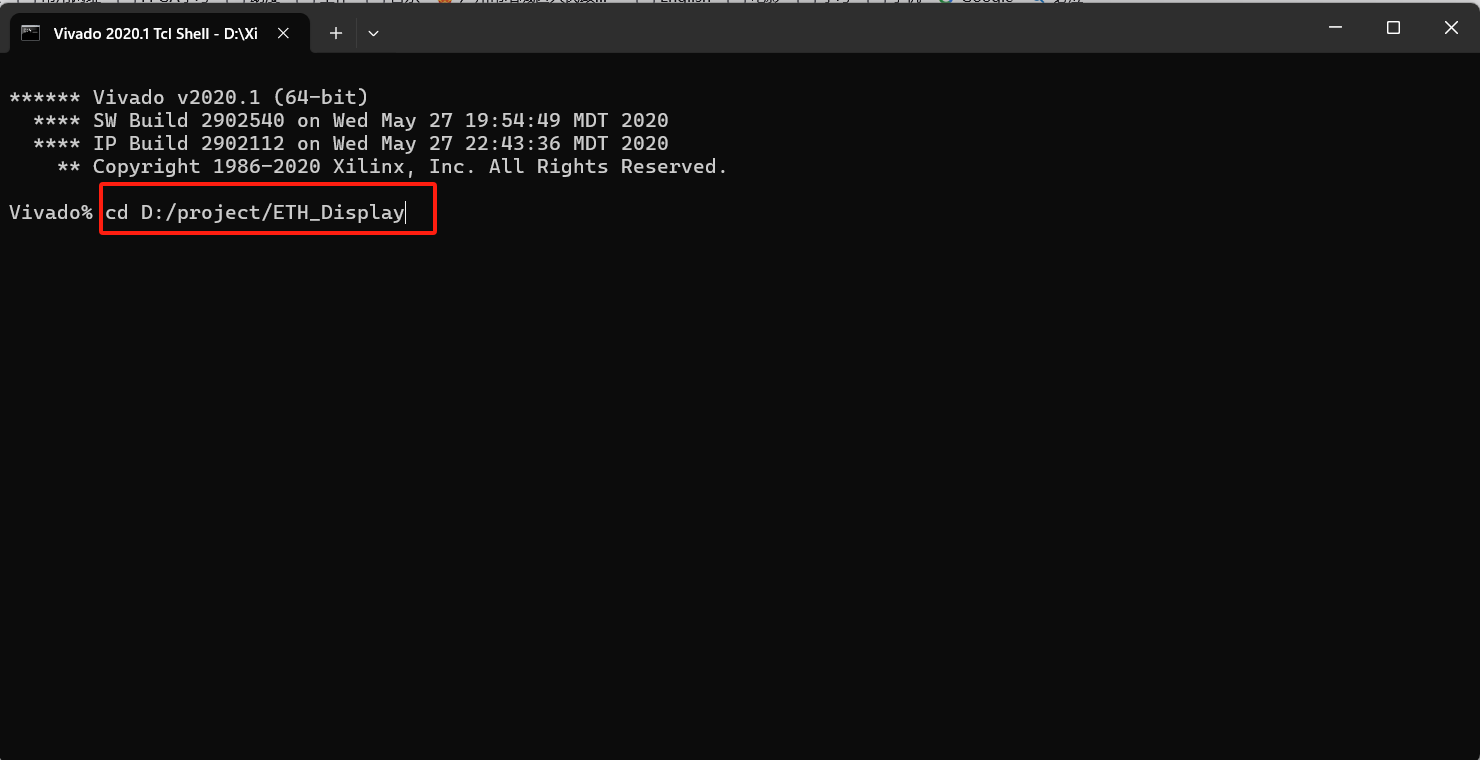

2. 进入到需要编译的工程所在的目录下

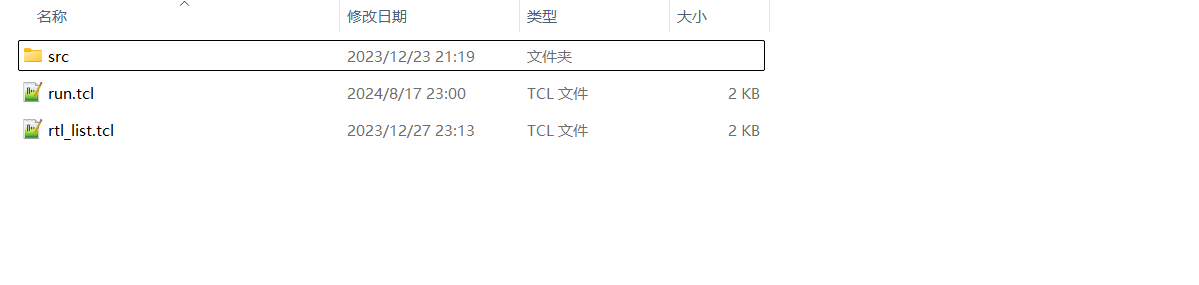

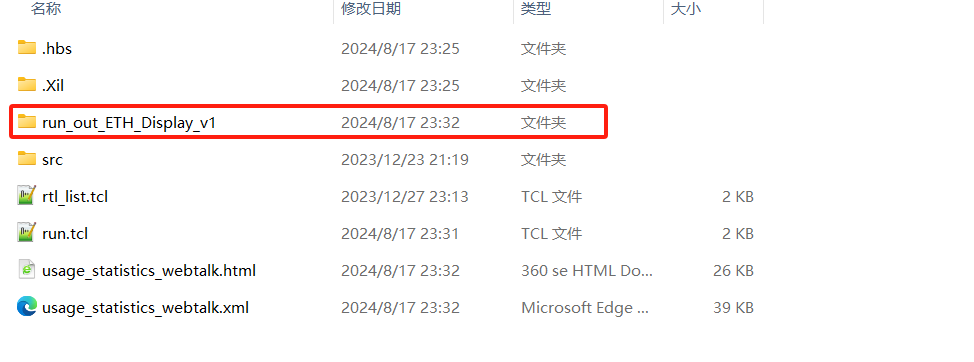

3. 在当前目录下的文件如下,其中src存放的是代码,IP核,xdc文件等文件,这些上一篇文章有提到,都是同一个工程

run.tcl的内容如下

set name ETH_Display_v1 set proj_dir D:/project/ETH_Display set output_dir ./run_out_$name file mkdir $output_dir set_part xczu3eg-sfvc784-1-i source $proj_dir/rtl_list.tcl #read_xdc $proj_dir/constraints/AXU3EG.xdc set_param general.maxThreads 16 synth_design -top AXU3EG_top -part xczu3eg-sfvc784-1-i \ -include_dirs $proj_dir/src/hdl \ -include_dirs $proj_dir/src/hdl/udp \ -include_dirs $proj_dir/src/hdl/udp/arp \ -include_dirs $proj_dir/src/hdl/udp/gmii_to_rgmii #sfcu write_checkpoint -force $output_dir/postsynth write_verilog -force $output_dir/postsynth_netlist.v report_clocks -file $output_dir/clock_out.txt opt_design place_design -directive AltSpreadLogic_high write_checkpoint -force $output_dir/post_place route_design write_checkpoint -force $output_dir/post_route report_timing_summary -max_paths 5 -file $output_dir/post_route_timing_summary.rpt report_timing -sort_by group -max_path 5 -path_type summary -file $output_dir/post_route_timing.rpt report_utilization -file $output_dir/post_route_util.rpt report_utilization -hierarchical -append -file $output_dir/post_route_util.rpt write_bitstream -force -bin_file $output_dir/$name.bit

之后只需在步骤2处输入指令source run.tcl即可,然后等待编译完成即可,编译完成目录下会出现生成的文件。

以上是笔者在vivado2020.1版本进行的无工程生成固件的操作,不同的vivado版本对指令也存在差异,正常报错会提示。笔者觉得使用无工程生成固件比UI界面生成的方式要快不少。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步