vivado使用tcl脚本新建工程

对于一些比较大的FPGA项目,包含较多的模块时,这是通过写脚本进行项目工程新建可能比vivado图形界面操作更方便。还有就是对原有项目进行拓展,记得笔者初学FPGA,都是复制了原项目,然后再更改代码,这样会导致工程很臃肿占用资源多,后来笔者就通过脚本来对工程进行备份或者移植。以下便是方法,先写好生成新工程的脚本。

create_new_proj.tcl

1 if {[info exists ::create_path]} { 2 set dest_dir $::create_path 3 } else { 4 set dest_dir [file normalize [file dirname [info script]]] 5 } 6 puts "INFO: Creating new project in $dest_dir/proj" 7 8 cd $dest_dir 9 set proj_name [file tail $dest_dir] 10 cd $dest_dir/proj 11 12 #set part "xc7z020clg400-2" 13 set part "xczu3eg-sfvc784-1-i" 14 create_project $proj_name $dest_dir/proj 15 source $dest_dir/rtl_list.tcl 16 17 set_property top AXUEG_top [current_fileset] 18 update_ip_catalog 19 20 set obj [get_projects $proj_name] 21 set_property "default_lib" "xil_defaultlib" $obj 22 set_property "part" $part $obj 23 # set_property "board_part" $brd_part $obj 24 set_property "simulator_language" "Mixed" $obj 25 set_property "target_language" "Verilog" $obj 26 set_property XPM_LIBRARIES {XPM_CDC XPM_MEMORY XPM_FIFO} [current_project]

文件列表rtl_list.tcl,其中read_verilog是加载verilog文件;read_xdc是加载xdc(约束文件);read_ip是加载例化好的IP核,后缀一般是.xci。

1 set path D:/project/ETH_Display 2 read_verilog $path/src/hdl/AXU3EG_top.v 3 read_verilog $path/src/hdl/Cmos_buf.v 4 read_verilog $path/src/hdl/cmos_decode.v 5 read_verilog $path/src/hdl/Cmos_initial.v 6 read_verilog $path/src/hdl/Eth_img.v 7 read_verilog $path/src/hdl/i2c_dri.v 8 read_verilog $path/src/hdl/i2c_ov7725_rgb565_cfg.v 9 read_verilog $path/src/hdl/Image_process.v 10 read_verilog $path/src/hdl/RstFrameGen.v 11 read_verilog $path/src/hdl/VGA_test_gen.v 12 read_verilog $path/src/hdl/udp/eth_ctrl.v 13 read_verilog $path/src/hdl/udp/eth_interface.v 14 read_verilog $path/src/hdl/udp/Gmii_to_Rgmii.v 15 read_verilog $path/src/hdl/udp/img_data_pkt.v 16 read_verilog $path/src/hdl/udp/start_transfer_ctrl.v 17 read_verilog $path/src/hdl/udp/udp.v 18 read_verilog $path/src/hdl/udp/udp_rx.v 19 read_verilog $path/src/hdl/udp/udp_tx.v 20 read_verilog $path/src/hdl/udp/arp/arp.v 21 read_verilog $path/src/hdl/udp/arp/arp_rx.v 22 read_verilog $path/src/hdl/udp/arp/arp_tx.v 23 read_verilog $path/src/hdl/udp/arp/crc32_d8.v 24 read_xdc $path/src/constraints/AXU3EG.xdc 25 read_ip $path/src/ip/async_fifo_512x18/async_fifo_512x18.xci 26 read_ip $path/src/ip/async_fifo_1024x32b/async_fifo_1024x32b.xci 27 read_ip $path/src/ip/sys_pll/sys_pll.xci

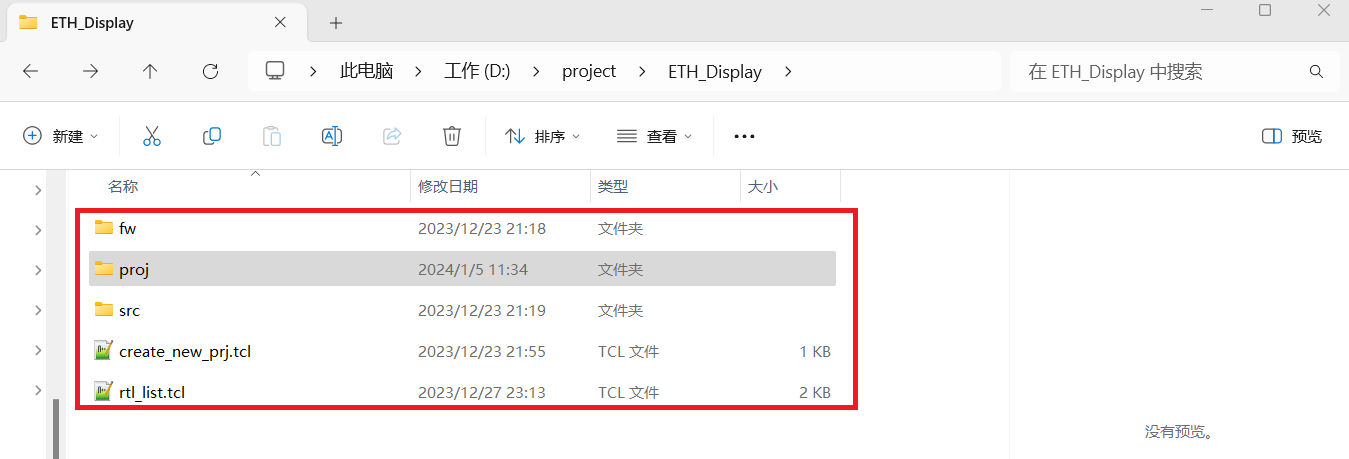

新建以下几个文件夹,而且在每次跑脚本前确保proj文件是空的,否则脚本会报错。

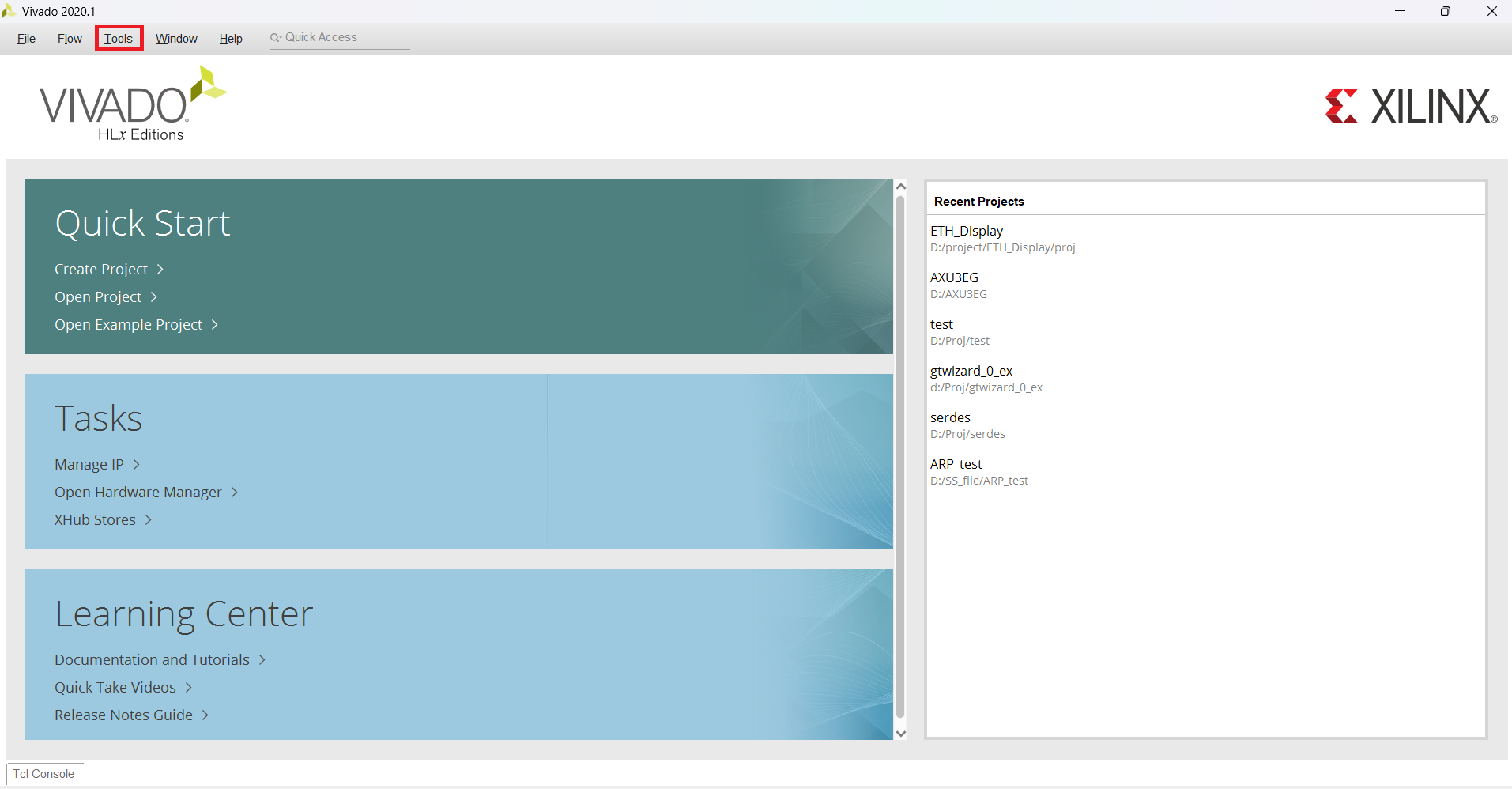

接着打开vivado图形化界面,选择Tool。

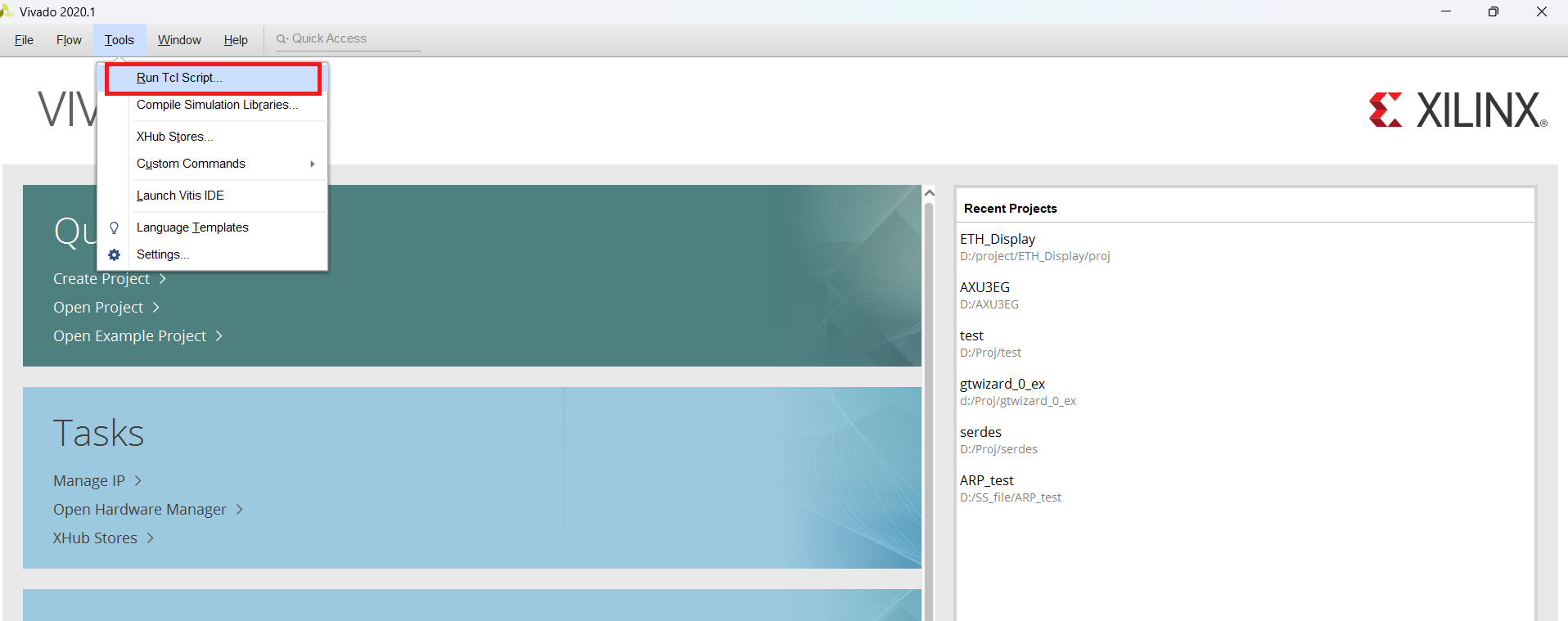

然后选择红框的Run Tcl Script...

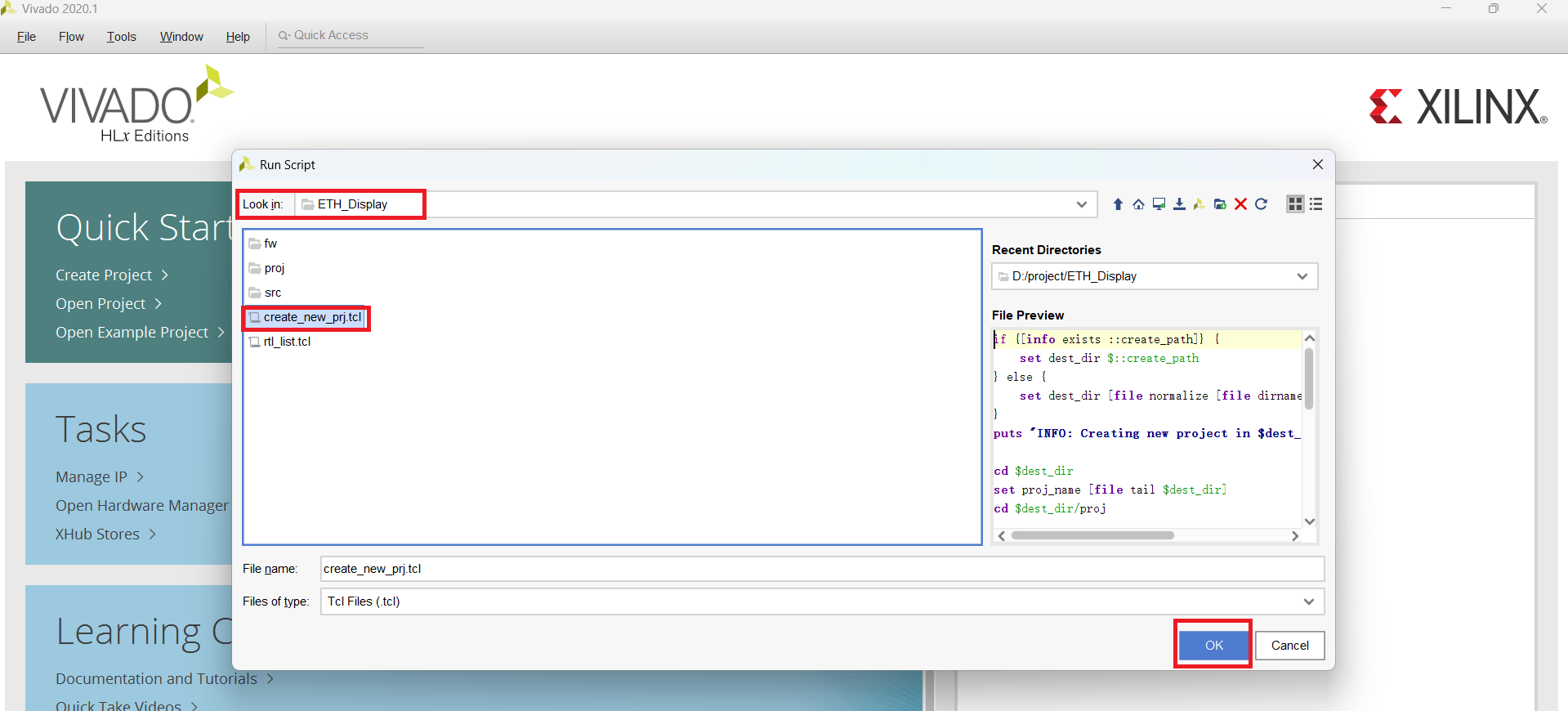

接着选择前面新建的create_new_proj.tcl脚本,点击OK。

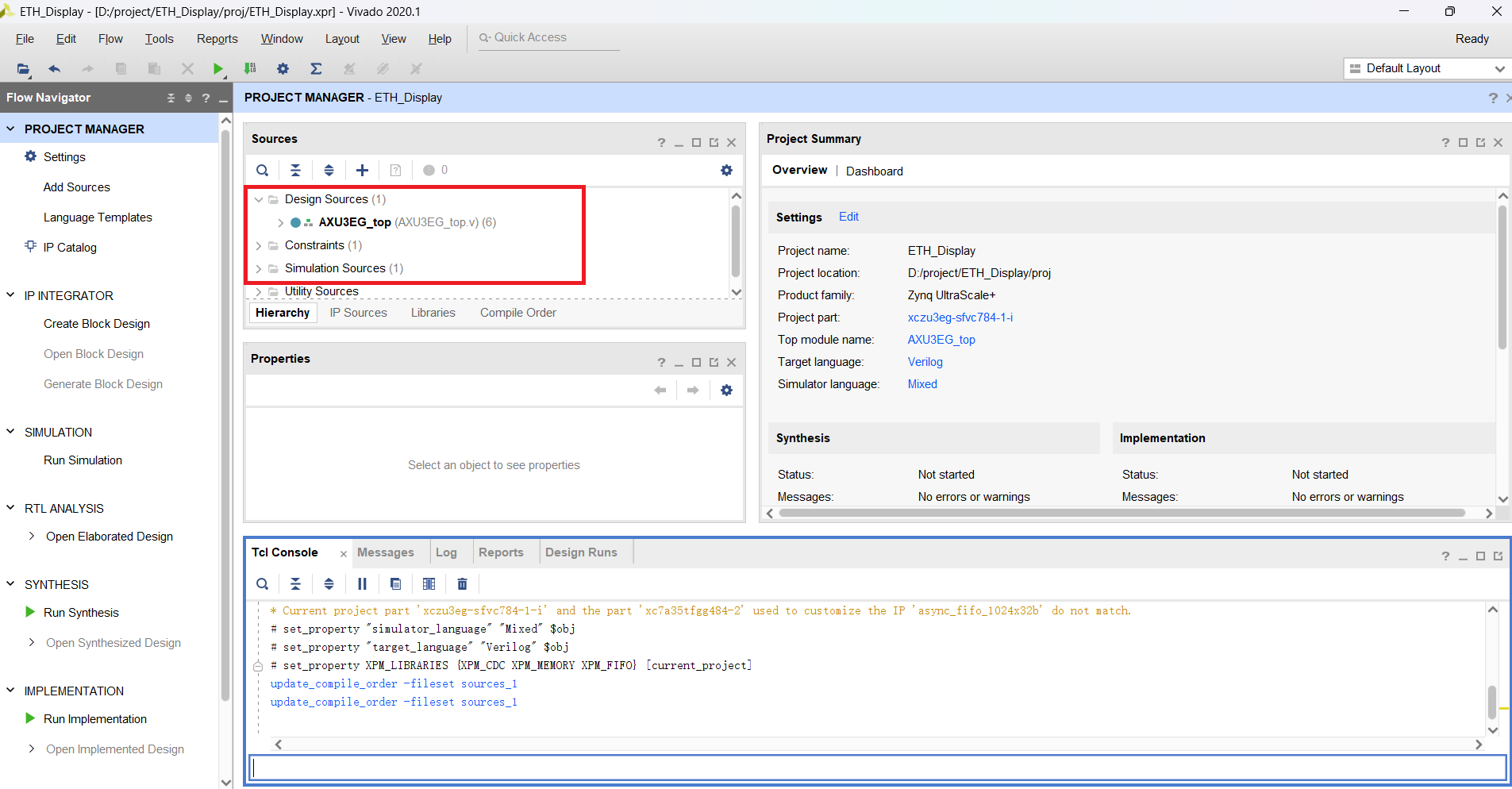

跑完脚本就会出现完整的工程,有设计代码也有约束文件,可以直接进行综合编译生成bit文件。当然也可以在运行脚本上加综合布线等等指令,按照文档添加指令即可。出现报错则需根据错误提示修改文件列表rtl_list.tcl或者create_new_proj.tcl。

以上便是使用tcl脚本进行vivado新工程备份或新建的方法,有时间再写个无工程生成bit文件的博文,也是使用tcl脚本实现。