verdi仿真的简单使用

对于IC的从业人员来说,Verdi是使用频率很高的工具,这也是Synopsys(新思科技)的EDA工具。笔者之前都是使用vivado或者modelsim进行代码仿真,当然modelsim是使用最多的,后面接触了IC并且使用过verdi进行仿真后,觉得Verdi更好用,效率更高。当然笔者是做设计的仿真工具只是为了确保代码的功能及逻辑正确,verdi对于验证工程师来说可能更加重要。

笔者也没对verdi进行深入了研究,就简单的能跑仿真,看波形信号。下面就简单介绍如何使用verdi进行仿真

首先是先写好逻辑代码,激励文件等。然后新建在文件目录下新建如下几个文件,其中rtl文件夹中存放的是设计代码,tb存放测试激励,makefile作为运行脚本,rtl.f是文件列表。

rtl.f文件就是把需要添加到仿真工程的文件都列出来

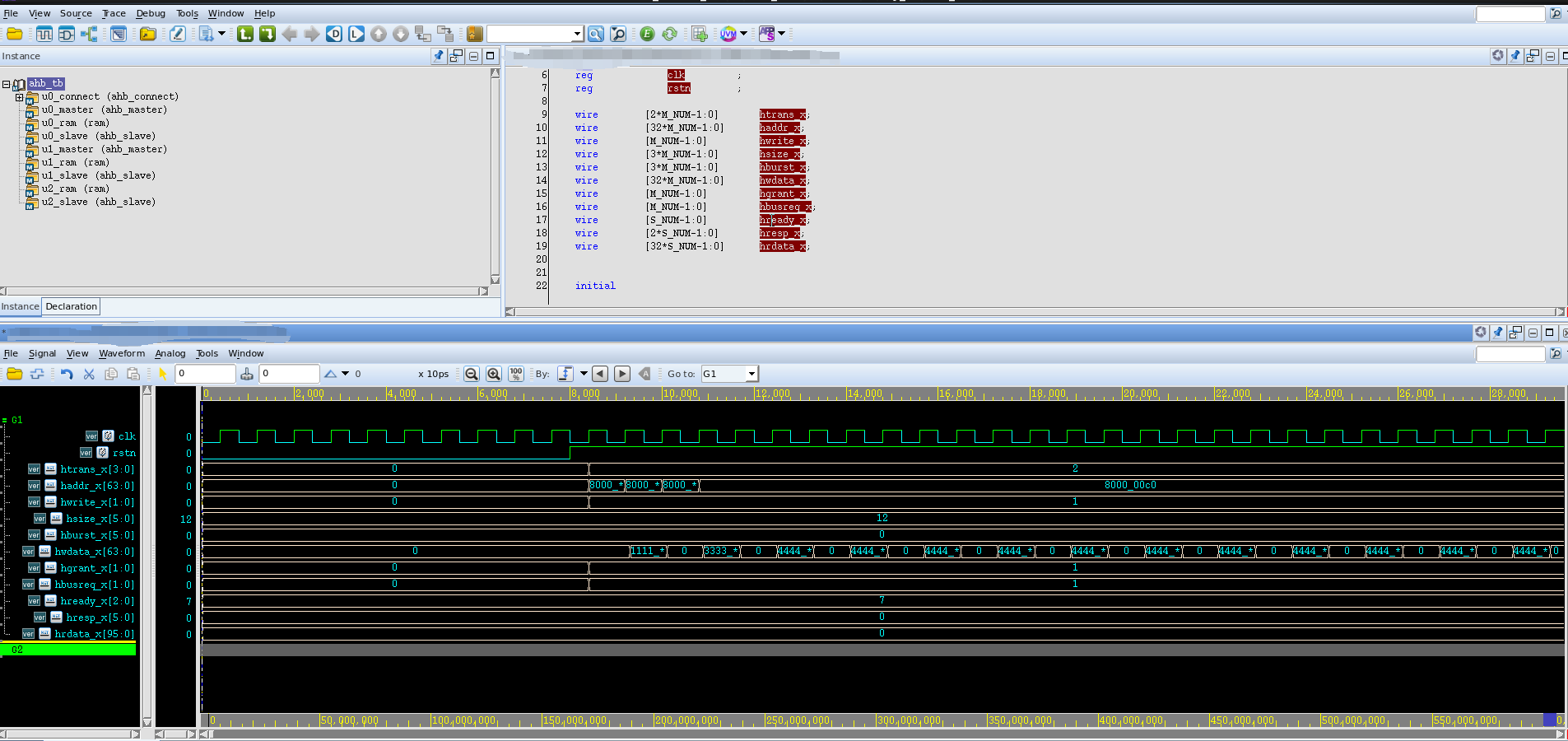

接着就是编写makefile

1 all: clean com sim verdi 2 3 clean: 4 rm -rf 5 6 com: 7 vcs -full64 \ 8 -f rtl.f -R +v2k \ 9 -debug_access+all \ 10 -timescale=1ns/100ps \ 11 -fsdb +define+FSDB \ 12 -l com.log 13 14 sim: 15 ./simv -l sim.log 16 17 verdi: 18 verdi -f rtl.f -ssf *.fsdb -nologo &

vcs -full64 使用EDA逻辑仿真工具编译源代码

-f rtl.f 读取文件列表中的文件

+v2k 支持verilog2001标准

-debug_access+all 保存debug过程中生产的各种文件

-timescale=1ns\100ps 定义仿真时间单位

-fsdb +define+FSDB 添加fsdb的宏定义

-l com.log 保存日志文件com.log

./simv -l sim.log 仿真并保存仿真日志

verdi -f rtl.f -ssf *.fsdb -nologo & 打开verdi并打开对应的波形文件及代码

准备就绪就可以运行指令:make all

运行没报错之后便自动打开verdi,然后根据需要添加波形信号即可进行仿真分析。