Spyglass的Lint检查

SpyGalss是Synopsys(新思科技)推出的一款静态Signoff平台,目前业界唯一可靠的RTL Sign off解决方案,可以帮助客户在设计早期发现潜在问题,保证产品质量,极大的减少设计风险,降低设计成本。笔者在转行做IC前没用过该软件,后面是入行后老员工指导需要用该软件进行跨时钟域检查,他说该软件对时钟域检查比较可靠,但是解决避免跨时钟域这些问题是比较难的,即使工具检查都没问题,实际流片可能也会出现问题。笔者以前一般只用vivado,modelsim等工具进行仿真,仿真完毕没问题就直接综合生成FPGA固件,这就是FPGA与IC的区别吧,芯片比FPGA更加的科学严谨。

以下是Lint检查步骤

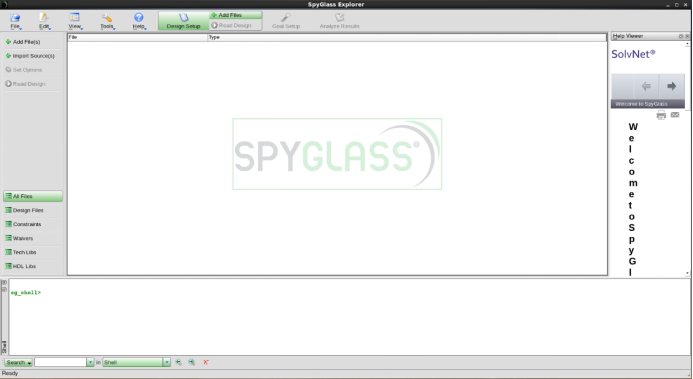

1.打开SpyGlass,在命令端口输入spyglass。

2.点击Add Files添加文件

3.这里以spi文件为例,根据上一步弹出的添加文件框,选中需要添加的文件,然后点击Add,接着点击OK:

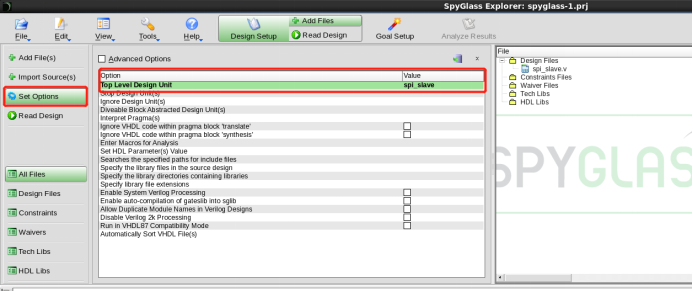

4.点击Set Options,在右边的Value中输入顶层文件的文件名称:

5.点击Read Design,再在左侧点击Run Design Read开始进行设计文件编译和分析,在读取完成后会在下方窗口列出问题,根据报错提示做相应的修改,这里没有报错。如下图所示:

6.勾选Synthesize Netlist,然后重新前一步操作的Run Design Read。

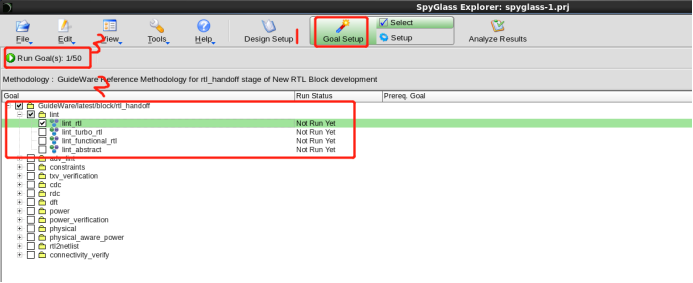

7.点击Goal Setup,然后勾选主窗口下Lint的第一项lint_rtl,然后点击Run Goal(s) ,当运行完成,会自动弹出Analyze Result窗口。这里要一项一项的跑,然后分析,不然错误会被覆盖。

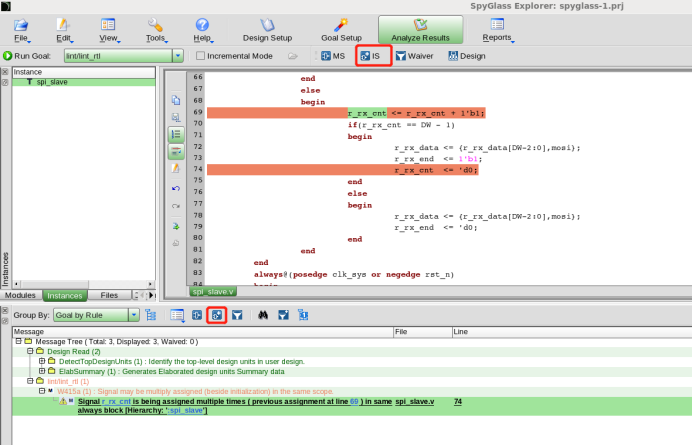

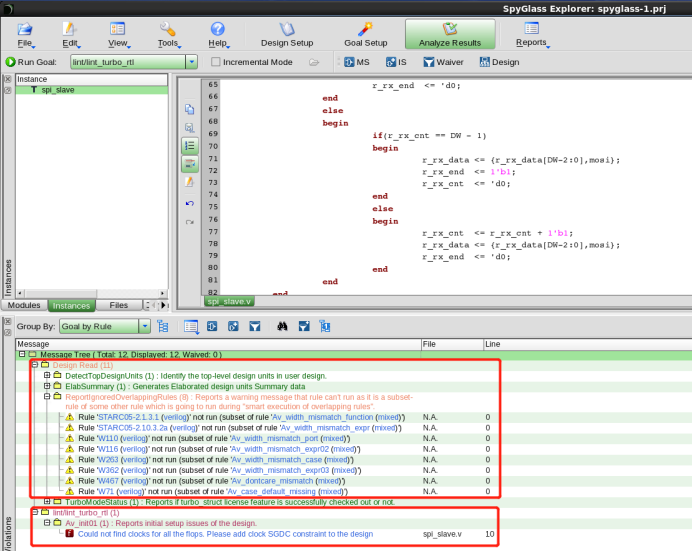

8.等待一段时间,得到分析结果后,首先查看Lint分析结果。首先展开lint/lint_rtl文件夹消息。错误信息以红色显示,警告以橙色显示,信息以绿色显示。选择并展开lint/lint_rtl文件夹。双击第一条违规消息。此时与错误相关的代码会在RTL代码窗口中显示出来,右边框则显示该问题的错误或警告原因,并提示修改的方法。如下所示:

根据警告号W415a在文件《SpyGlass lint Rules Reference Guide》中查找,也可以看右边Help Viewr说明。这里的警告大概是说当if条件满足时,r_rx_cnt的值赋了2次,if里头的赋值会覆盖前面累加的赋值。这里需把r_rx_cnt <= r_rx_cnt + 1’b1放进else里面。

9.点击下面红框处可以查看违规代码的电路框图:

10.修改好上面的代码后重新跑lint_rtl,直到把所有报错和一些潜在问题的警告消除后,再跑lint_turbo_rtl。如下:

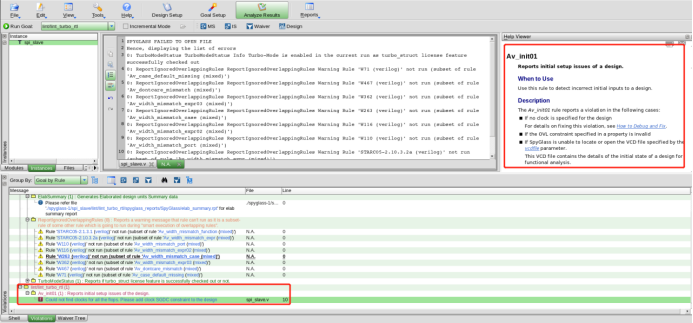

11.根据分析报告可以,可以看到有警告,还有紫色的一些提示:

点击警告,发现Help Viewer也没提示,不管它;点击下面的紫色提示,结合右边框显示内容应该是要添加约束文件:

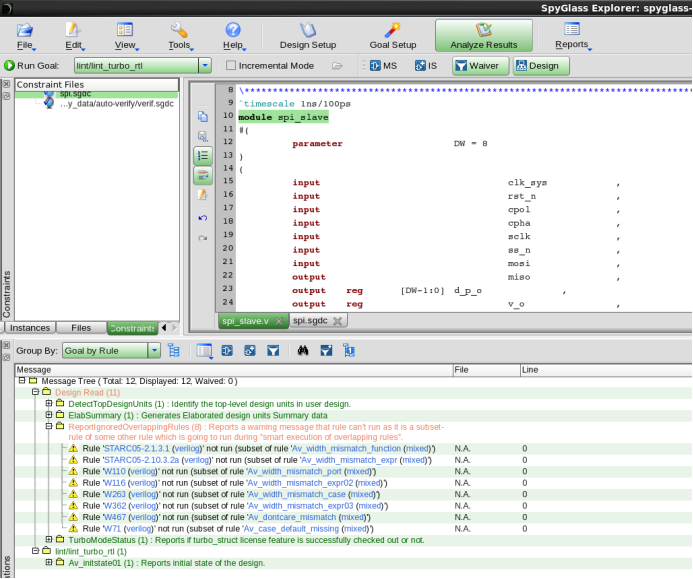

12.根据要求添加约束文件之后,再跑lint_turbo_rtl

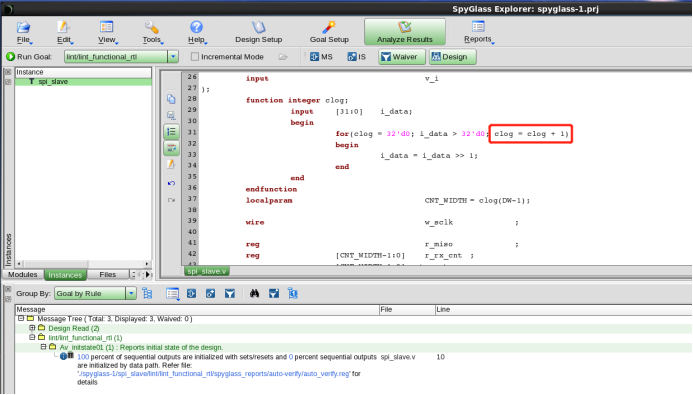

13.接着进行下一步检查,lint_functional_rtl检查。发现有以下警告:

这里提示内容是代码处1’b1是无符号型,clog是有符号型,应该改为一致的数据类型,这里把1‘b1改为1。重新跑lint_functional_rtl,发现问题解决。

结论:Spyglass的lint检查主要是对代码块的语法,还有就是一些违规时序的检查,主要检查一些常见的容易修改的错误。lint的作用更多的是发现潜在的问题,有些警告可以根据实际情况做修改,也可以不用修改。

网上Spyglass的教程很多,讲的都挺详细的,笔者当时也是照着教程一步一步跟着学。这里就不讲脚本指令操作的方式,因为正常使用Spyglass不会完全脱离UI界面。

浙公网安备 33010602011771号

浙公网安备 33010602011771号