modelsim仿真含Xilinx原语代码块

很早之前笔者已经写过关于modelsim仿真的文章了,不过之前笔者做的仿真都是有现成代码块的仿真。对于那些使用原语的代码块进行仿真时则需要产生相关的仿真库,笔者这里使用modeltech64_2020.4,Vivado 2020.1。由于vivado产生的仿真库生成对应一些modelsim的版本,版本不匹配貌似在生成仿真库过程会报错,笔者也遇到过多次,所以笔者这里就使用仿真成功过的modelsim版本及Vivado版本。

一、生成仿真库步骤

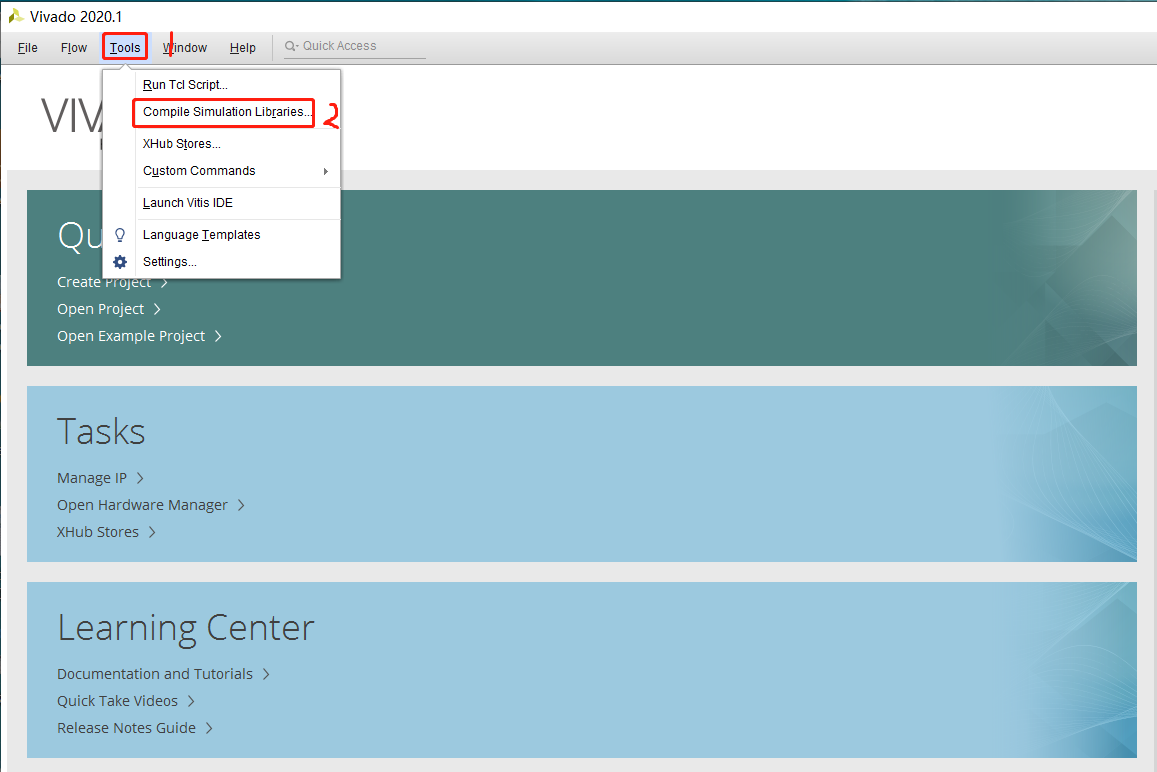

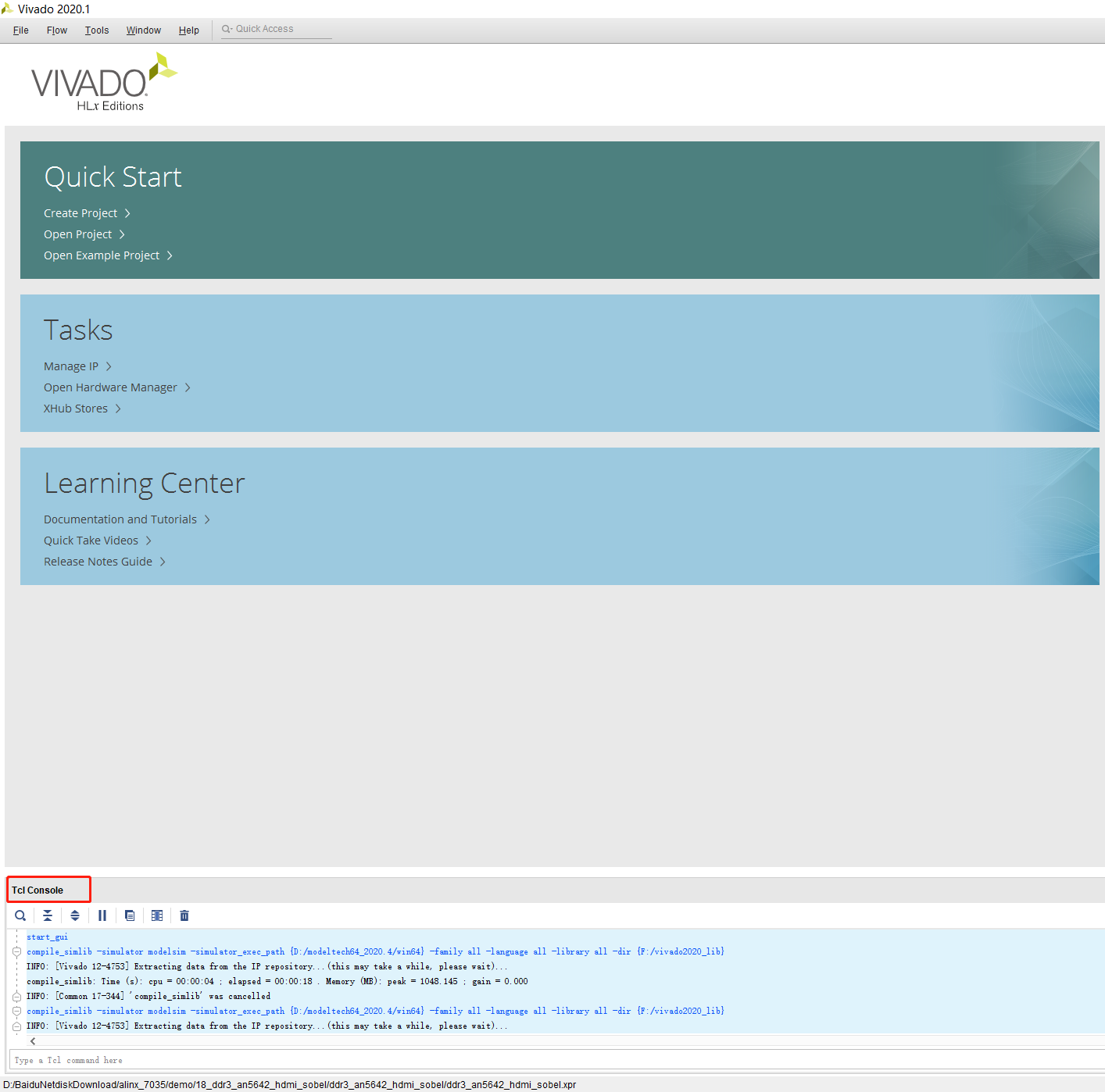

1.打开vivado,先点击Tools,接着选择Compile Simulation Libraries...

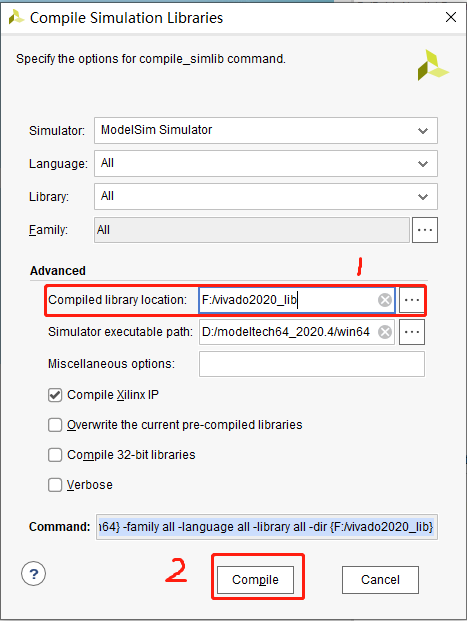

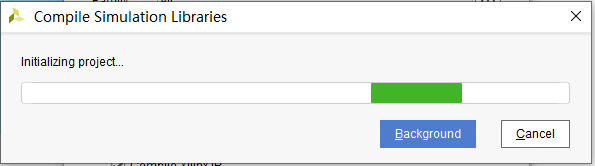

2.先选择仿真库存放的路径地址,接着点击下方的Compile,之后便跳出Initializing project...的显示框

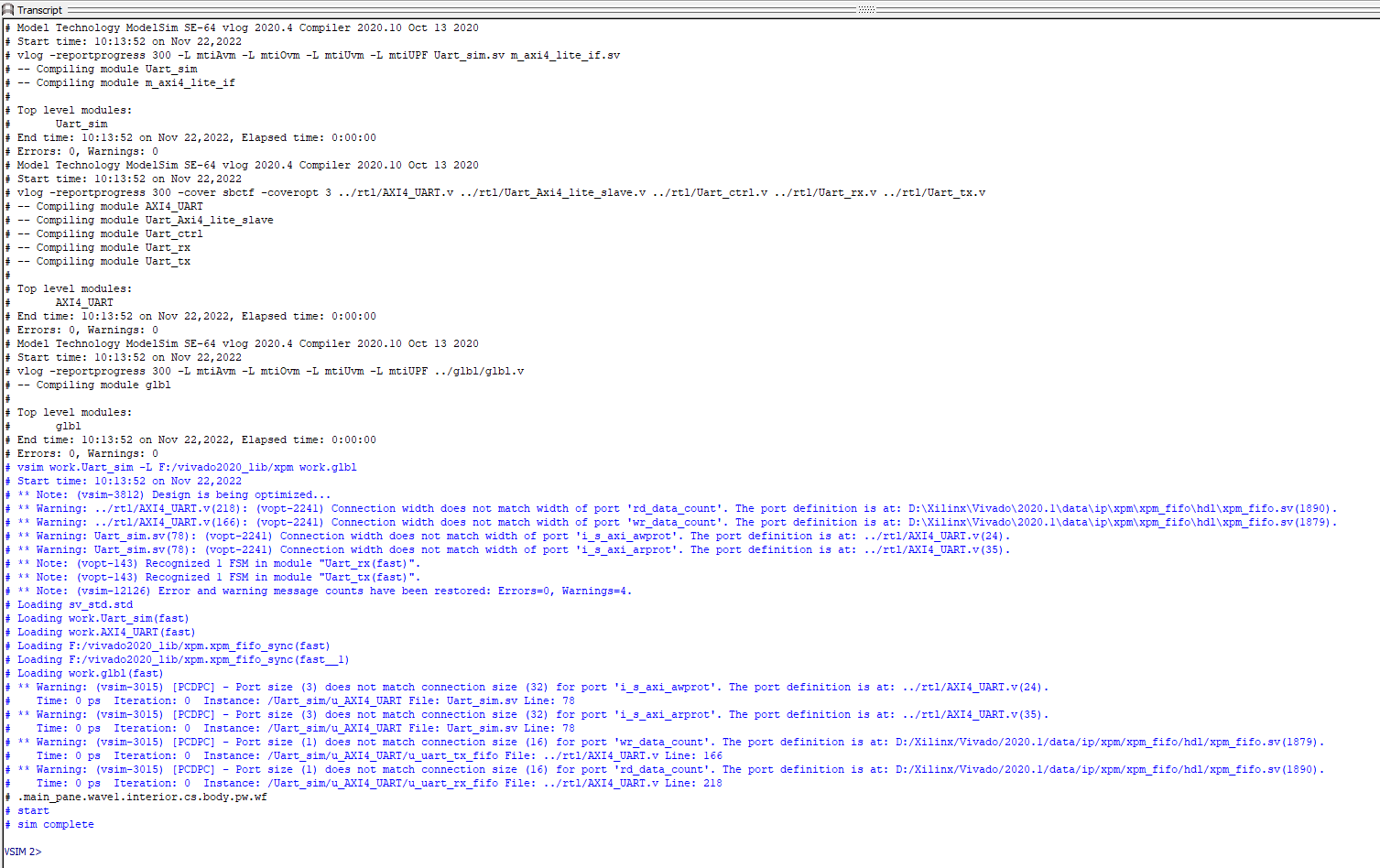

3.此时查看Tcl Console可以查看编译的信息,之后需要等待一段较长的时间。

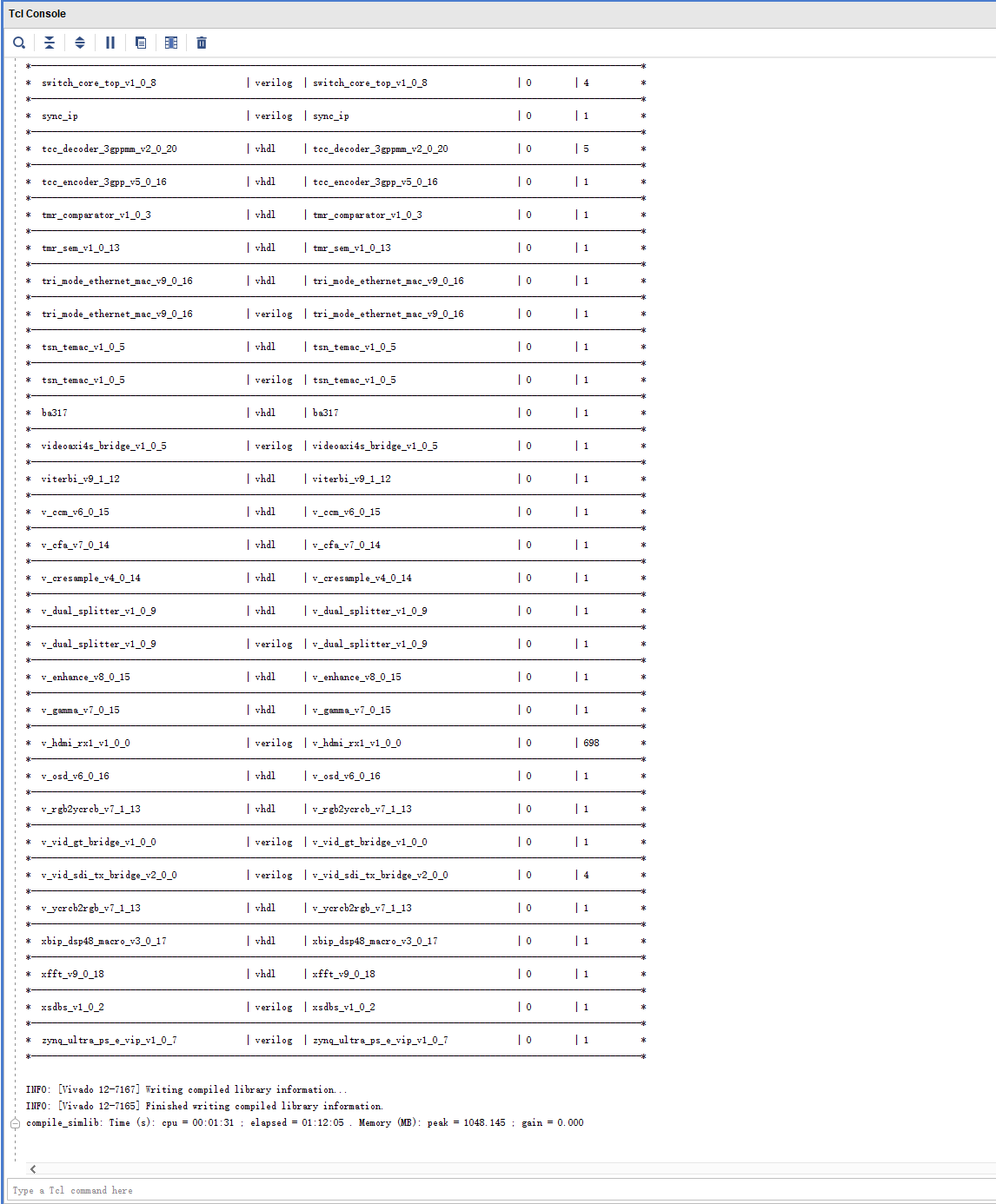

4.编译成功后,Tcl Console显示如下:

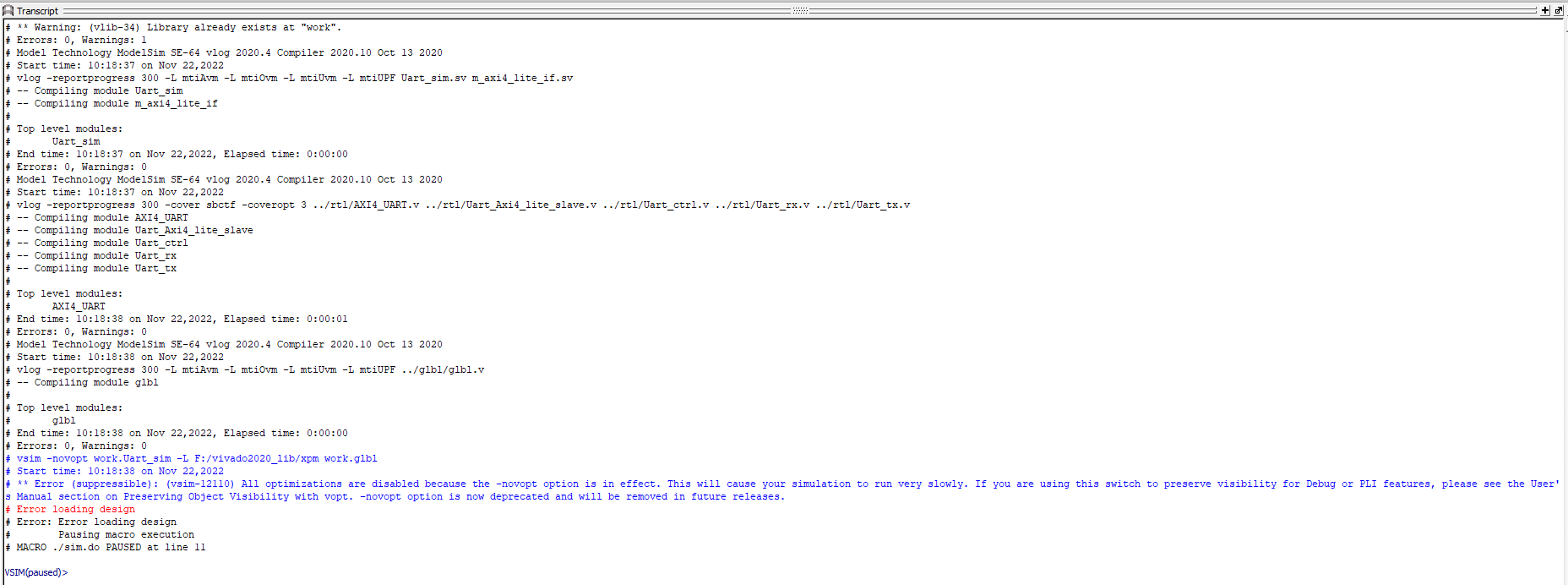

二、编写好modelsim的.do文件

下面的代码中把上面步骤生成的仿真库添加进来,第10行-L F:/vivado2020_lib/xpm就是起到了这个作用,这里需要对含xpm_fifo_sync原语的代码块进行仿真,所以后面是xpm。需要注意的是如果10行中的代码用旧版本的vsim -novopt work.Uart_sim -L F:/vivado2020_lib/xpm work.glbl,就会出现下图2中的错误,这是新版本modelsim需要注意的事。-voptargs="+acc"是允许自动优化,可加可不加。

1 #删除work工作目录 2 quit -sim 3 .main clear 4 5 vlib work 6 vlog -L mtiAvm -L mtiOvm -L mtiUvm -L mtiUPF *.sv 7 vlog -cover sbctf -coveropt 3 ../rtl/*.v 8 vlog -L mtiAvm -L mtiOvm -L mtiUvm -L mtiUPF ../glbl/glbl.v 9 10 vsim -voptargs="+acc" work.Uart_sim -L F:/vivado2020_lib/xpm work.glbl 11 #观察DUT的信号波形 12 add wave -position insertpoint sim:/Uart_sim/u_AXI4_UART/u_Uart_tx/* 13 view -new wave 14 add wave -position insertpoint sim:/Uart_sim/u_AXI4_UART/u_Uart_rx/* 15 16 run 10ms

三、直接点击run.bat,自动仿真完成

代码用的是前面UART的相关代码《基于Axi4_lite的UART串口Verilog代码实现》。仿真完成如下: