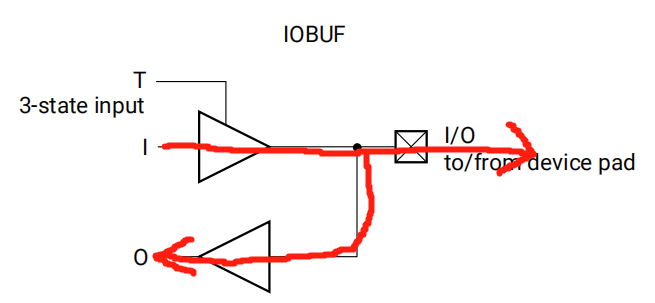

IOBUF的用法

IOBUF这个原语在Xilinx的原语手册有说明,主要作为三态端口使用,作用是把FPGA内部三态信号与外部的双向信号连接。对于UltraScale

系列芯片说明文档为:ug974-vivado-ultrascale-libraries.pdf,对于Z7系列芯片说明文档为:ug953-vivado-7series-libraries.pdf。可自行到xilinx官网下载。笔者粗略对比两文档中的IOBUF原语,发现差别不大,Z7多了些参数设置,大多情况默认即可。下面为UltraScale文档IOBUF部分说明:

根据上述大段的英文介绍笔者大概了解关键信息:当信号T为1时,IOBUF作为输入;T为0时IOBUF作为输出。

实际使用时,方向引脚对应T,代码模块输出对应IOBUF的I,代码块输入对应IOBUF的O。需要注意代码块的引脚方向信号必须是1为输入,0为输出,IOBUF的IO脚直接连FPGA引脚。

UltraScale官方代码如下:

1 // IOBUF: Input/Output Buffer 2 // UltraScale 3 // Xilinx HDL Language Template, version 2020.1 4 IOBUF IOBUF_inst ( 5 .O(O), // 1-bit output: Buffer output 6 .I(I), // 1-bit input: Buffer input 7 .IO(IO), // 1-bit inout: Buffer inout (connect directly to top-level port) 8 .T(T) // 1-bit input: 3-state enable input 9 ); 10 // End of IOBUF_inst instantiation

Z7官方代码如下:

1 // IOBUF: Single-ended Bi-directional Buffer 2 // All devices 3 // Xilinx HDL Language Template, version 2020.1 4 IOBUF #( 5 .DRIVE(12), // Specify the output drive strength 6 .IBUF_LOW_PWR("TRUE"), // Low Power - "TRUE", High Performance = "FALSE" 7 .IOSTANDARD("DEFAULT"), // Specify the I/O standard 8 .SLEW("SLOW") // Specify the output slew rate 9 ) IOBUF_inst ( 10 .O(O), // Buffer output 11 .IO(IO), // Buffer inout port (connect directly to top-level port) 12 .I(I), // Buffer input 13 .T(T) // 3-state enable input, high=input, low=output 14 ); 15 // End of IOBUF_inst instantiation

根据三态门的原理可以通过代码把3态门表示出来,为了不与IOBUF的名称相冲突,该模块改为PIN脚的PIOBUF:

1 module PIOBUF 2 ( 3 inout IO , 4 input T , 5 input I , 6 output O 7 ); 8 9 assign O = IO; 10 assign IO = ~T ? I : 1'bz; 11 12 endmodule

1 module PIOBUF 2 ( 3 inout IO , 4 input T , 5 input I , 6 output O 7 ); 8 9 assign O = T ? IO : I; 10 assign IO = ~T ? I : 1'bz; 11 12 endmodule

以上便是最常见的两种三态门写法,很多双向口都是使用该方法。实际上这两种方式是一样的,assign语句是线型,所以当T为0时,直接把I的值赋给O与先把值赋给IO,IO再赋给O,结果是一样的。

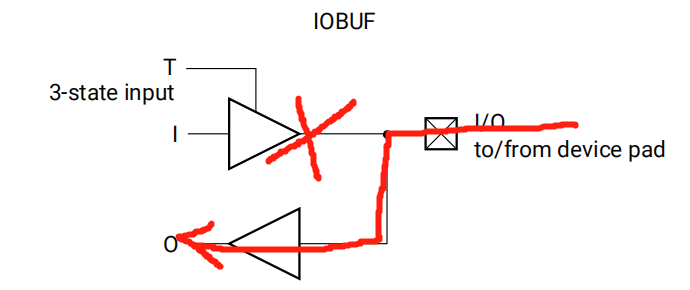

根据Xilinx的IOBUF原语T=0时,I与O信号是连接的特性,可以实现一些接口的小妙用。比如对于音频接口I2S,如果RX与TX作为两个模块,在FPGA作为时钟WCLK,BCLK输出,同时使用数据输出输入时,那么WCLK,BCLK分别使用IOBUF连接可以简单的解决既能发送数据,也能采样接收的数据。也可以在GPIO使用,三态口接IOBUF,输出高低电平时可以通过读取输入得到实际输出状态。

T=1时,3态的原语的I/O端口到input的路径是断路,不连通的:

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步