第十四届智能车培训 PLL锁相环

什么是锁相环?

PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时脉讯号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步。一般的晶振由于工艺与成本原因,做不到很高的频率,而在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路就可以实现稳定且高频的时脉冲讯号。

锁相环主要作用:

单片机使用锁相环(PLL)功能能够获得更高的总线频率,这对于需要提高单片机运行速度的场合非常必要。

锁相环相关寄存器简介:

1、CRG时钟合成寄存器(SYNR)

该寄存器低6位有效,有效值0~63

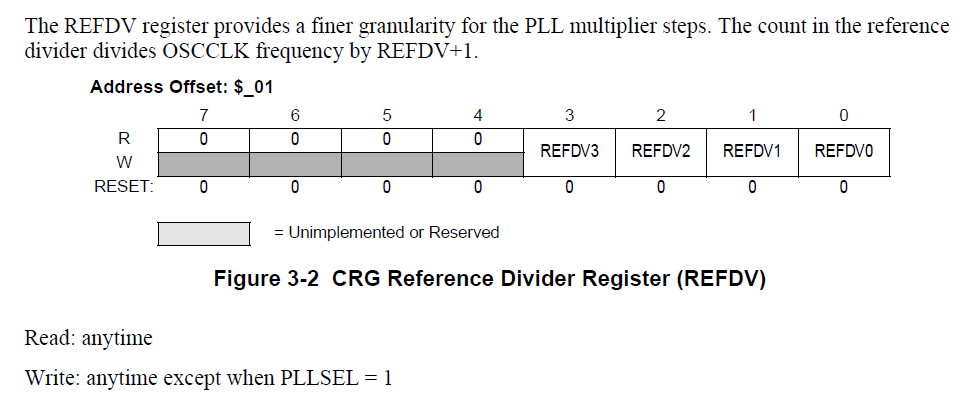

2、时钟分频寄存器(REFDV)

该寄存器有效位为寄存器的低4位,有效值为0~15

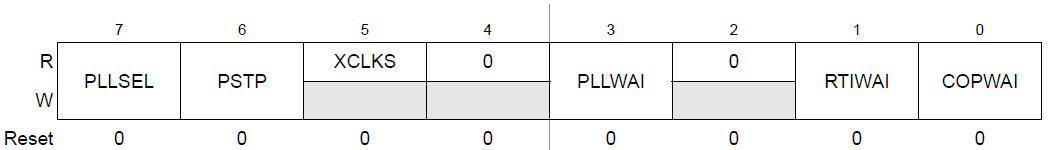

3、时钟选择寄存器(CLKSEL)

PLLSEL置1:Bus Clock = PLLCLK / 2 置0:Bus Clock = OSCCLK / 2)

设置锁相环计算方法

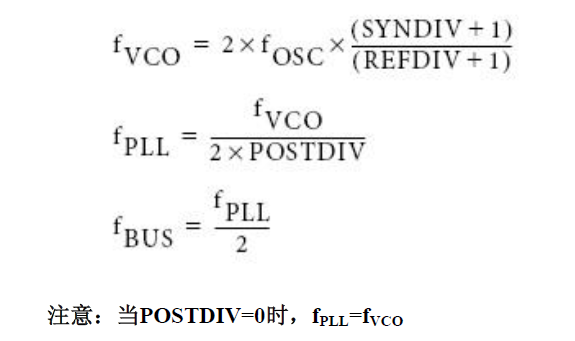

配置锁相环的主要目的是为了得到新的总线时钟,其配置主要依据下面的三个公式:

Fosc系统总线时钟频率

Fpll锁相环时钟频率

Fbus总线时钟频率

配置流程:

1. CLKSEL=0X00; // 在CLKSEL最高位为0时才能设置其他寄存器

2. 设置相关参数 SYNR ( 时钟合成寄存器 ) REFDY ( 时钟分频寄存器 )

3. 等待 PLL 稳定 该部分用到的寄存器 CRGFLG_LOCK 当 CRGFLG_LOCK=1 表示时钟频率已经稳定

4、CLKSEL=0x80 ;//使用PLL时钟

例程代码:

void PLL_Init(void) { CLKSEL=0; //时钟选择寄存器的最高位为0 Bus Clock(总线时钟)= OSCCLK / 2) // 为1 Bus Clock(总线时钟)= PLLCLK / 2) // 在CLKSEL最高位为0时才能设置其他寄存器 SYNR=0x44;//时钟合成寄存器 0100 0100 因低六位有效所以最大为63 REFDV=0x81;//时钟分频寄存器 1000 0001因低四位有效所以最大为15 外部晶振fosc=8M,BUS clock=20M _asm(nop); //空操作 _asm(nop); while(!CRGFLG_LOCK==1); //当CRGFLG_LOCK!=1时 //CRGFLG_LOCK=1 表示时钟频率已经稳定 CLKSEL=0X80; //时钟选择寄存器的最高位 // 在CLKSEL最高位设置为1其他寄存器不允许设置 }

void PLL(void) { SYNR=0x01; //时钟主频:PLL clock = 2*OSC CLOCK*(1+SYNR)/(1+REFDV) REFDV=0x00; // PLL clock = 32MHz = 2* 8 * 2 / 1 while(!(CRGFLG_LOCK==1)); //等待晶振稳定 CLKSEL_PLLSEL=1; //对时钟主频/2得到 //总线时钟:BUS CLOCK = PLL CLOCK / 2 //BUS CLOCK =16MHz = 32 /2 } //ECT模块的输出比较功能设置 //通道0

//根据元件的工作频率选择单片机合适的主频率 //system clock 8MHZ(系统时钟) void PLL(void) //设定总线频率 (超频) { CLKSEL=0x00; //初始化PLL前先使用外部晶振(晶振时钟) SYNR=0x01; //时钟主频:PLL clock = 2*OSC CLOCK*(1+SYNR)/(1+REFDV) REFDV=0x00; //got 32 MHZ = 2*8*2/1 while(!(CRGFLG_LOCK==1)); //等待晶振稳定(时钟校正同步) CLKSEL_PLLSEL=1;//(CLKSEL=0x80;) //BUS CLOCK 16 MHZ = PLL CLOCK / 2 (选定锁相环时钟)(PLLSEL置1:Bus Clock = PLLCLK / 2) }