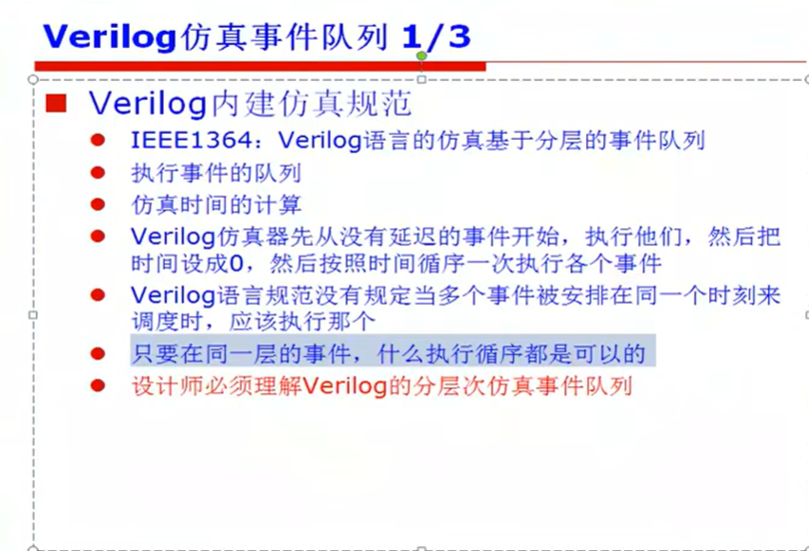

VCS

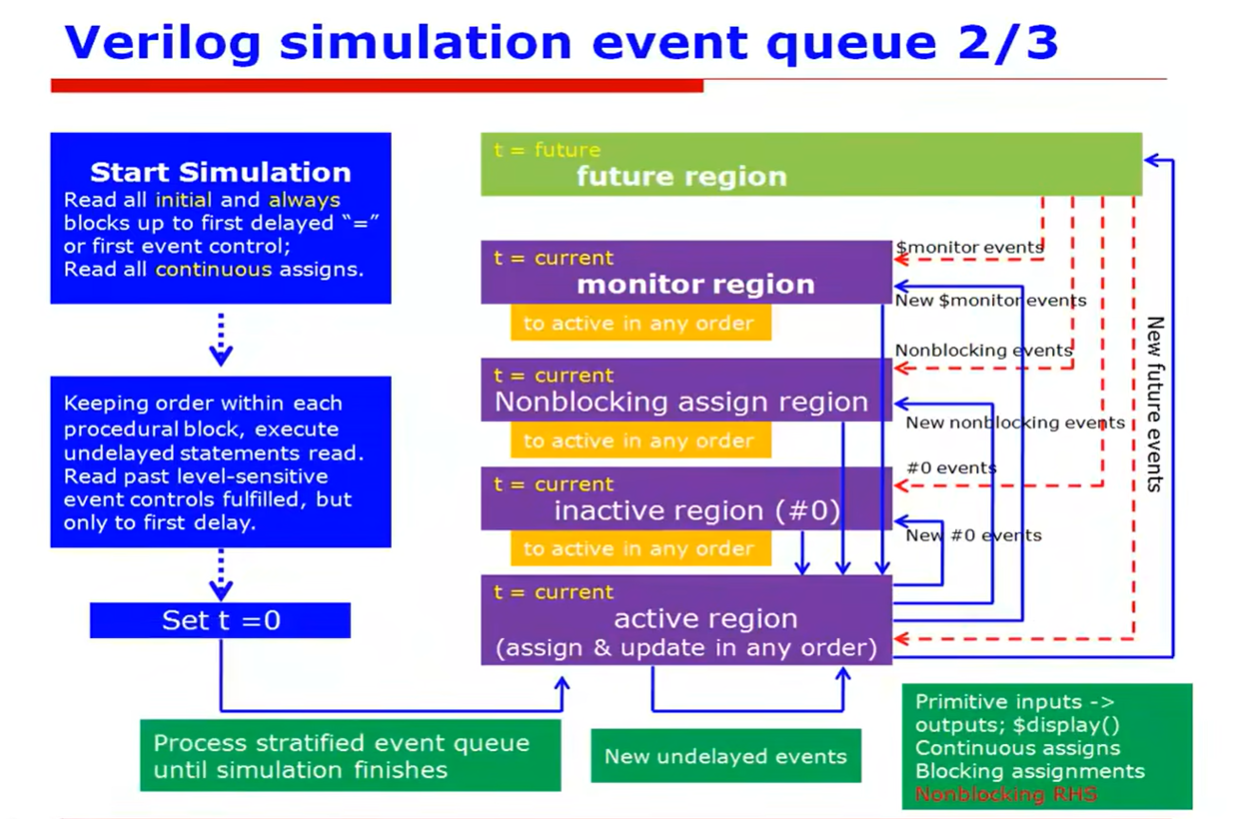

VCS处理流程

--首先把模块读进来

--按照固定的顺序放在队列,先执行没有延迟的语句

--active_region (执行UDP原语、display()、assign、阻塞赋值、非阻塞赋值的计算)

--inactive_region #0

--Nonblocking assign region 非阻塞赋值

--monitor region 只有当相关变量发生变化才进行执行

--future region

scope命令显示当前目录

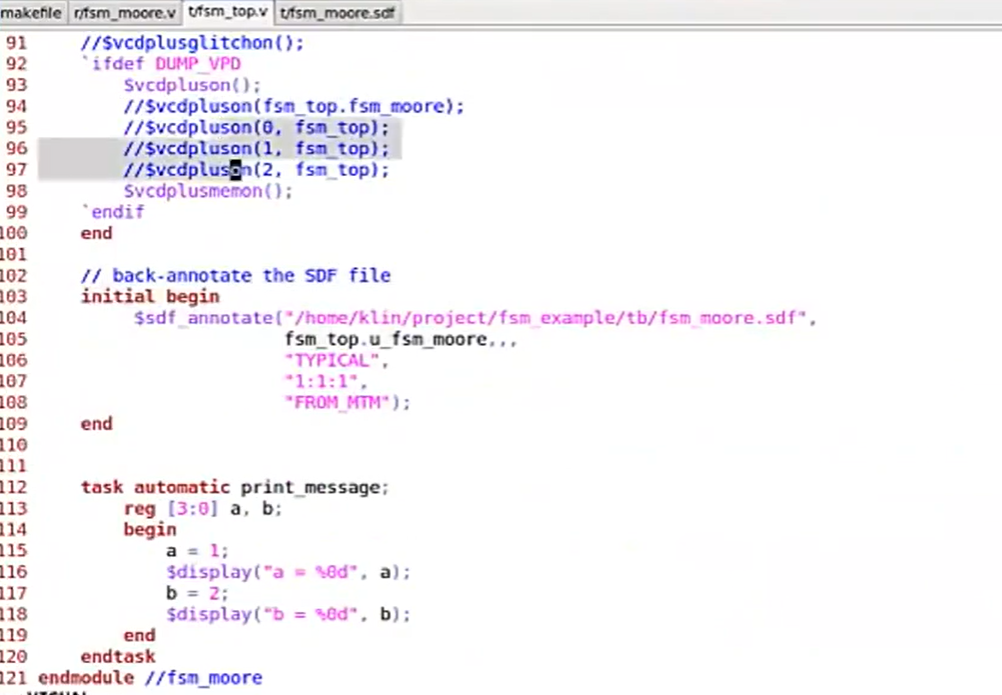

VCS后仿真

------主要关注toggle覆盖率

RTL经过DC后产生带有时序信息的门级网表(.v文件)并生成SDF(standard delay format)

后仿真的仿真文件里边加入时序信息反标注文件

$sdf_annotate(“sdf文件位置”,

SDF文件反标注的模块,(这个参数省略),(这个参数省略),

“TYPICAL(指定延迟方式,也可以MAX、MIN)”,

“1:1:1(缩放因子,时间比例,最小延迟可以乘多少,一般不变)”

“FROM_MTM”);

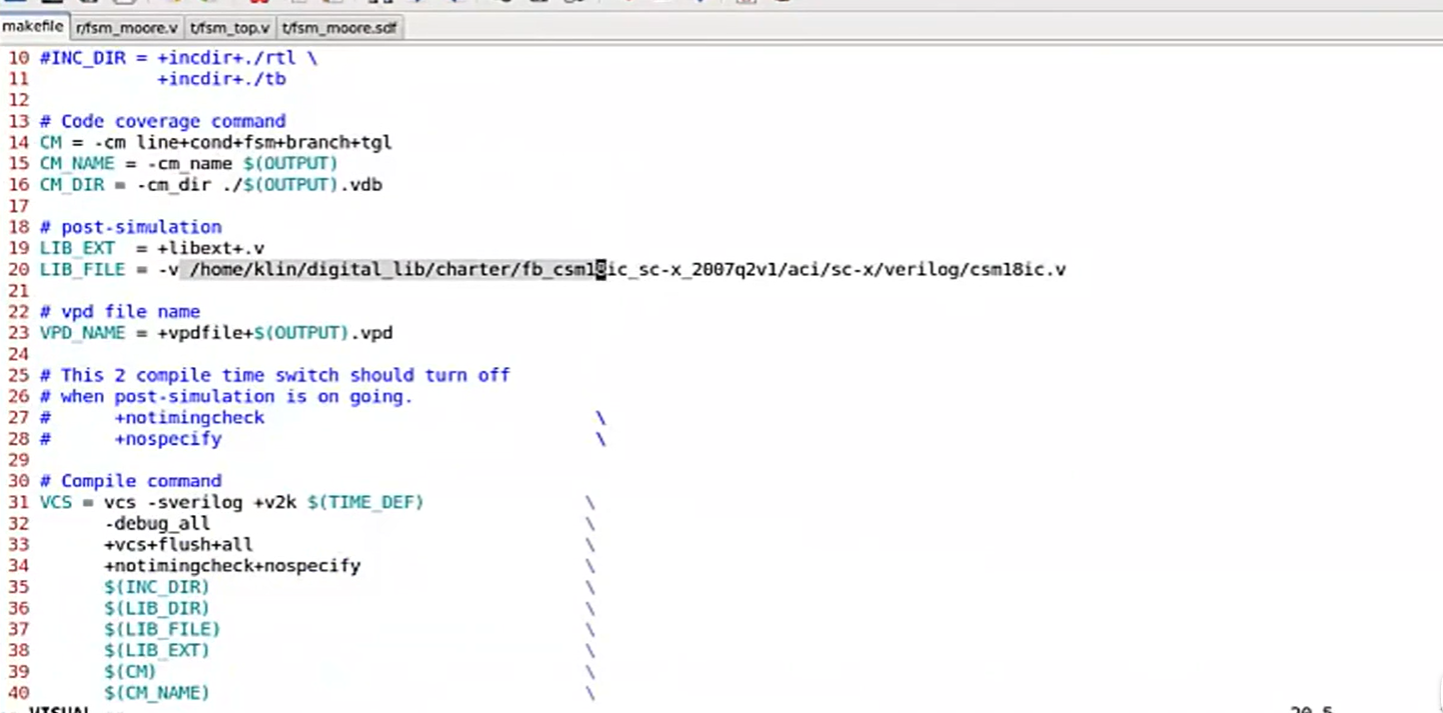

后仿真需要在Makefile中用LIB的后缀类型和位置 -v或-y