IP核:XDMA学习

知识:

XDMA效率没有RIFFA高,最高似乎只支持1288位宽;

输出的用户时钟是250MHZ;

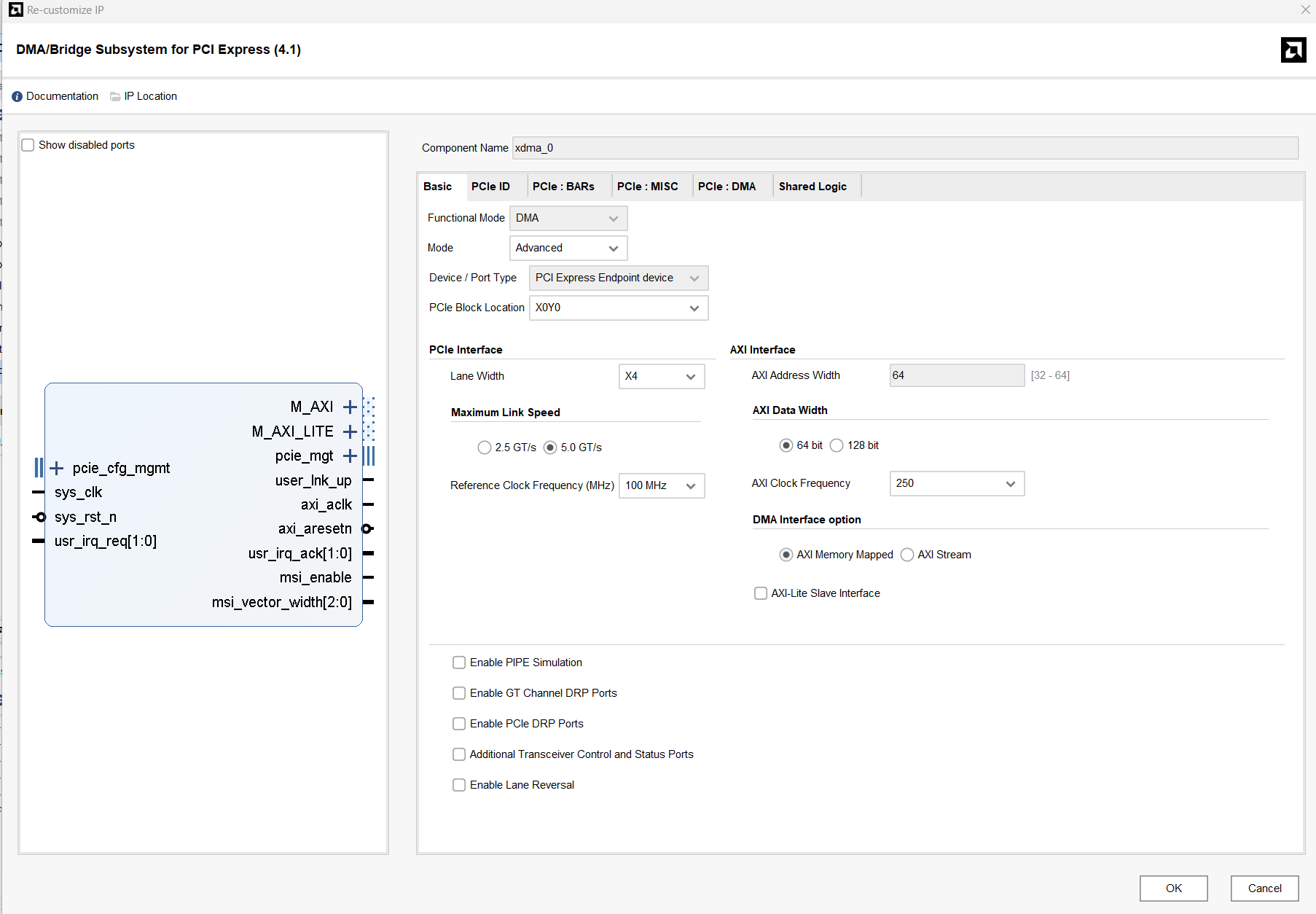

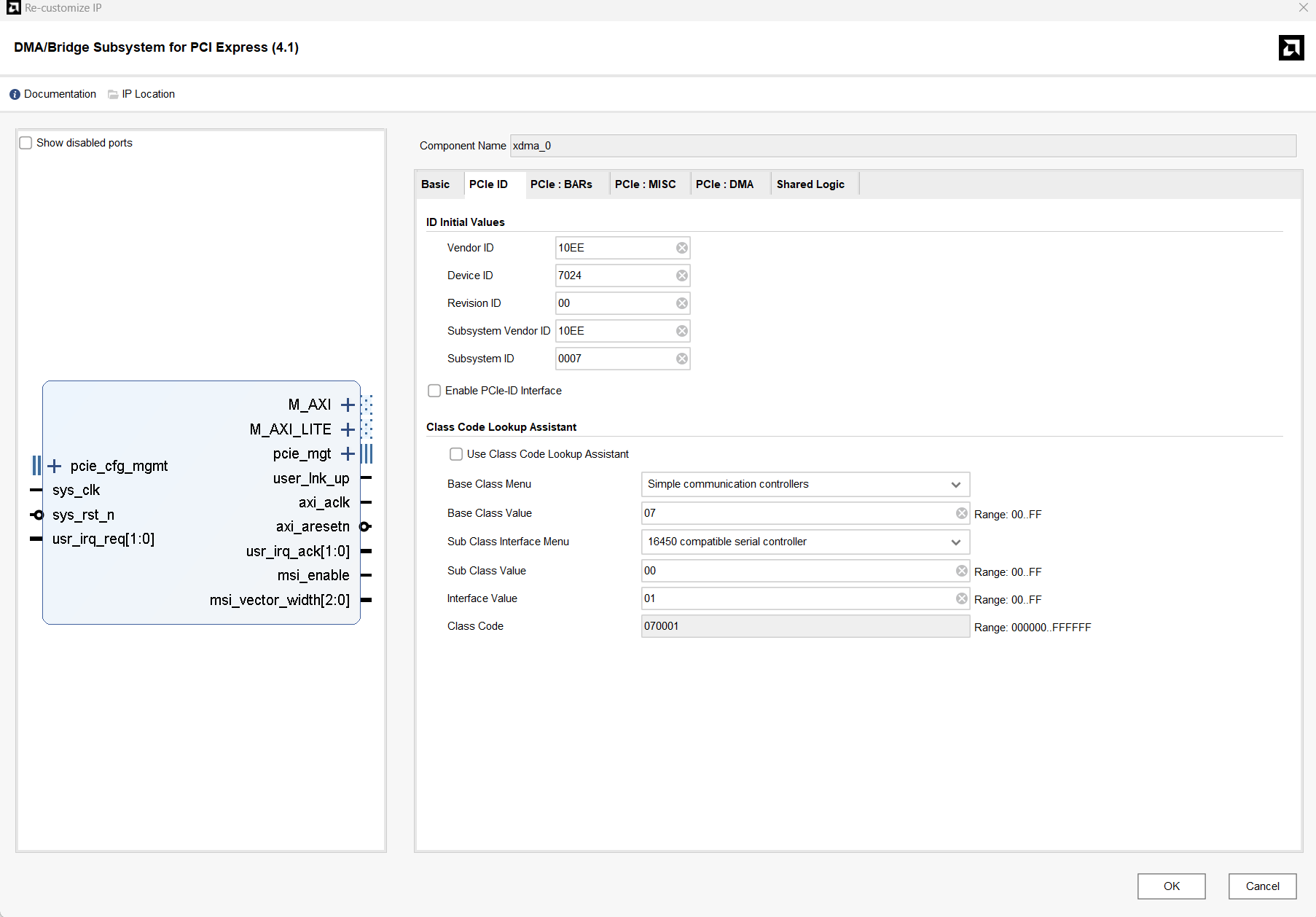

IP核配置:

参考:

https://docs.amd.com/r/zh-CN/pg195-pcie-dma/

具体:

重要:

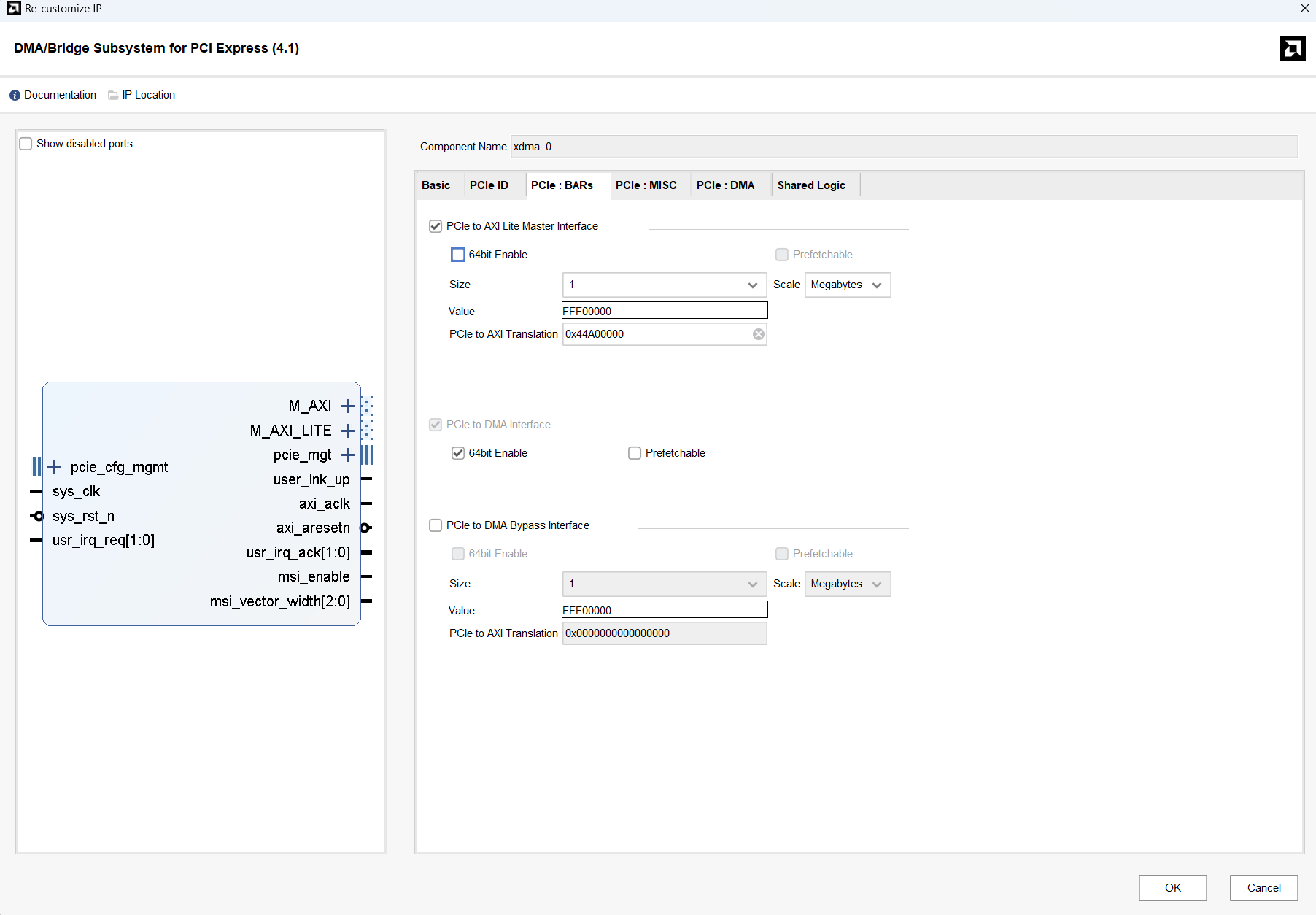

PCIe:BARs标签页

该标签页主要用于配置 BAR,所谓的使能和配置各接口 interface,其实质是配置不同的 BAR,首先介绍下什么是 BAR。 BAR 是 Base Address Register 的缩写,译为基址寄存器。 通过将读取或写入请求映射到基址寄存器( BAR),可以从主机访问 XDMA 内部的配置和状态寄存器以及用户逻辑中的配置和状态寄存器。 XDMA 根据 BAR 命中,将请求路由到适当的位置。 比如,对于 PCIe to AXI-Lite Master (BAR0)地址映射, 命中 PCIe 到 AXI4-Lite Master 的事务将路由到 AXI4-Lite 内存映射用户接口。该接口支持 32 位地址空间和 32 位读取和写入请求。 PCIe to AXI-Lite Master (BAR0)地址映射可由用户逻辑定义。

BAR分2种大小:

32位BAR:地址空间最小可达128字节或者最大可达2千兆字节(GB)。用于内存或I/O。

64位BAR:地址空间最小可达128字节或者最大可达8艾字节(EB)。仅用于内存。

BAR 也可分为两种类型(Type)——I/O 和内存:

I/O: I/O BAR 只能采用 32 位;“可预取 (Prefetchable)”选项不适用于 I/O BAR。仅限针对传统 PCIExpress 端点才能启用 I/O BAR。

内存(Memory):内存BAR可采用64位或32位,并且可预取。

与 BAR 寄存器相关的选项含义:

Size(大小):可用大小范围取决于所选 PCIe 器件/端口类型和 BAR 类型;

Value(值):基于当前选择分配给 BAR 的值;

64bit Enable:是否使用 64 位BAR;

Prefetchable(可预取):识别内存空间预取功能。

每个 BAR 空间可以单独选择 64bit Enable 选项。每个 64 位 BAR 空间都可以选择是否预取。

AXI4‑Lite 是使用BRAM实现的用户逻辑寄存器;

BAR 的选择是可配置的。默认情况下,DMA 位于 BAR 0(64 位),AXI4‑Lite 主接口则位于 BAR 2(64 位)。这些选择可根据用户需求而变;

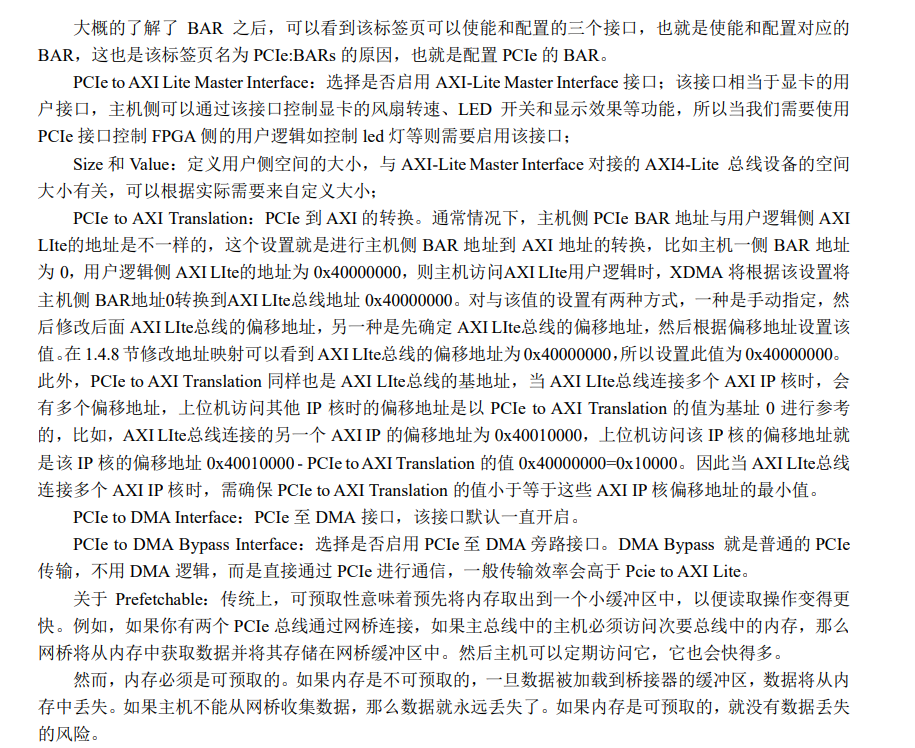

PCIe to AXI Lite Master Interface:

选择是否启用 AXI-Lite Master Interface 接口;该接口相当于显卡的用户接口, 主机侧可以通过该接口控制显卡的风扇转速、 LED 开关和显示效果等功能,所以当我们需要使用PCIe 接口控制 FPGA 侧的用户逻辑如控制 led 灯等则需要启用该接口。

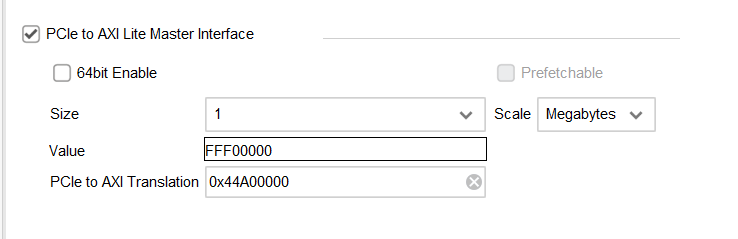

PC的内存域地址与PCIe域地址的映射关系:PCIe to AXI Translation这个地址要与Address Editor中AXI_Lite设置的地址大小一致。

PCIe to AXI Translation:PCIe 到 AXI 的转换。主机一侧 BAR 地址为 0, 用户逻辑侧 AXI LIte的地址为 0x40000000,则主机访问AXI LIte用户逻辑时, XDMA 将根据该 设置将主机侧 BAR地址0转换到AXI LIte总线地址 0x40000000。对与该值的设置有两种方式,一种是手动指定,然后修改后面 AXI LIte总线的偏移地址,另一种是先确定 AXI LIte总线的偏移地址,然后根据偏移地址设置该值。例如修改地址映射AXI LIte总线的偏移地址为 0x40000000,所以设置此值为 0x40000000

此外, PCIe to AXI Translation 同样也是 AXI LIte总线的基地址,当 AXI LIte总线连接多个 AXI IP 核时,会有多个偏移地址,上位机访问其他 IP 核时的偏移地址是以 PCIe to AXI Translation 的值为基址 0 进行参考的,比如, AXI LIte总线连接的另一个 AXI IP 的偏移地址为 0x40010000,上位机访问该 IP 核的偏移地址就是该 IP 核的偏移地址 0x40010000 - PCIe to AXI Translation 的值 0x40000000=0x10000。 因此当 AXI LIte总线连接多个 AXI IP 核时,需确保 PCIe to AXI Translation 的值小于等于这些 AXI IP 核偏移地址的最小值

参考:

https://blog.csdn.net/Njustxiaobai/article/details/132874083

https://blog.csdn.net/kunkliu/article/details/108812595

PCIE to AXI Lite Master Interface:不勾选 , 我们不使用这个接口来访问用户逻辑,如果有人看过《PCIE_xdma教程_LINUX.pdf》这个pdf文档的话,

应该知道这个文档里讲的是使用这个接口来进行访问用户逻辑,而不使用DMA Bypass 接口,我刚开始也是参照这个文档使用这个接口,但是后面在使用的时候发现了问题,

这个接口的数据输出是经过XDMA内部过滤的,

也就是说这个接口出来的地址并不是所有的都能给用户使用,

有部分地址是用来对XDMA的寄存器配置使用的,

容易造成用户地址和配置地址混合,

如果用户地址只有几个十几个还好,要是有几十上百个的话,这个接口并不实用。

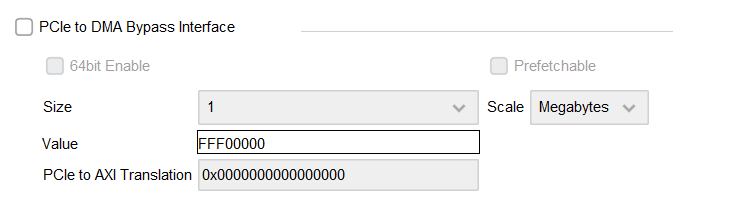

PCIe to DMA Interface: PCIe 至 DMA 接口,该接口默认一直开启,prefetchable和nonprefetchable(可预取和不可预取)。

PCIe to DMA Bypass Interface: 选择是否启用 PCIe 至 DMA 旁路接口。 DMA Bypass 就是普通的 PCIe传输, 不用 DMA 逻辑, 而是直接通过 PCIe 进行通信, 一般传输效率会高于 PCIe to AXI Lite。

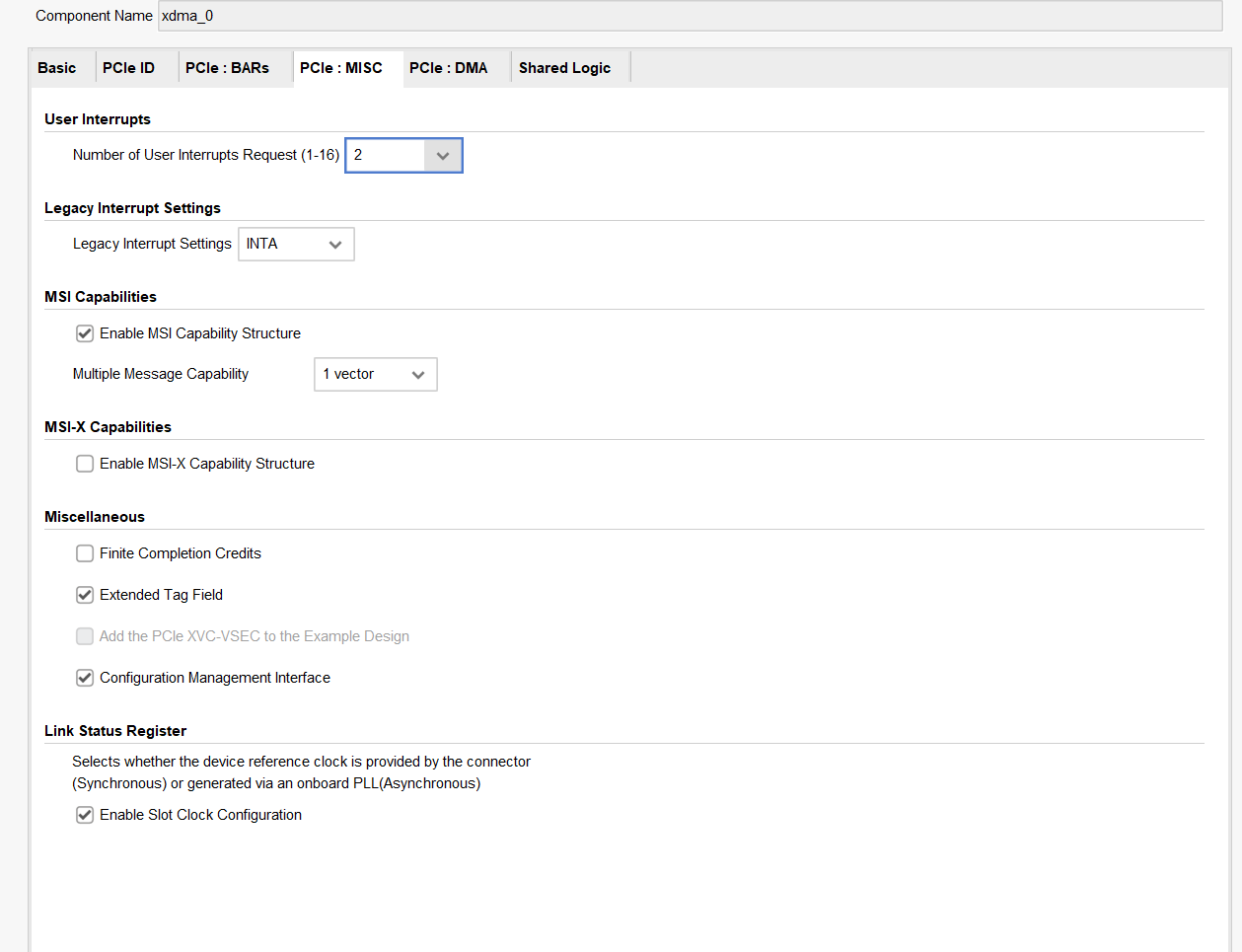

Number of User Interrupt Request:用户中断请求数,最多可以选择 16 个用户中断请求; Legacy Interrupt Settings:可以选择传统中断之一:INTA,INTB,INTC 或 INTD; MSI Capabilities:默认情况下,启用 MSI 功能,并且启用 1 个向量,最多可以选择 32 个向量。通常,Linux 仅将 1 个向量用于 MSI,可以禁用此选项; MSI-X Capabilities:使能 MSI-X 功能; Finite Completion Credits(Advanced 配置模式下有):在支持有限完成信用的系统上,可以启用此选项以获得更好的性能; Extended Tag Field:扩展标签字段,默认情况下,使用 6 位完成标签。对于 UltraScale 和 Virtex-7 器件, 扩展标签选项提供了 64 个标签。对于 UltraScale +器件,扩展标签选项提供 256 个标签。如果未选择扩展标签选项,则 DMA 将 32 个标签用于所有设备 Configuration Management Interface:是否使用 PCIe 配置管理接口; 关于 MSI-X 中断:用户可以尝试使用 MSI-X 中断,而不是 MSI 或传统中断。使用 MSI-X 中断,数据 速率要优于使用 MSI 或基于传统中断的设计。

中断向量: MSI 中断和 MSI-X中断只能选择一个,否则会报错,如果选择了 MSI 中断,则可以选择 Legacy中断,如果选择了MSI-X中断,那么MSI必须取消选择,同时Legacy也必须选择None。此 IP 对于7系列设置有这么个问题,如果使用Ultrascale 系列,则可以全部选择。 对PCIE来说只有三种中断:MSI-X、MSI、Legacy。而user interruput是逻辑侧的控制中断口。 中断优先级为:MSI-X>MSI>Legacy 在申请中断时req需要一直保持为高,直到响应ack来了后,才能拉低,然后进行下一次申请; 由于逻辑侧的中断与主机侧的中断是通过优先级来对应的,因此同一时刻只有一种中断。

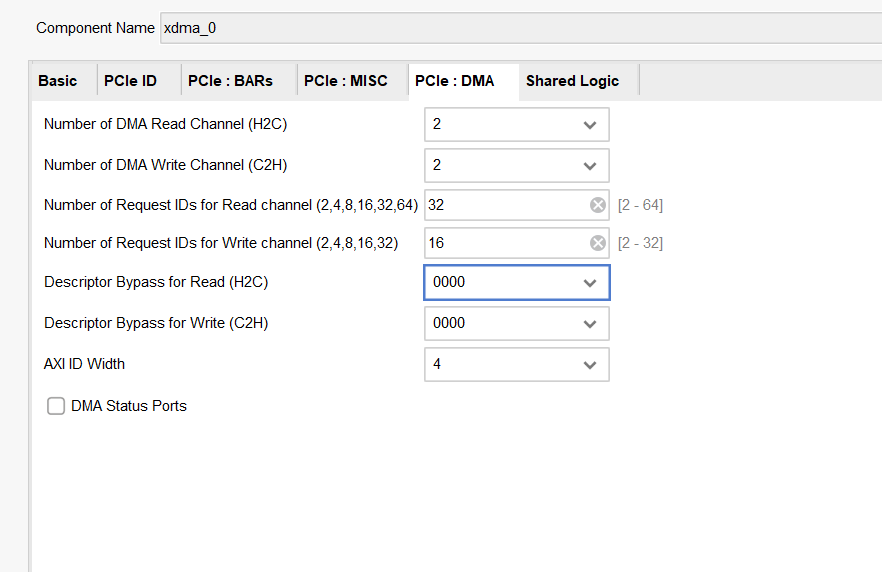

Number of Read Channels:主机到 PCIe 卡(H2C)的 DMA 读通道数,对于 7 系列 Gen2 IP,最多两个(通道数越多,同等情况下传输速率越快); Number of Write Channels:PCIe 卡到主机(C2H)的 DMA 写通道数,对于 7 系列 Gen2 IP,最多两个(通道数越多,同等情况下传输速率越快); Number of Request IDs for Read channel:读通道的请求 ID 数,即每个通道的最大未完成请求数,可用的选择是从 2 到 64; Number of Request IDs for Write channel:写通道的请求 ID 数,即每个通道的最大未完成请求数,可用的选择是从 2 到 32; Descriptor Bypass for Read (H2C):适用于所有选定的读通道。每个二进制数字对应一个通道。LSB 对应于通道 0。值为 1 的位表示相应的通道启用了描述符旁路; Descriptor Bypass for Write (C2H):适用于所有选定的写通道。每个二进制数字对应一个通道。LSB 对应于通道 0。值为 1 的位表示相应的通道启用了描述符旁路; AXI ID Width:默认值为 4 位宽,也可以选择 2 位宽; DMA Status port:DMA 状态端口可用于所有通道。

DMA通道数用来区别不同的数据来源和类型,比如光纤数据,ADC数据等;

多通道时在AXIStream模式下影响很明显,在AXI Stream模式下选择多通道,可以连接不同的数据源。在AXI Memory Mapped模式下影响不大。

XDMA如何通过 PCIE 把数据放入电脑内存,简单来说, 我们先向操作系统申请一片电脑内存,得到这个内存的实地址 然后我们把这个实地址和内存大小配置到XDMA的寄存器中 然后写XDMA寄存器启动DMA XDMA就开始准备数据,按章PCIe的数据包格式打包【数据+目的内存的地址】 CPU收到包后,会将数据包的数据放到对应地址上,然后发送一个ack包给XDMA 然后XDMA开始准备下一个数据包,直到传输结束 发送一个IRQ告诉CPU DMA传输完成。 PCIe四种复位方式:冷、暖、热、功能层

浙公网安备 33010602011771号

浙公网安备 33010602011771号