6、AXI GPIO

AXI 互联接口作为 ZYNQ PS 和 PL 之间的桥梁, 能够使两者协同工作,进而形成一个完整的、 高度集成的系统。

MIO 和 EMIO 是直接挂在 PS 上的 GPIO。 而 AXI_GPIO 相当于 GPIO 的 IP 核,是通过 AXI 总线挂在 PS 上的GPIO 上。 本课节通过一个按钮控制 LED 亮暗讲解 AXI GPIO IP 的使用。

这里我们将在 PL 端调用 AXI GPIO IP 核, 并通过 AXI4-Lite 接口实现 PS 与 PL 中 AXI GPIO 模块的通信。

AXI GPIO IP 核为 AXI 接口提供了一个通用的输入/输出接口。 与 PS 端的 GPIO 不同, AXI GPIO 是一个软核( Soft IP),即 ZYNQ 芯片在出厂时并不存在这样的一个硬件电路, 而是由用户通过配置 PL 端的逻辑资源来实现的一个功能模块。 而 PS 端的 GPIO 是一个硬核( Hard IP) ,它是一个生产时在硅片中实现的功能电路。

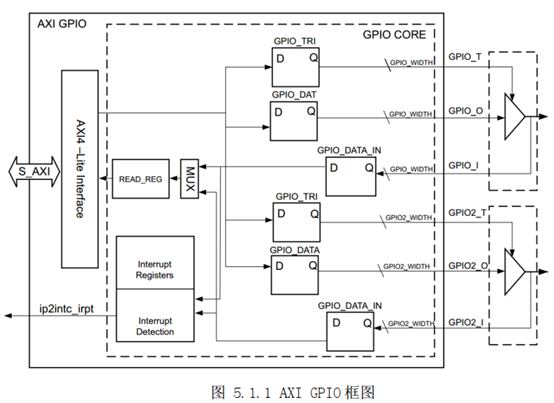

AXI GPIO 可以配置成单通道或者双通道, 每个通道的位宽可以单独设置。 另外通过打开或者关闭三态缓冲器, AXI GPIO 的端口还可以被动态地配置成输入或者输出接口。其顶层模块的框图如下所示:

从上图可以看到, 模块的左侧实现了一个 32 位的 AXI4-Lite 从机接口, 用于主机访问 AXI GPIO 内部各通道的寄存器。 当右侧接口输入的信号发生变化时,模块还能向主机产生中断信号。不过只有在配置IP 核时选择“ 使能中断” , 才会启用模块的中断控制功能。

这里的实验任务是通过调用 AXI GPIO IP 核,使用中断机制,实现领航者底板上 PL 端按键控制核心板上 PS 端 LED 的功能。

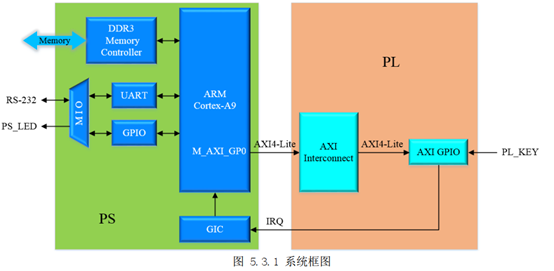

根据实验任务我们可以画出本次实验的系统框图,如下图所示:

在上图中, PS 端的 M_AXI_GP0 作为主端口, 与 PL 端的 AXI GPIO IP 核以 AXI4-Lite 总线相连接。

其中, AXI 互联 IP( AXI Interconnect) 用于连接 AXI 存储器映射( memory-mapped) 的主器件和从器件。通用中断控制器( GIC) 用于管理来自 PS 或者 PL 的中断, 并把这些中断发送到 CPU。

浙公网安备 33010602011771号

浙公网安备 33010602011771号