微机原理之 半导体存储器

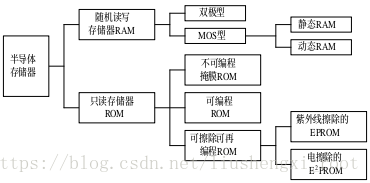

1. 半导体存储器的分类

从应用角度可将半导体存储器分为两大类:

RAM: RAM中的信息断电后即丢失

ROM: 断电后信息不会丢失,常用来存放不需要改变的信息(如某些系统程序)

1.1 RAM 的分类:

1. 双极型

2. MOS型

双极型:

存取速度快、集成度较低、功耗较大、成本较高等特点,适用于对速度要求较高的高速缓冲存储器

MOS型:

MOS型存储器具有集成度高、功耗低、价格便宜等特点,适用于内存储器

MOS型存储器按信息存放方式又可分为:

1.静态RAM(Static RAM,简称SRAM)

2.动态RAM(Dynamic RAM,简称DRAM)

1. 静态RAM:

SRAM存储电路以双稳态触发器为基础,状态稳定,只要不掉电,信息不会丢失。其优点是不需要刷新,控制电路简单,但集成度较低,适用于不需要大存储容量的计算机系统。

2. 动态RAM:

DRAM存储单元以电容为基础,电路简单,集成度高,但也存在问题,即电容中的电荷由于漏电会逐渐丢失,因此DRAM需要定时刷新,它适用于大存储容量的计算机系统。

1.2 分类总览:

1.3 半导体存储器的主要技术指标

1.存储容量

- 用字数 x 位数(即字长)表示,以位为单位。常用来表示存储芯片的容量,如1 K x 4位,表示该芯片有1 K个单元(1 K=1024),每个存储单元的长度为4位。

- 用字节数表示容量,以字节为单位,如128 B,表示该芯片有 128个单元,每个存储单元的长度为8位。

2.存取时间

3.存储周期

4.功耗

5.可靠性

6.集成度

7.性能/价格比

1.4 半导体存储器芯片的基本结构( 暂略 )

2. 随机读写存储器(RAM)

暂略

3.只读存储器(ROM)

暂略

4. 存储器的扩展(考点)

每一个存储器芯片的容量都是有限的 ,而且其字长有时候也不能正好满足计算机系统对字长的要求。因此,微机系统的存储器总是由多个存储器芯片共同构成的。

对存储芯片进行扩展与连接时要考虑两个方面的内容:

1.如何用容量较小的,字长较短的芯片组成满足系统容量要求的存储器

2.存储器如何与CPU连接

4.1 存储芯片的扩展

几个重要结论:(牢记)

1.存储器位宽表示每个地址下有多少位数据,与它的数据线根数相等;

2.存储器的地址线根数(N)决定了它的地址编号范围(2^N)

3.存储容量=2^地址线×数据线

4.字数=2^地址线

字长=数据线长度

重要!!! 存储容量 = 2^地址线×数据线

存储容量 = 字数 x 位数

字拓展(与CS有关) ,位拓展(与数据线有关) ,其余线路都并联即可!

存储芯片的扩展包括

1. 位扩展

2. 字扩展

3. 字位同时扩展

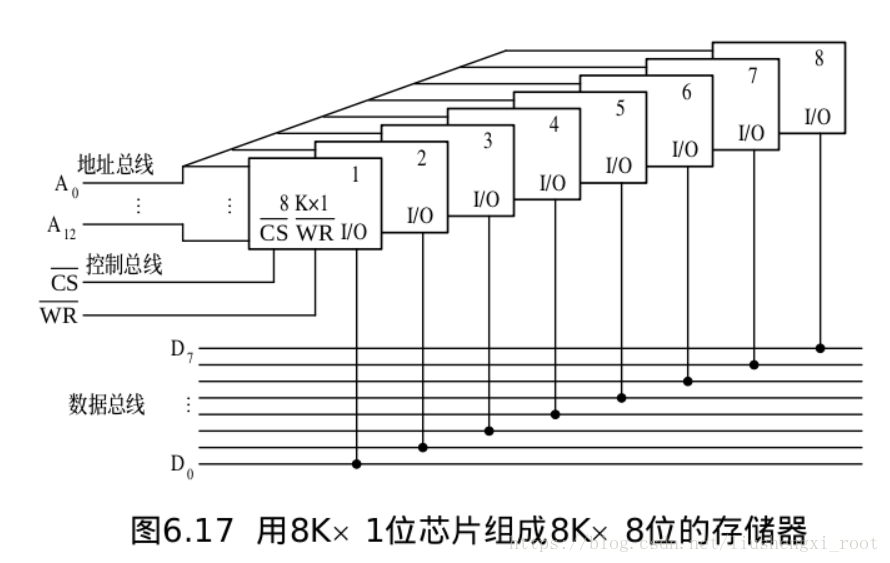

位扩展 :将各芯片的地址线、片选CS、读/写控制线相应并联,而数据线要分别引出。

位扩展是指存储芯片的字(单元)数满足要求而位数不够,需对每个存储单元的位数进行扩展。下图给出了使用8片8 K1的RAM芯片通过位扩展构成8K x 8的存储器系统的连线图。

说明 : 由于存储器的字数与存储器芯片的字数一致,8 K=2^13,故只需13根地址线(A12 x A0)对各芯片内的存储单元寻址,每一芯片只有一条数据线,所以需要8片这样的芯片,将它们的数据线分别接到数据总线(D7D0)的相应位。在此连接方法中,每一条地址线有8个负载,每一条数据线只有一个负载。位扩展法中,所有芯片都应同时被选中,各芯片CS端可直接接地,也可并联在一起,根据地址范围的要求,与高位地址线译码产生的片选信号相连。对于此例,若地址线A0A12上的信号为全0,即选中了存储器0号单元,则该单元的8位信息是由各芯片0号单元的1位信息共同构成的。

可以看出,位扩展的连接方式是将各芯片的地址线、片选CS、读/写控制线相应并联,而数据线要分别引出。

字扩展 :将各芯片的地址线、数据线、读/写控制线并联,而由片选信号来区分各片地址

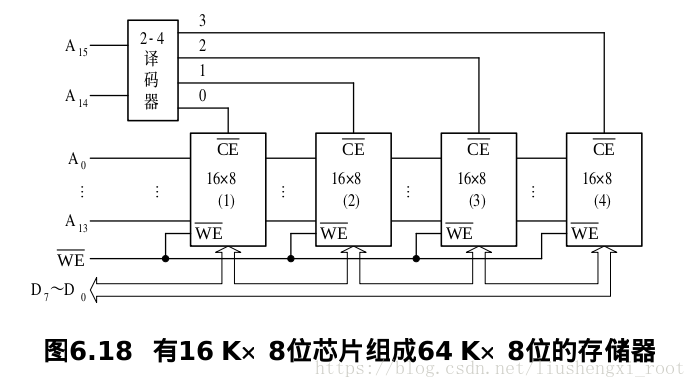

字扩展用于存储芯片的位数满足要求而字数不够的情况,是对存储单元数量的扩展。图6.18给出了用4个16 K8芯片经字扩展构成一个64K8存储器系统的连接方法。

说明: 图中4个芯片的数据端与数据总线D7D0相连;地址总线低位地址A13A0与各芯片的14位地址线连接,用于进行片内寻址;为了区分4个芯片的地址范围,还需要两根高位地址线A14、A15经2–4译码器译出4根片选信号线,分别和4个芯片的片选端相连。

可以看出,字扩展的连接方式是将各芯片的地址线、数据线、读/写控制线并联,而由片选信号来区分各片地址。也就是将低位地址线直接与各芯片地址线相连,以选择片内的某个单元;用高位地址线经译码器产生若干不同片选信号,连接到各芯片的片选端,以确定各芯片在整个存储空间中所属的地址范围。

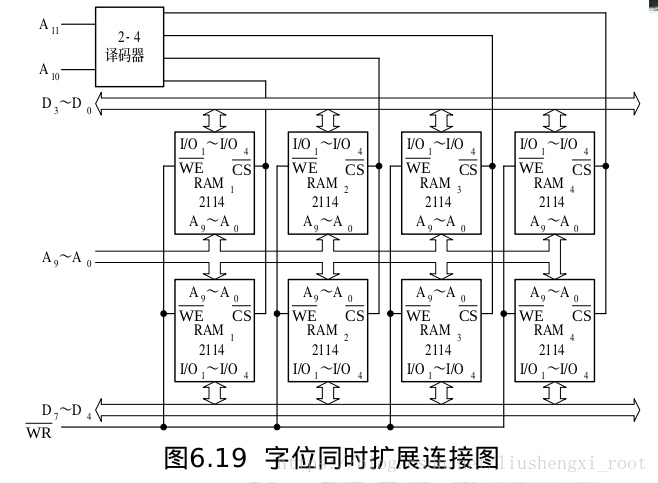

字位同时扩展:前面相除的为组的数量,后面相除的为组内的数量。组内采用位扩展法,组间采用字扩展法

字数和位数都需要扩展的情况

若使用 l x k 位存储器芯片构成一个容量为M x N位(M>l,N>k)的存储器,那么这个存储器共需要(M/l)x(N/k)个存储器芯片。连接时可将这些芯片分成(M/l)个组,每组有(N/k)个芯片,组内采用位扩展法,组间采用字扩展法。 图6.19给出了用2114(1K4)RAM芯片构成4K8存储器的连接方法。

说明:图中将8片2114芯片分成了4组(RAM1、RAM2、RAM3和RAM4),每组2片。组内用位扩展法构成1K8的存储模块,4个这样的存储模块用字扩展法连接便构成了4K8的存储器。用A9A0 10根地址线对每组芯片进行片内寻址,同组芯片应被同时选中,故同组芯片的片选端应并联在一起。本例用2–4译码器对两根高位地址线A10A11译码,产生4根片选信号线,分别与各组芯片的片选端相连。

4.2 存储器与CPU的连接

CPU对存储器进行访问时,首先要在地址总线上发地址信号,选择要访问的存储单元,还要向存储器发出读/写控制信号,最后在数据总线上进行信息交换。因此,存储器与CPU的连接实际上就是存储器与三总线中相关信号线的连接。

4.2.1 存储器与控制总线的连接

在控制总线中,与存储器相连的信号线为数不多,如8086/8088最小方式下的M/IO(8088为M/IO)、RD和WR,最大方式下的MRDC、MWTC、IORC和IOWC等,连接也非常简单,有时这些控制线(如M/IO)也与地址线一同参与地址译码,生成片选信号

4.2.2 存储器与数据总线的连接

8086 CPU的数据总线有16根 ,其中高8位数据线D15D8接存储器的高位库(奇地址库),低8位数据线D7D0接存储器的低位库(偶地址库),根据BHE(选择奇地址库)和A0(选择偶地址库)的不同状态组合决定对存储器做字操作还是字节操作。

4.2.3 存储器与地址总线的连接

对于由多个存储芯片构成的存储器,其地址线的译码被分成

1. 片内地址译码:用于对各芯片内某存储单元的选择

2. 片间地址译码 :用于产生片选信号,

以决定每一个存储芯片在整个存储单元中的地址范围,避免各芯片地址空间的重叠