EMC设计总结篇--PCB设计

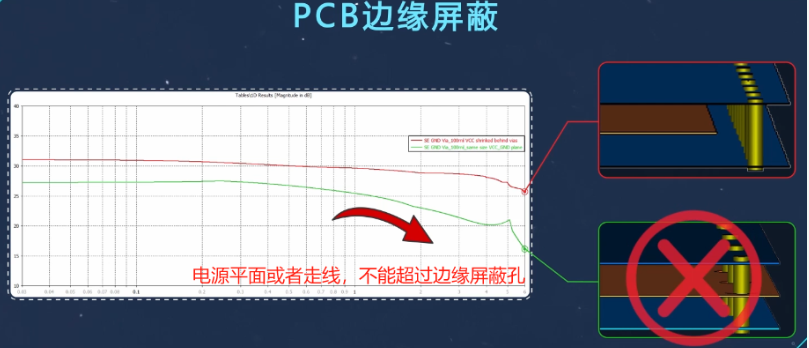

1、PCB边缘屏蔽及高速差分线EMI分析及设计规则

1.1、屏蔽孔:PCB周边一圈屏蔽孔间距不超过100mil;电源平面或者走线不得超过屏蔽孔。

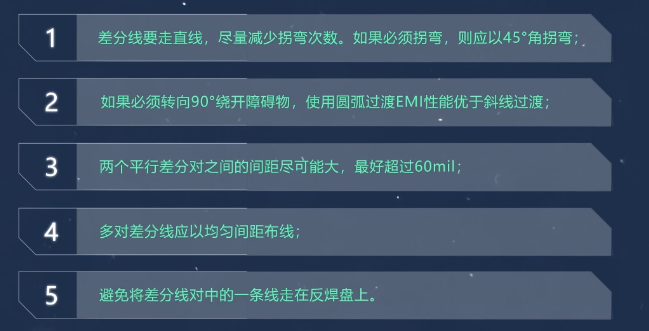

1.2、高速差分线EMI分析及设计规则

2、3W原则和20H原则的分析及应用

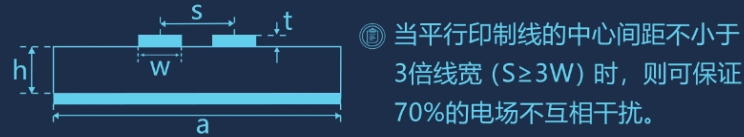

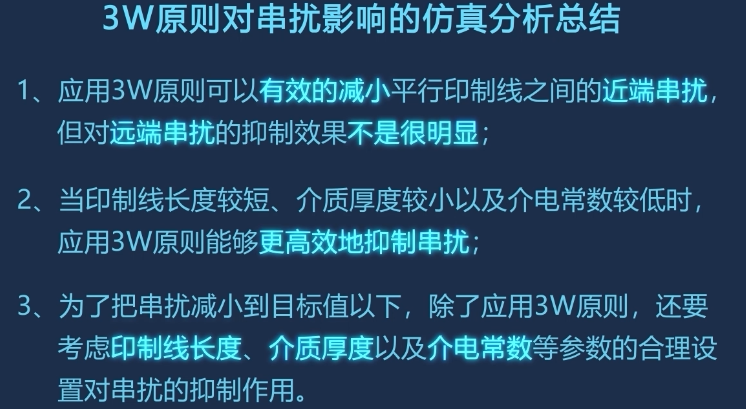

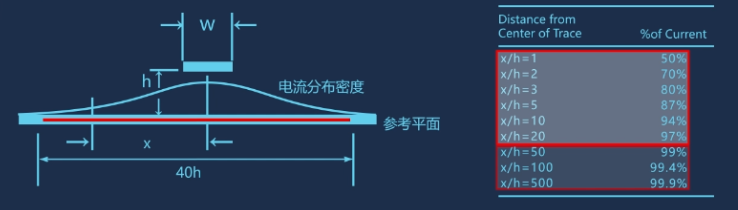

2.1、3W走线

2.2、不同印制线中心距对串扰的影响;

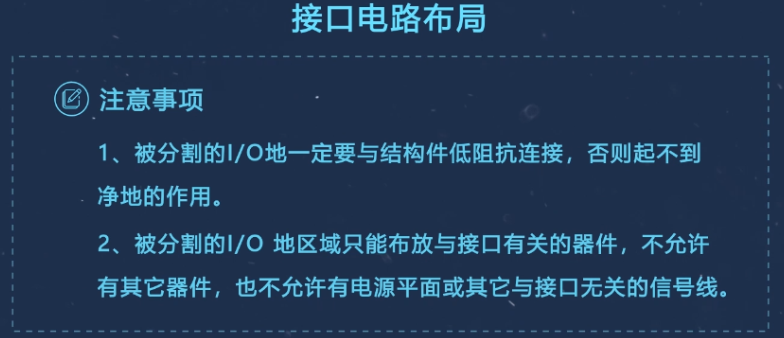

2.3、不同印制线长度对串扰的影响;

2.4、不同介质厚度对串扰的影响;

2.5、不同介电常数对串扰的影响;

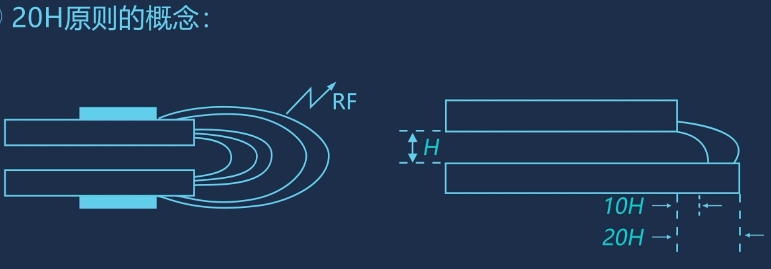

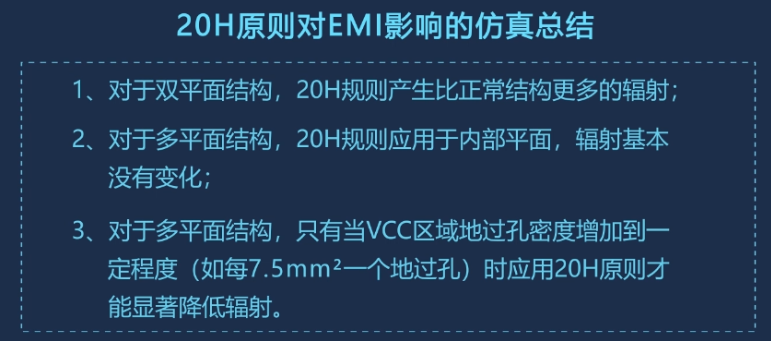

2.6、20H原则

3、关系信号PCB边缘走线和包地EMI分析及设计规则

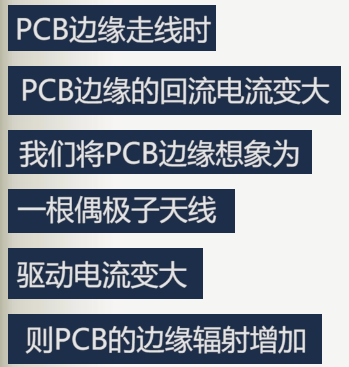

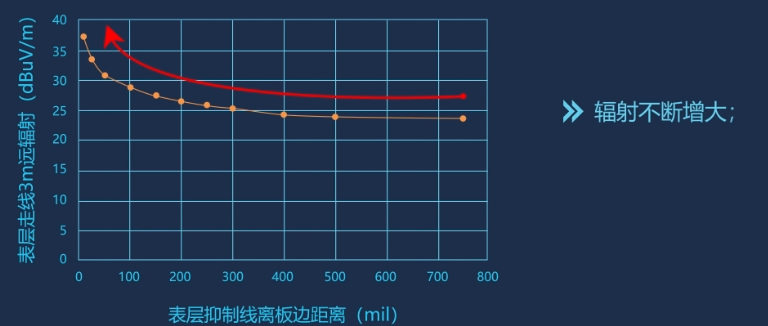

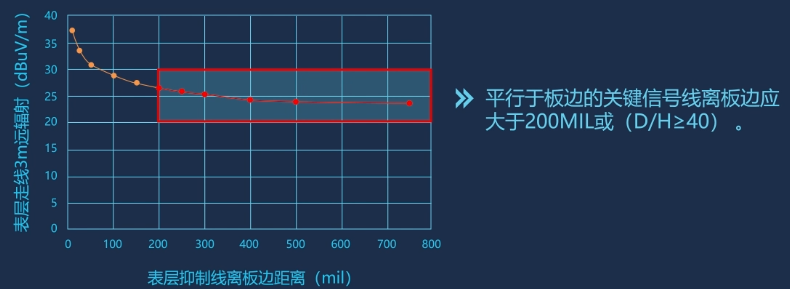

3.1、关系信号PCB边缘走线

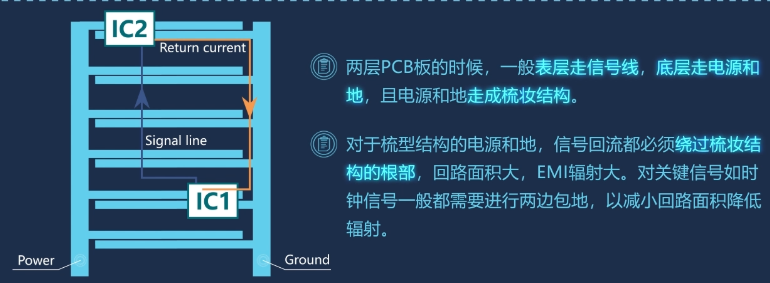

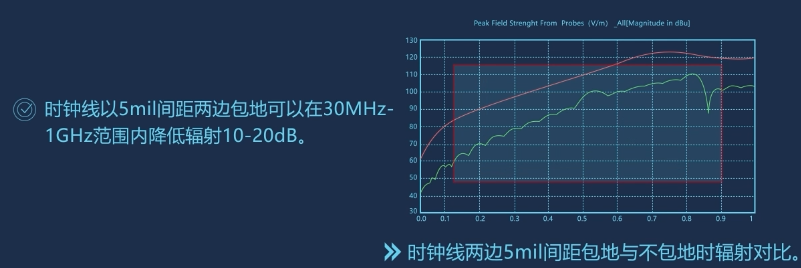

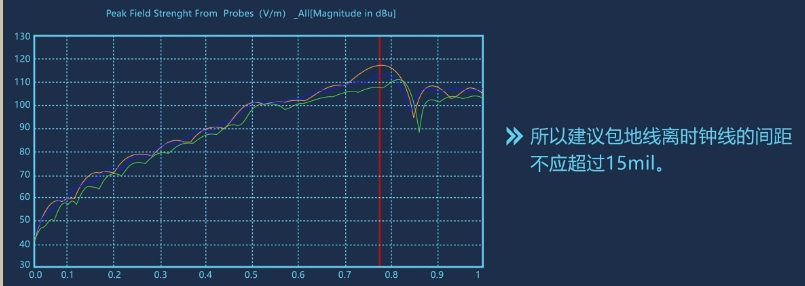

3.2、关键信号包地EMI分析及设计规则

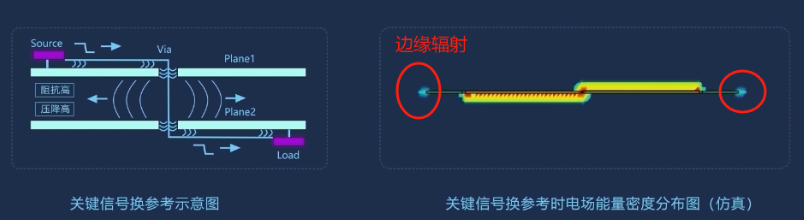

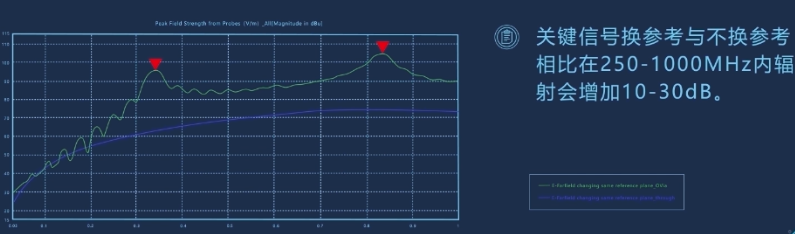

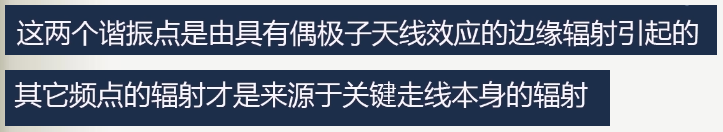

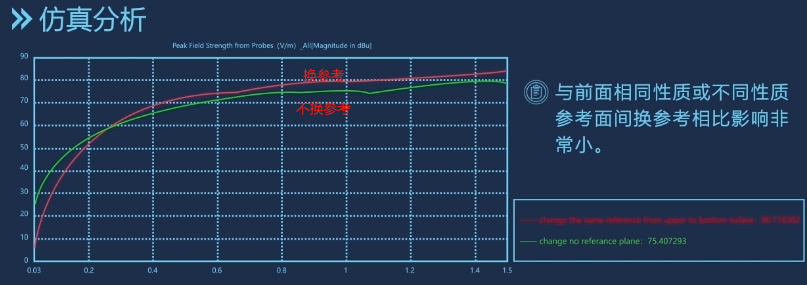

4、关键信号换参考EMI分析及设计规则

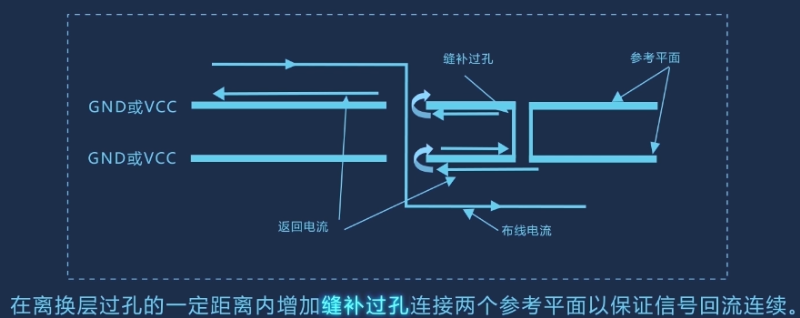

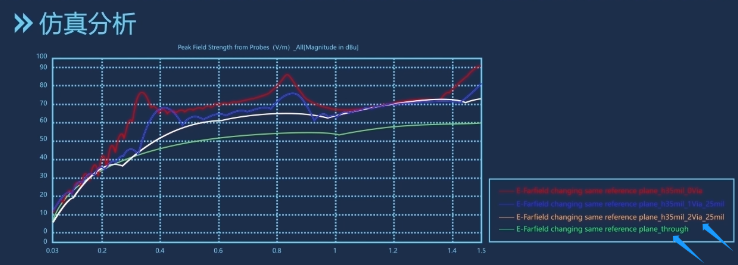

4.1、参考面都是相同性质,都是GND或者都是VCC增加缝补过孔。

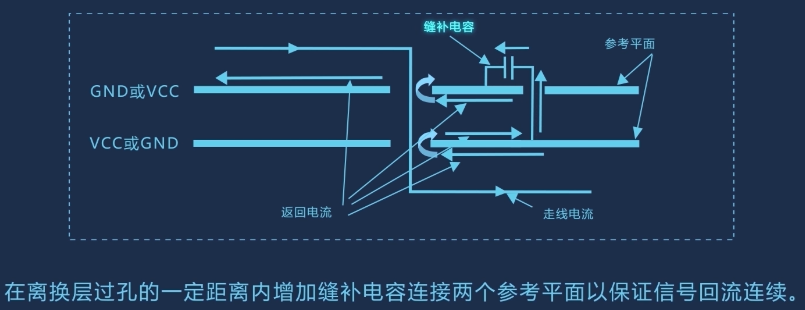

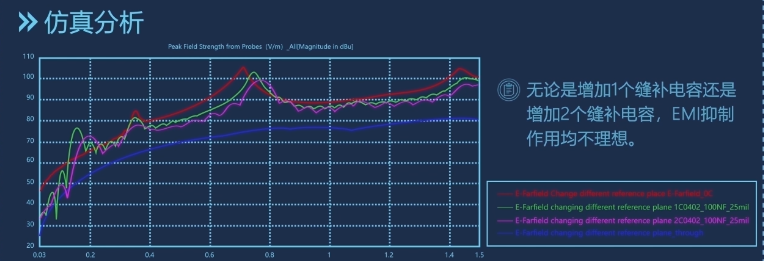

4.2、参考面都是不同性质,增加缝补电容

参考面都是不同性质,增加缝补电容

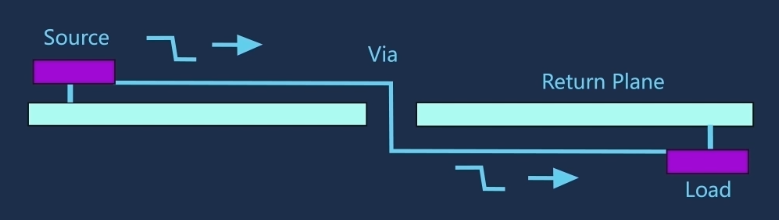

4.3、参考面不变的换参考

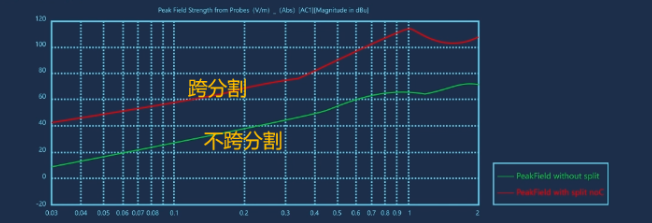

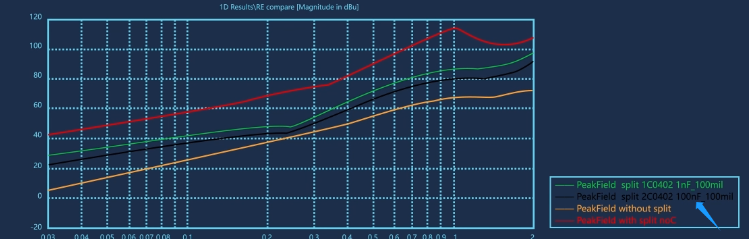

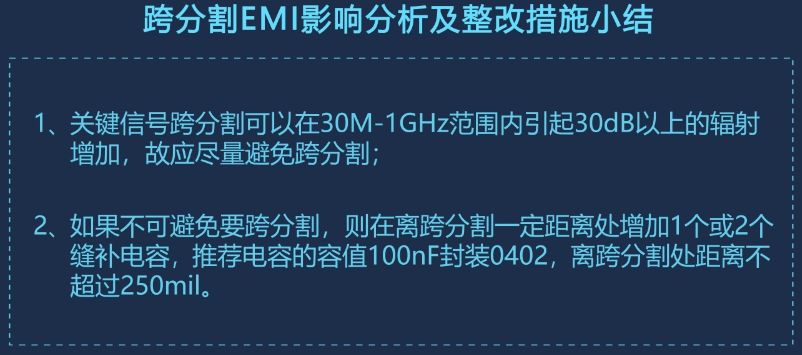

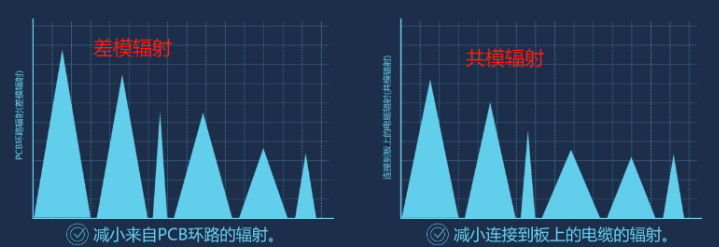

5、关键信号跨分割EMI分析及设计规则

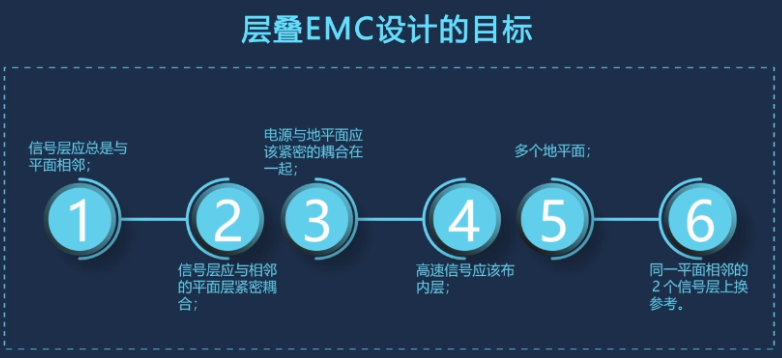

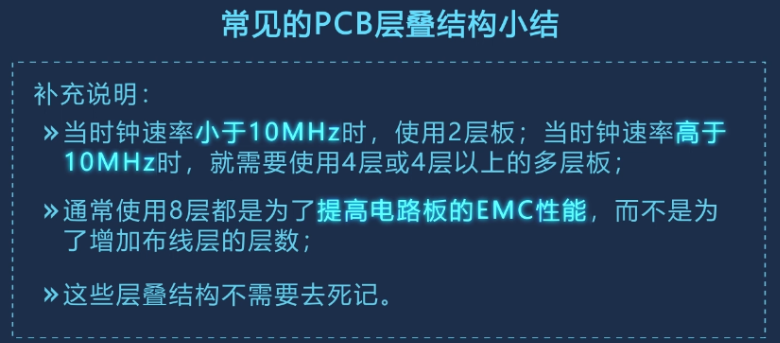

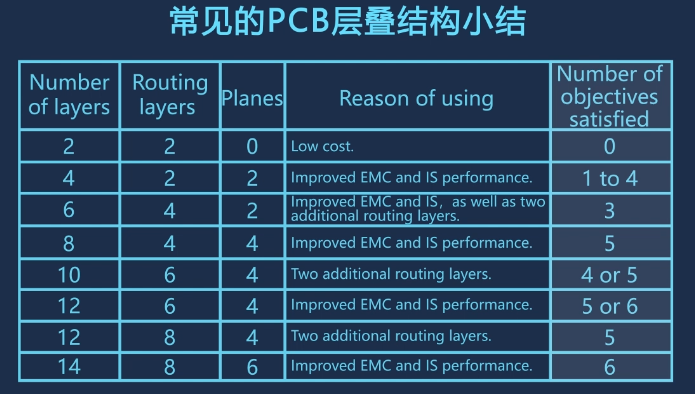

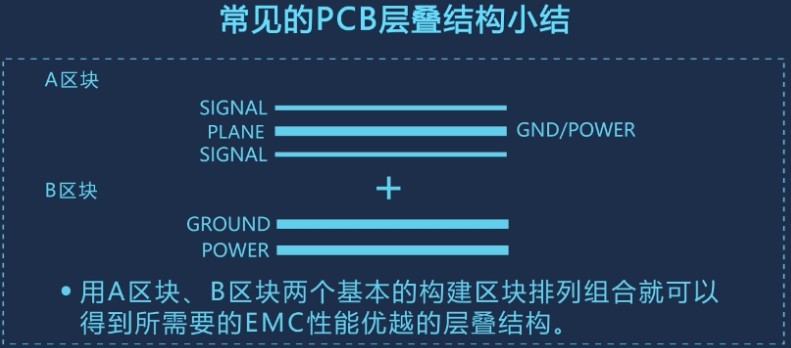

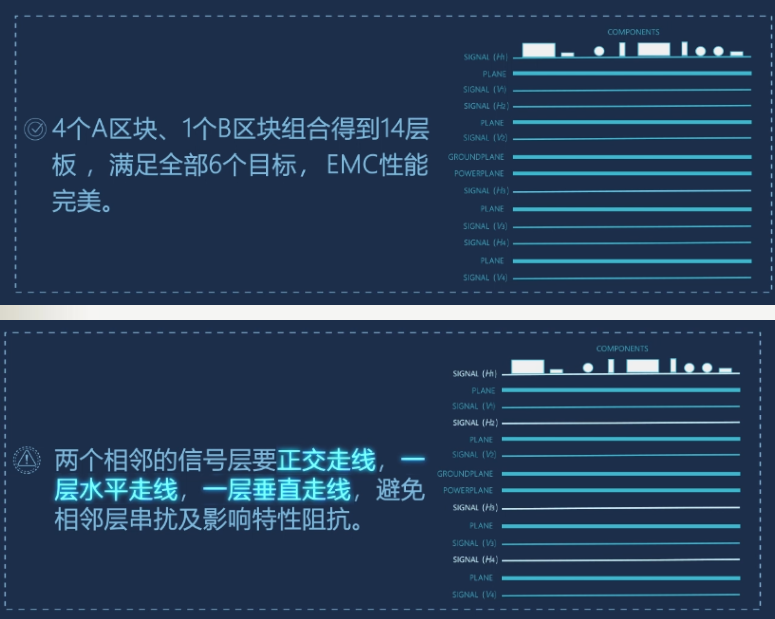

6、PCB层叠EMC设计

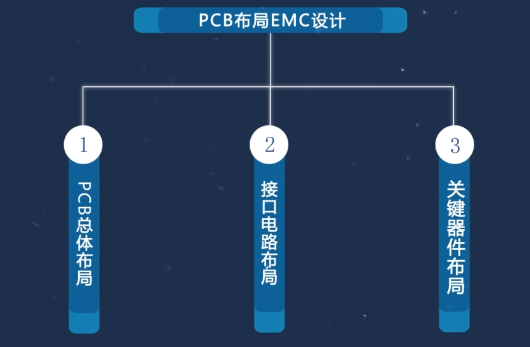

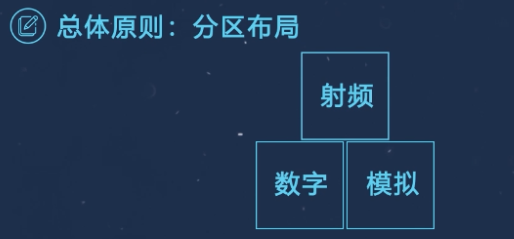

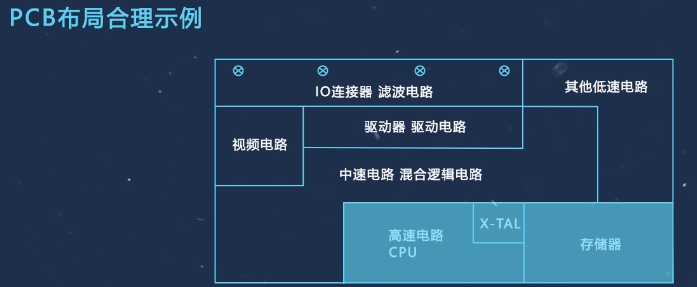

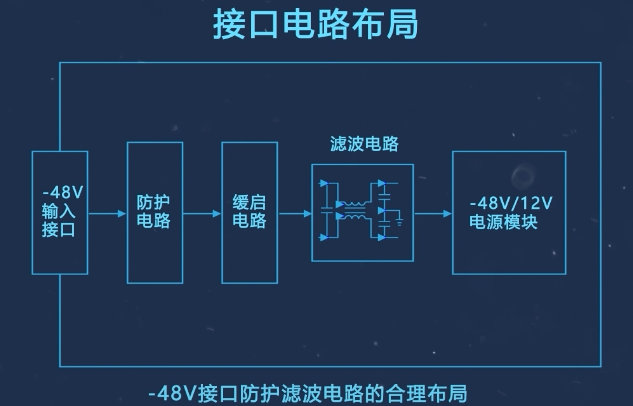

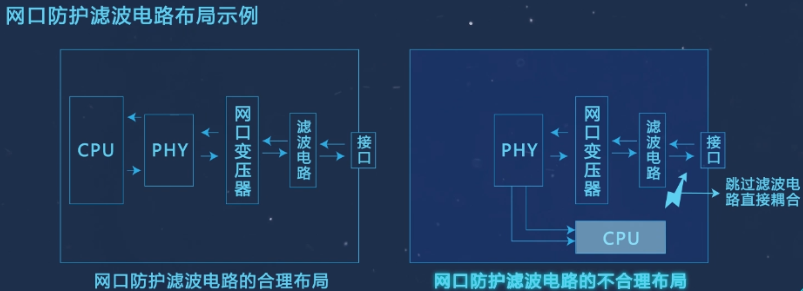

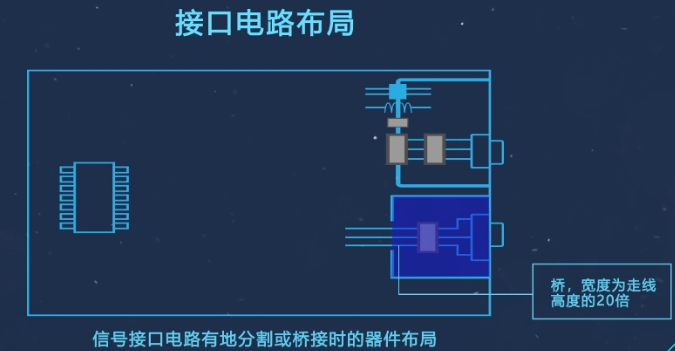

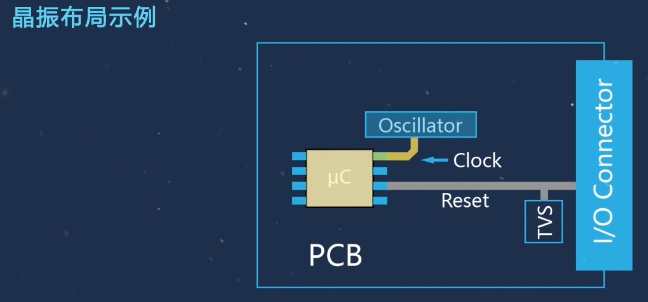

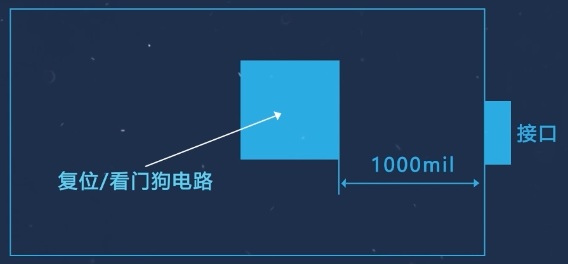

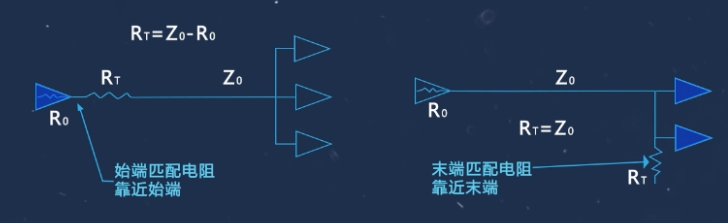

7、PCB布局EMC设计

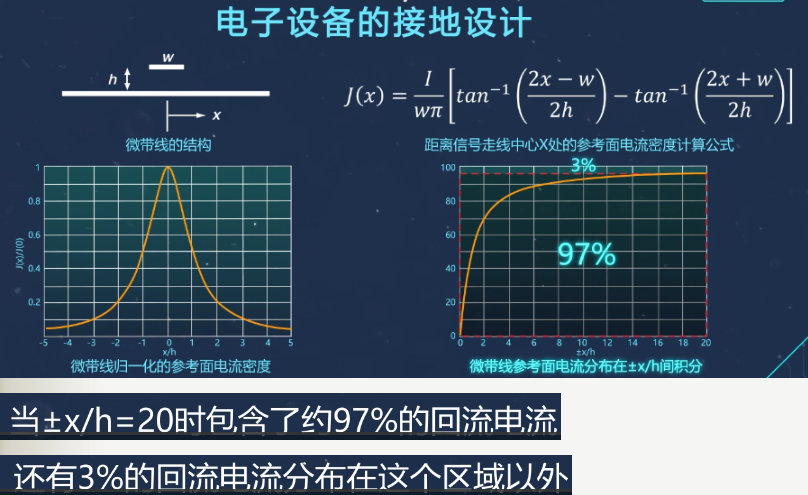

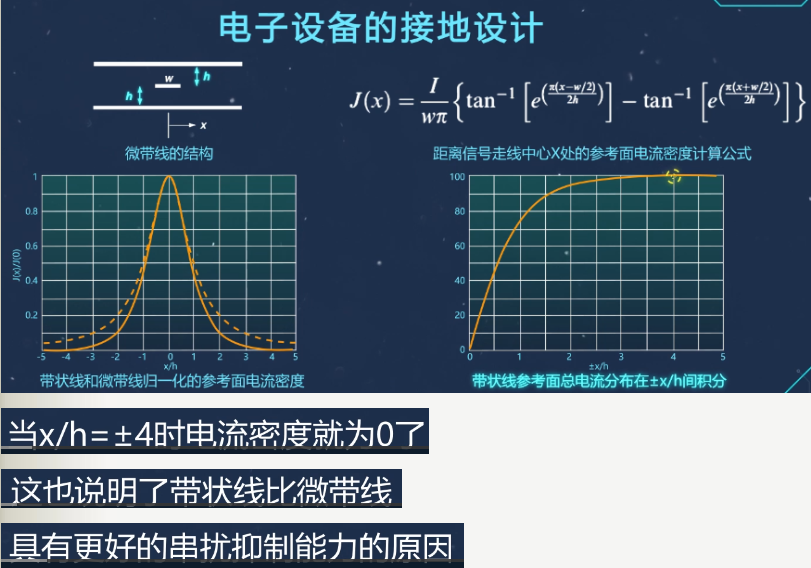

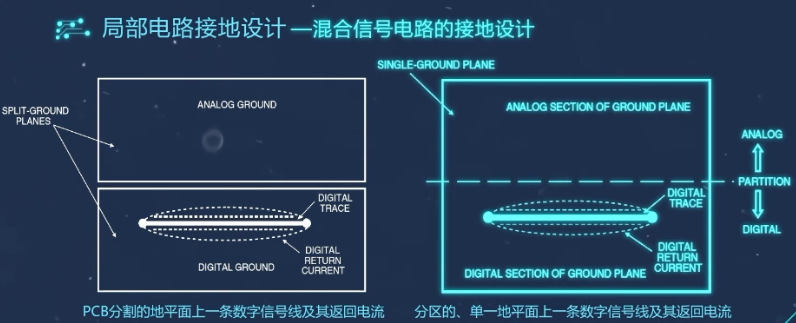

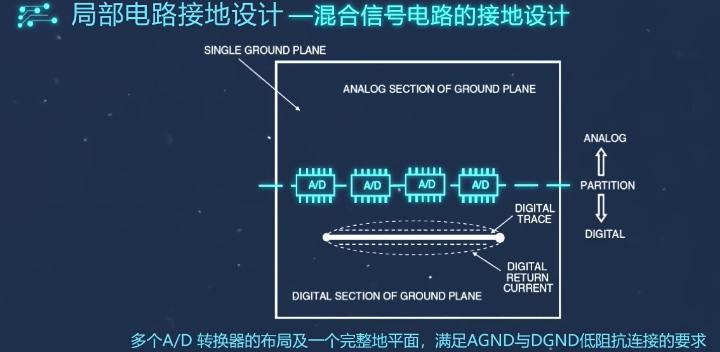

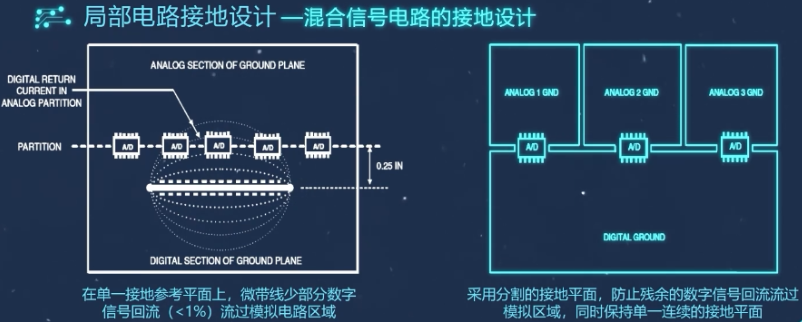

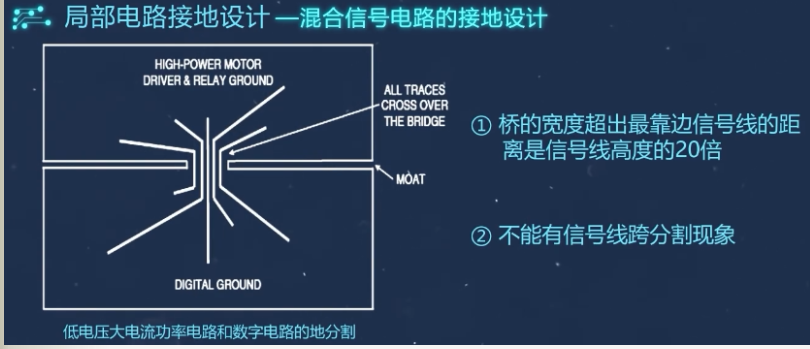

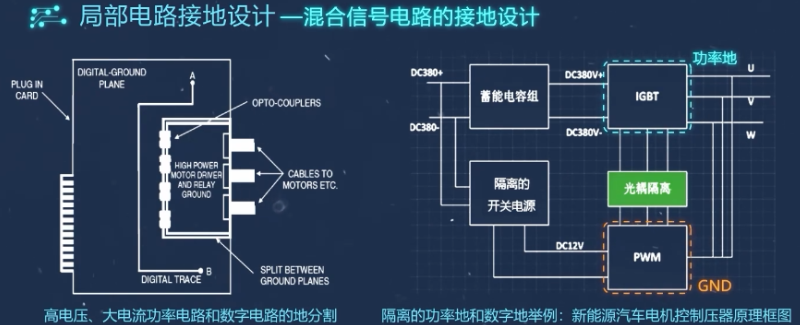

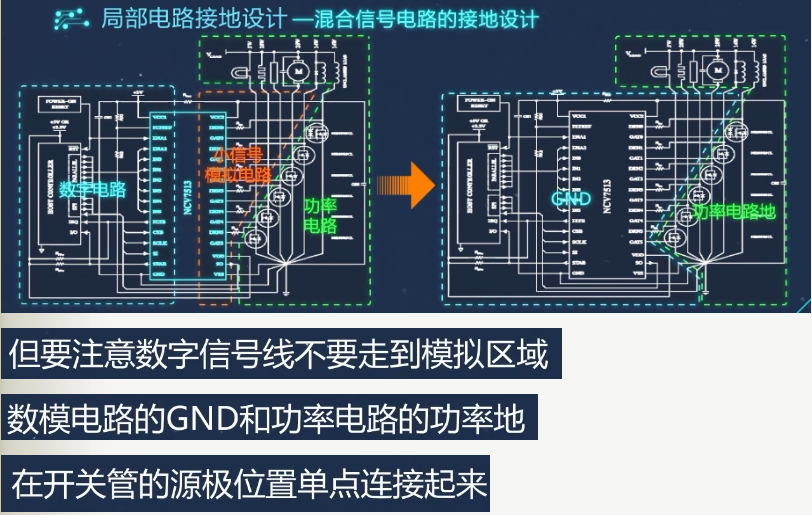

8、电子设备的接地设计

浙公网安备 33010602011771号

浙公网安备 33010602011771号