相对等长,动态等长,静态等长

好吧,又是等长,虽然实际的操作不复杂,但是似乎关于它的话题一直都不会少。

在allegro的Electrical规则里面,有关等长约束的规则,细细数来也有好几条。

为什么说Allegro是做高速板的神兵利器,就是因为不管你有什么样的设计要求,

它都能通过CM管理器设置合理的约束来达到既定的设计需求。这期我们就聊聊等长方面的约束,

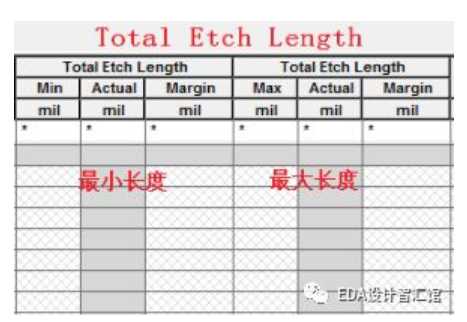

我们所有可能用到的有关走线长度的要求都可以通过下面几项来设置相应的规则,如下图。

1.Total Etch Length:总的走线长度,是用来约束一根线或者一组线总的最大最小长度。

假设:某种25G信号的损耗要求必须在3dB以内,我们选择的某种高速材料它对传输线损耗在0.7db/inch左右,

那总的走线长度不能超过4000mil,我们就可以给它设置一个最大长度为4000mil的约束规则。

2.Min/Max Propagation Delays:最大最小传播延时,其实跟Total Etch Length一个意思,因为延时也能通过长度来衡量,只不过这项多了一个pin delay。要考虑芯片内部传输延时的时候就必须使用这项约束来设置规则。

不考虑芯片内部传输延迟用谁都无所谓。

3.Relative Propagation Delay:相对传输延迟,

这项是我们平常用的最多的一项等长规则,首先这项约束针对的是一组线,

以某一根线为基准,其他走线长度和基准的差别必须在一个范围内。

有pin delay的话也必须要考虑进去。常用的相对等长规则的设置方法有三种。

4.Differential Pair:差分对,用来约束差分对内等长,

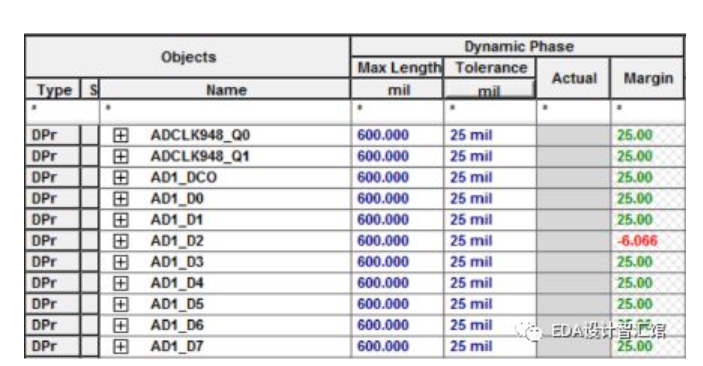

它有两个设置项:Static Phase(静态等长),Dynamic Phase(动态等长),如下图。

因为差分接收端所接收的信号是两根信号的差值,必须保证相位的高度同步,所以它们的对内等长要求一般都是通用的,差分对内等长要求总结如下:

1.差分对内整体控制等长<=5mil;

2.如果有换层,每一层的走线差分对内控制等长<=5mil(考虑不同层传输延时的差别);

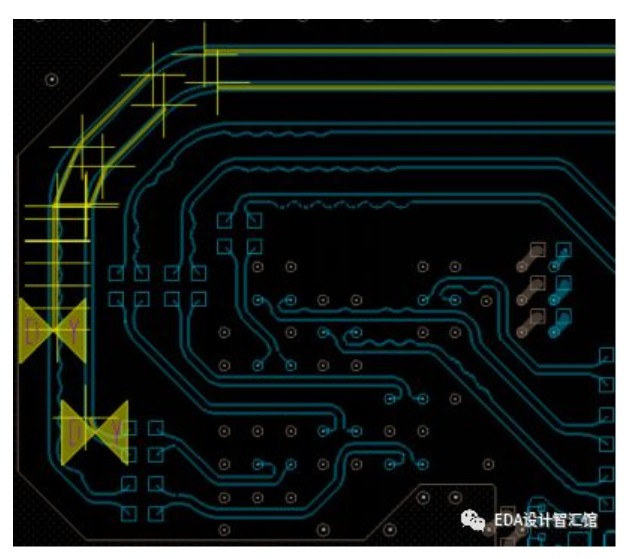

3.大于5G的高速串行总线,考虑实时等长,也就是当走线的偏差大于25mil的时候,必须在600mil以内进行补偿,可以反向拐角来补偿,也可以按照3W规则小波浪绕线补偿;

4.Break out区域,偏差可以放大到30mil,不等长的范围可以增加到800mil,如果换层,每层走线之间的不等长偏差也从<=5mil加大到<=10mil。

第1点、可以直接通过Static Phase来进行约束,实际上我们平常所处理的差分对内等长设的都是静态规则,只要保证整体等长即可,至于是绕大波浪还是小波浪,在哪儿绕波浪,这些都还是有讲究的,有些同学处理等长的时候虽然满足了静态规则的要求,但是提交上来的等长依然不合格,大多都是波浪没处理好的原因,由于篇幅关系我们后面再来介绍。

第2点、这项要求我们无法通过约束来设置相应的规则,但是可以设置一个静态规则的同时在处理等长时候需要有一个动态思维:因为动态等长就是我们所说的实时等长,它与静态等长所不同的是差分对的两个信号无论在哪个位置都是满足5mil的等长误差。我们在处理静态等长的时候就需要有这种思维:两根线的长度是在哪里引起的误差,就需要在哪里补偿回来,保证实时等长。

第3.4点、就是真正意义上的动态等长,当信号速率比较高的时候,我们就必须设置Dynamic Phase,通过这项约束来保证两根信号的实时等长。因为有很多同学没有做过,这里我们以第三点的等长要求为例来介绍Dynamic Phase的用法:

首先差分对内需整体控制等长<=5mil,所以必须要有个Static Phase,如下图。

当走线的偏差大于25mil的时候,必须在600mil以内进行补偿,其Dynamic Phase约束如下图。

如果最终的差分等长没有满足Dynamic Phase约束的时候,会报DY的错误出来,如下图。

以上就是我们在处理信号长度的时候所有可能会用到的约束规则,希望以上的讲解,对大家的设计有帮助,谢谢!

来自:https://www.eda365.com/article-63833-1.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号