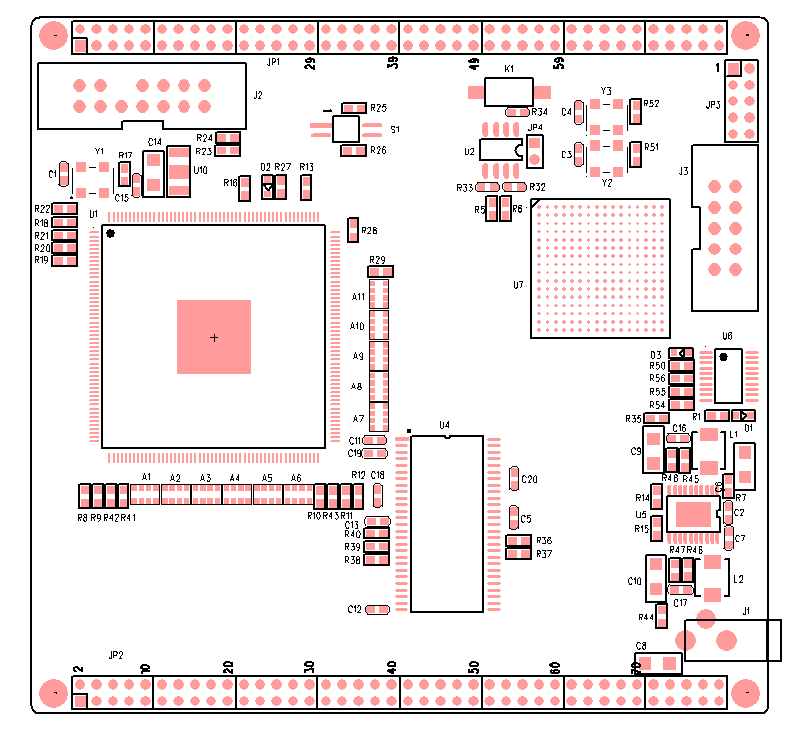

PADS LAYOUT 基础学习总结

1、Layout 前期准备

1.1、“选项”中配置“设计栅格”和“显示栅格”

1.2、“选项-全局-常规“中配置最小显示宽度

1.3、“显示颜色”里面配置可见性 去掉干扰布线的因素

1.4、布局-添加过孔-设置层叠-设计规则设置-布线(router)

2、Layout 常用参数

2.1、丝印中元件符号 50、5有比较好的显示效果

2.2、MCU 和外部电阻电容间 50mil(两者焊盘间距)比较好

2.3、元件编辑器中,元件丝印线的宽度 4mil 或 5mil 比价美观

2.4、钻孔到其他所有最小要8mil 小于8mil 板厂可能要加钱。

通常一款板子过孔设计不多于2种。常用过孔8/16mil,10/20mil和12/24mil等。

2.5、过孔载流:VIA8/16--0.5A,VIA10/20--0.8A,VIA12/24--1.2A。

2.6、板边到其他所有有12mil (0.3mm)一般设置为20mil。

2.7、电源走线40mil能过1A电流 ,一般设置大于这个数。

2.8、最小线宽4mil(0.1mm),线距要0.1mm(4mil)。

2.9、铺铜间距最好不小于0.2(0.15)mm,一般设置为10mil

PCB Layout 时,我常好奇为什么他们 Layout 大系统板子的就可以用 4mil 走线,而我做 MCU 板子的就只能用 6mil 的走线。现在我才知道其实 4mil 6mil 的走线就载流能力来看都是够的,只不过是对于洗板工艺有要求,6mil 的走线一般的洗板厂都可以做到,但是 4mil 走线对于洗板工艺就有些要求了。

大系统的板子上的元件会有 BGA 的封装,比较精密,本来就对洗板要求高,所以用 4mil 的走线;而 MCU 板子没那么精密,用 6mil 就可以满足要求,用 4mil 走线洗板的时候价格还会比 6mil 贵些,就有点浪费资源了

2.10、对于芯片和连接座等位置不变的器件,可以选择Glued(胶粘)

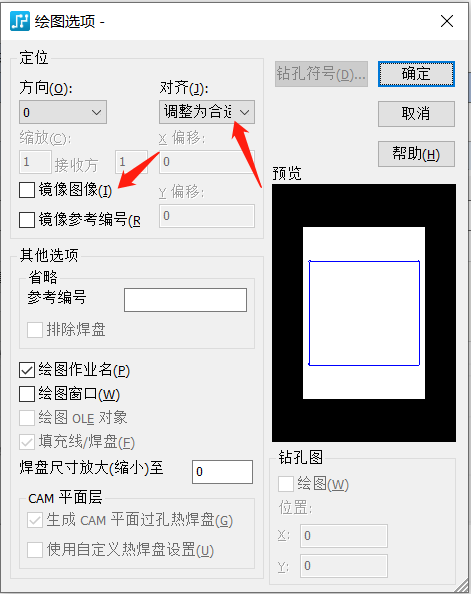

3、导 Gerber

3.1、无模快捷键@camdocs VX版本有快捷键CAM里的自动定义。会自动生成CAM文件。

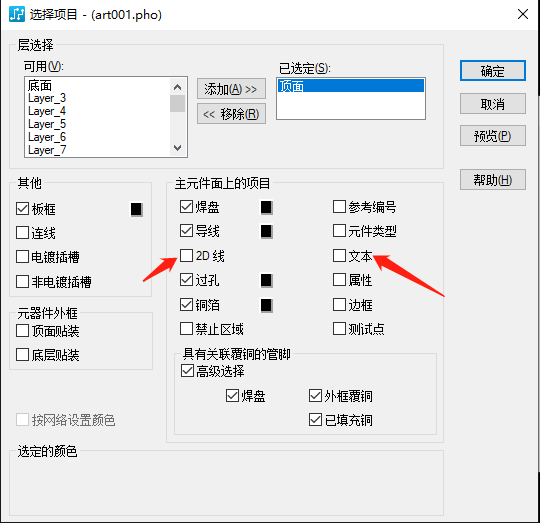

走线层(顶层 底层 中间层)2D线和文本不选(因为在走线层的2D线和文本 做出来都是铜皮。文本检查DRC还会报错,2D线还不会报错),这一层做出来的都是铜皮。

阻焊层(SM 绿油层)一般可以不修改。(高密度板阻焊层(绿油层)焊盘尺寸放大缩小要做修改,默认的是10mil,可修改为最小走

线宽度。不然导线离焊盘进,会露铜。特别是BGA 一定要注意)

助焊层(PM 钢网层)可以不修改。

开窗要在阻焊层和助焊层都画且要画重叠,一般是复制重叠。其中助焊层开钢网上锡,阻焊层这片区域不上绿油。

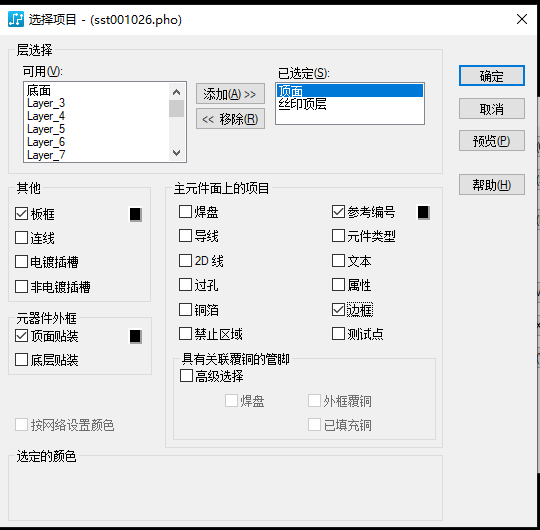

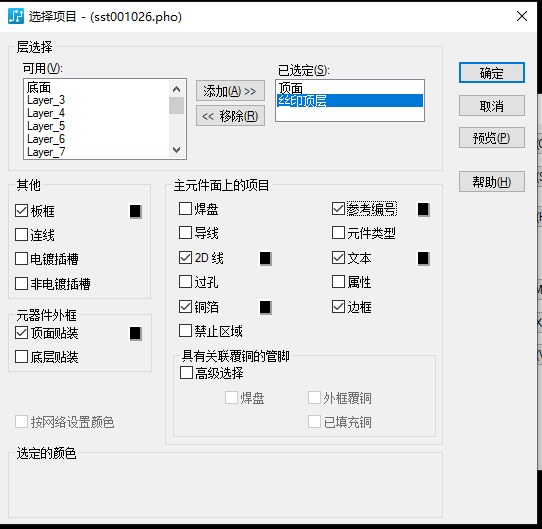

丝印层 (丝印层里的铜箔 出来是一片字符颜色,参考编号就是元器件位号 边框(元件边框)也选中一下)

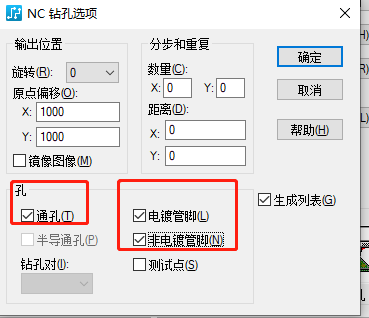

数控转钻孔层 (非电镀管脚选中一下)通孔默认就可以了

pt是电镀层 np是不电镀的转孔层

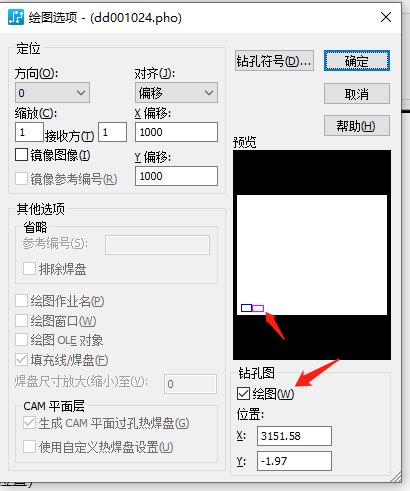

钻孔图(VX版本默认就可以了 老版本改一下位置)

3.2、通孔焊盘在 Solder Mask(阻焊层)中显示,不在 Paste Mask(助焊层)中显示。

3.3、板子开窗可以通过“在 Solder Mask(阻焊层)增加一无网络的铜箔”实现。

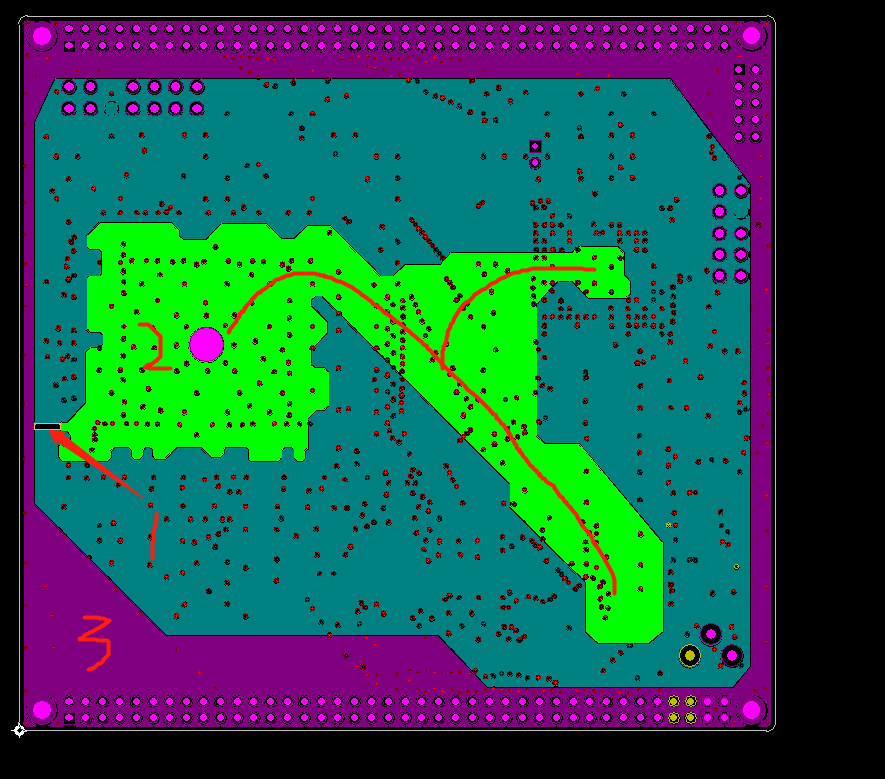

4、定义平面分隔(Split Planes)、覆铜/灌铜(Copper Pour)、贴铜/铜箔(Copper) 概念

一般来说贴铜或者铜箔指的是 Copper,灌铜指的是 Copper Pour,但说到覆铜可能指的是 Copper Pour 也可能是统指 Copper、Copper Pour、Plane 三种大面积的覆铜方式。

定义平面分隔(Split Planes)

一般用在电源层或地层的分割中,当设计中有多个地或者多个电源网络的时候,可以用定义平面分割来对平面进行网络分配。

覆铜/灌铜(Copper Pour)

覆铜范围为自行绘制的覆铜边框,并且要为覆铜边框选择网络,覆铜时它将以完全间距的距离避开不同网络的焊盘、过孔等目标,而对于同一网络的目标,采用花孔或者 Flood over 进行连接。

贴铜/铜箔(Copper)

画完 Copper 的外形框之后,对其内部全部铺铜,是实心铜,它不会避让任何的网络和元件等目标。

5、定义平面分隔(Split Planes)操作步骤

其实很简单,跟覆铜操作相比,只需多做一步即可,即“修改层定义为分割/混合平面“,最多两步,“先为不同的网络分配不同的颜色”可以更方便的绘制分割平面。后续的“绘制分割平面”跟“填充平面层两步”跟覆铜操作大同小异。

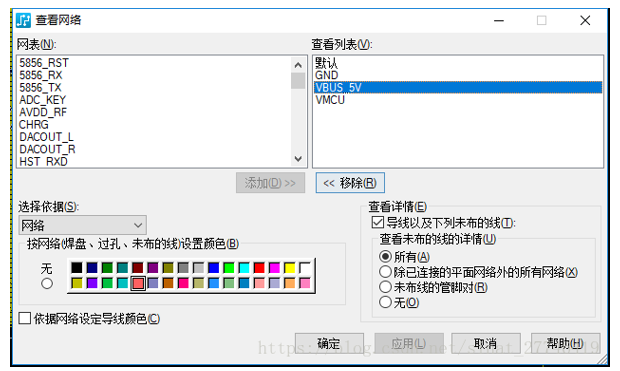

5.1、先为不同的网络分配不同的颜色

5.2、修改层定义为分割/混合平面,并分配网络

5.3、绘制分割平面

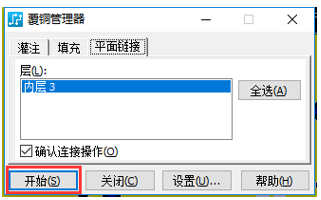

5.4、填充(Flood)平面层

6、PADS Layout 的层类型( Plane Type)

PADS Layout 中层类型有三种:

无平面(No Plane)

CAM 平面(CAM Plane)

混合/分割平面(Split/Mixed)

无平面(No Plane)

一般使用的是平面类型是无平面(No Plane)类型,以正片的形式输出

CAM 平面(CAM Plane)

CAM 平面以负片的形式输出,现在一般不用。

层分割以 2D 线来实现,不用铺铜,通常用于电源层和地层,且占用的数据量要小得多,但有一个缺点就是不会检查设计规则,即分配到这层的网络,就不会再检查安全间距及连接性,因此,分割层需要自己保证无误。

混合/分割平面(Split/Mixed)

以正片的形式输出

PS:一般建议各层都使用无平面即可,因为电源层及地层要用混合/分割平面实现的设计在无平面类型中使用覆铜功能也可以实现,只是相对于混合/分割平面文件可能会大一些。

7、Layout 修改层定义

Layout 中,原始层定义是 4 层板,但实际上两层板就可以搞定,只用了 1、4 层。于是想把层定义从 4 层修改到 2 层,但是如果修改不了怎么办?

没关系,层定义仍用 4 层板,导 Gerber 的时候只导出顶层和底层,洗板备注为两层即可。

来自:https://blog.csdn.net/sinat_27746419/article/details/81063064

8、Layout 的封装编辑器里

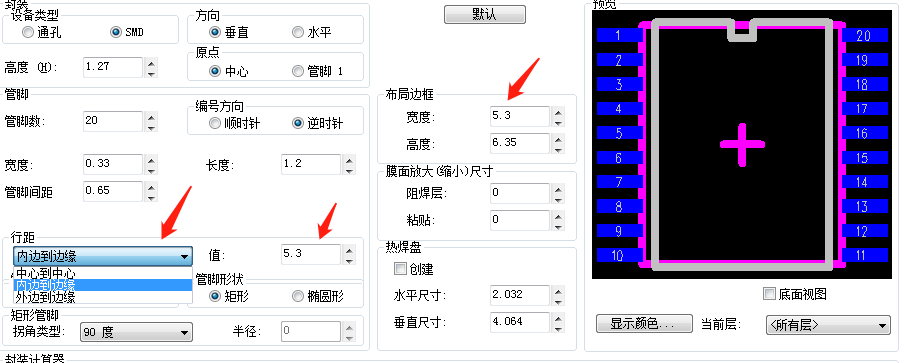

行距:

中心到中心是指,焊盘的中心到中心

内边到边缘是指,焊盘的内边沿到另一排焊盘的内边沿

外边到边沿是指,焊盘的外边沿到另一排焊盘的外边沿

调整布局边框参数看出上述变化

管脚宽度一般是管脚间距的一半 外露0.8mm

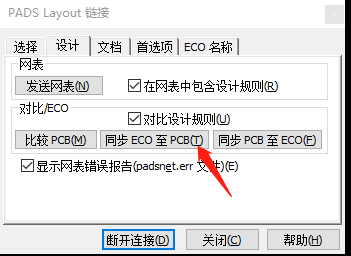

9、PCB改版后,logic中要选同步ECO至PCB ,才会更新。

10、ROUTER里不要给元器件设置特性

11、ROUTER里设置差分走线(一般网络名带+ - p n为差分线,例如USB的D+ D-)

右键选择差分网络,右键设置为差分走线,在项目浏览器下的网路对象下的差分对设置差分特性。

走线到连接引脚处 shift + Z 转换为单线接引脚。差分线打孔要对称(shift+单击鼠标左键)

12、ROUTER里布线时,快速切换到相应层布线的一种方法

选中该层的元件或走线 按下F3就切换到相应层,在ESC取消布线。

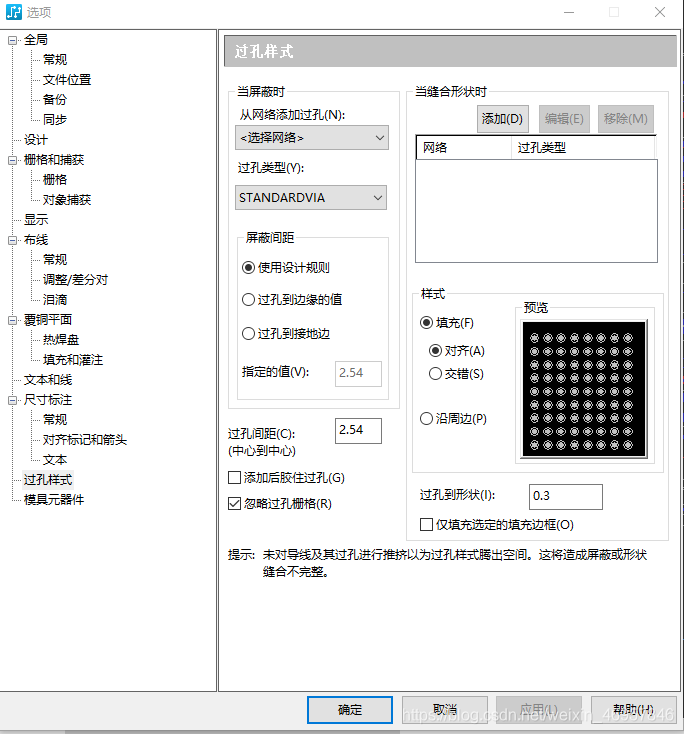

13、缝合孔是没有连线的孔。批量添加的过孔就是缝合孔。

14、批量添加地孔的方法

敷完铜后选铜皮边,右键选择敷铜内过孔阵列。

1、在选项>设计里的在线DRC下的防止错误,不然自动打孔会打在导线上。

2、工具 > 选项 >过孔样式

a.过孔网络同样选择GND;

b.过孔类型选择已创建的过孔类型;

b.在<当缝合形状时>中,选择添加,将以上a、b两布再添加一遍;

d.屏蔽间距一般默认选择<使用设计规则>,过孔间距及样式设置好即可。

3.工具 > 覆铜平面管理器 > 灌铜;

4.空白区域鼠标右击 > 选择形状 > 选中GND平面(在铜皮边缘选中) > 鼠标右击 > 覆铜区域内过孔阵列。

另外PADS手动批量添加过孔方式:

1.右击 > 选择网络> GND > 按”V“更改默认过孔样式

2.右击 > 添加过孔。

15、批量删除过孔

右键下的筛选条件下只选择缝合孔,然后回到PCB框选,选中的过孔删除就可以了

16、统一修改标签

右键下的筛选条件下只选择标签。然后回到PCB框选所有标签,

右键属性里的特性进行统一修改。一般尺寸和线宽50 5 或 60 6

17、圆弧倒角

圆弧倒角要在 选项-> 设计-> 倒角里的角度改为180 才可以

18、敷铜设置

18.1、敷铜栅格一般设置为1mil,敷铜线宽 ≥ 最小走线线宽。(如果敷铜线宽小于走线线宽,那么铜皮可能会出现小于线宽的铜皮,板厂制作会增加成本)

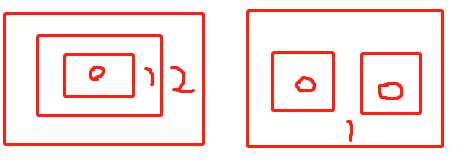

18.2、敷铜优选级设置,0级最高,敷铜里面的优先级最高。例如

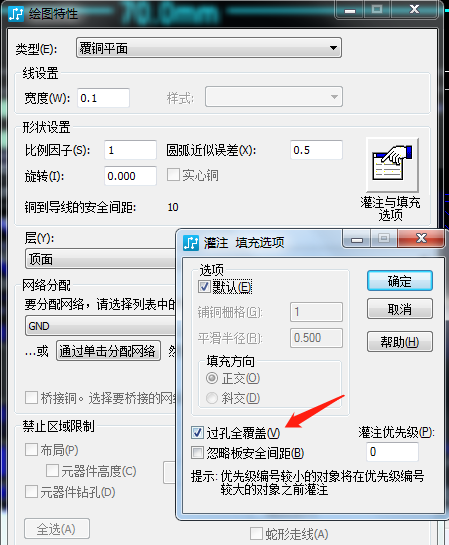

18.3、要使用过孔覆盖时,要再画第一个敷铜框时就把过孔覆盖选上,不然的话,之后的每一层都要设置一遍。

18.4、对于一层完整地的板子,敷铜时要观察地的上下连通性和左右连通性,适当的优化板子布线改善地的连通性。

18.5、画敷铜板框时出现字交叉,先修改线宽,把敷铜板框先闭合,闭合后在修改线宽。(一般选用 5mil 栅格设计)

18.6、电源分割

1、电源不能形成环路,不然会有环形电流干扰,有EMC问题

2、电源要走电源数,减少相互干扰

3、外围的地要多大过孔和内层地相连,不然的画也要阻断。避免形成环路

19、热焊盘

厚的板子一般使用热焊盘

20、出现T字型走线时,走线在交叉处画一个三角铜皮

21、虚拟过孔和过孔的区别,只是虚拟过孔可以做管脚对

22、电气网络是在做等长线时元器件两端当做同一个网络

23、最小间隙要大于2,不然干扰大。倒角比率,大概三边等长,看上去像个圆形。绕的弧形线长一般不要超过100mil,会发生天线效应,造成干扰。

24、热焊盘敷铜报错,原因:热焊盘接地有四个引脚,但引脚小于两个的时候就会报错。一般是地PADS的地一般不要拉线,不然敷铜敷不上。或者在 选项->热焊盘->选择给已布线元器件焊盘添加热焊盘打上勾。

25、地会找一个阻值小的线路回流,所以要检查板子上下左右地的环路,然后调整线路,使环路最小,因为地的环路过大会造成某些信号倍频,在地的回路,如果是铜皮,关键位置要多打过孔。所以一般一层不走线,或走短线,来保证地的完整性。

26、电源一般按照,电源树走线。

27、在router里才可以所有走线的线宽。网络->全选->

28、在router里的推挤功能,对于已经布好的线,选择最左边的一条保护,然后设置好线以线之间的宽度,对于要打孔的线要把距离预留够,一般比保护距离多2mil要好一些。(如果间距不够打不了过孔,又推挤过,只能一条一条拉)

29、布局

29.1、要先根据线宽和间距、是否打孔预估好要的布线所占空间,防止后面拉线堵死。

29.2、先把位置固定的元器件放好

29.3、元件与IC的距离 密度 手机 0.5mm PC 0.8-1mm 其他的要大于1mm 到 1.5mm

29.4、选择元器件分散,ctrl+E 抓取过来

30、布线

30.0、画板前先算阻抗

30.1、多层板 走线前 芯片的电源地要先打孔,不然走完线打孔很难,还要修改走线。

30.2、布线先难后易,先拉出线断不连接不打过孔,预估是否能拉完。(不能在调整布局,在预估拉线)不确定的线可以先拉出来占位置。

30.3、PADS打孔不能双击打孔,不然它会自动完成后面的布线。

30.4、IC的引脚间,不要走线。

30.5、布线时避免 U 型走线。

30.6、时钟信号尽量不要打孔。

30.7、晶振走线粗一点,一般10mil,晶振周边要包地。

30.8、考虑最佳的走线方式

30.9、管脚位错位的拉线方法(像倒车)

30.10、 IC或BGA 3个地可以共用2个过孔,2个地一般不要共用一个过孔。

30.11、分配颜色在 layout里

30.12、BGA不要打盘中孔(除非高密度的板 比如手机板),一些元器件焊盘大的可以打,不然会过孔漏锡,导致接触不良。

30.13、IC电容少 要兼顾多个引脚(一般IC一个VCC配一个电容),但为了省成本会少电容。所以在电容布局时要考虑,一个电容兼顾多个引脚。大电容的GND焊盘要打两个过孔。这种电容GND要就近打孔,减少回流路径,减少干扰。

30.14、电源VCC敷铜不要太靠近板边,不然电源辐射大,板边要预留一些敷铜,起屏蔽作用。

30.15、多个电源做分割时,重要的电源先分割。(比如 内核电源1.2V)最小区域距离要在60mil以上。如果内包 包了其他电源,那么这个电源孔要在其它层走线到该电源。

30.16、电阻电容中间0603以下,引脚间尽量不要穿线。

30.17、敷铜过不去可以拉线。

30.18、只有线距大于线宽,(线距大于线宽耦合大,干扰大)

30.19、U型走线 有辐射 (走线尽量不要出现U型)

30.20、走线不要走回头线

30.21、TP 测试点 TP 60 直径为60mil的测试点

31、装配文件

31.1、私印层装配文件设置

底层制作方式一样,只是要注意镜像。颜色只能点击打印之后,再回到层设置里修改。

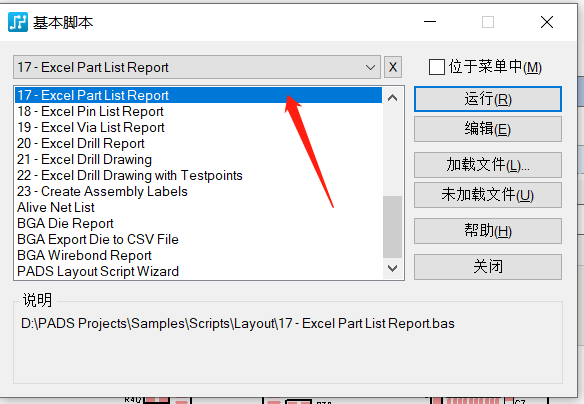

31.2、坐标文件输出

在工具的基本脚本里设置运行生成。注意单位,有些厂家要mm制(把PCB板改为mm制就可以)。

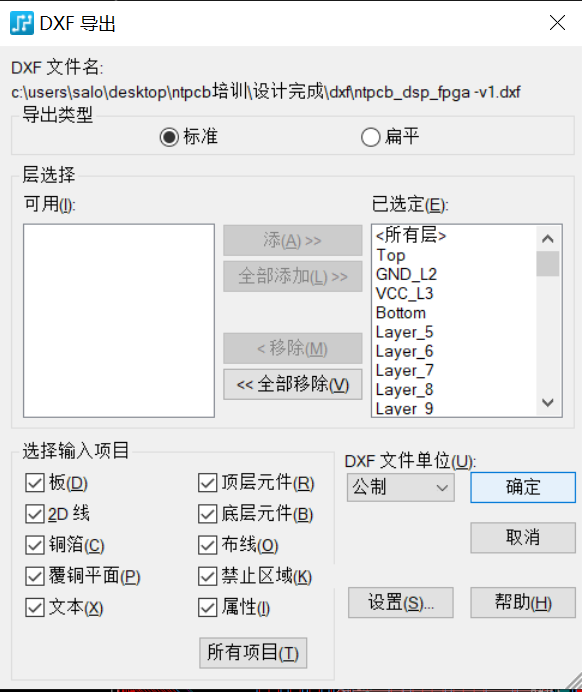

32、DXF文件输出

导出DXF文件给结构工程师做结构。一般默认就可以。

文件 -》导出-。选择DXF

33、钢网

CAM文件里选择钢网文件运行输出就可以了。对于拼版的文件可以向板厂要最终的grebre文件,导出钢网层就可以了。

34、MARK点

mark一般是40mil(1mm)的原点,加上3倍的禁止区域,再在开窗层放一个重叠以禁止区域的铜皮。

mark点离板边4mm,一般放两个在对角,或三个成三角形 。

mark点里不能有任何东西。

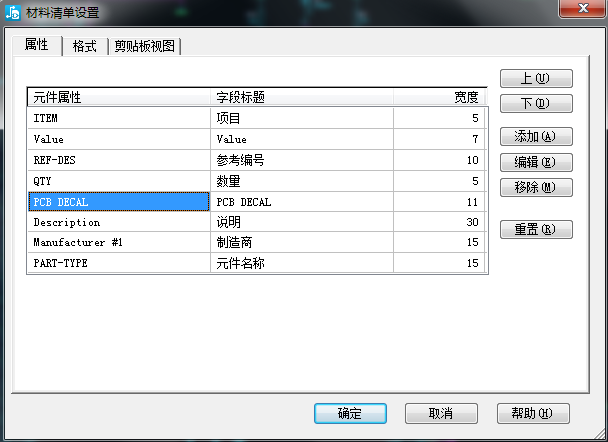

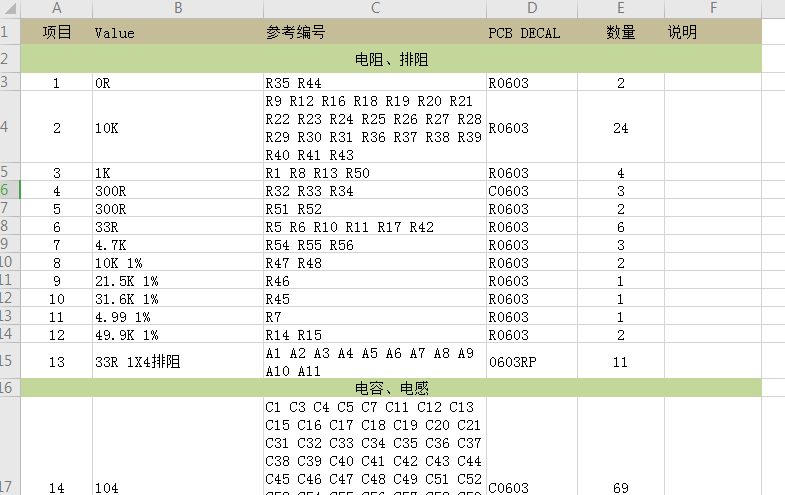

35、bom

bom在logic里出,出完后整理成公司规定的样式。

方法:文件-》报告-》材料清单里设置

新建EXSEL表,粘贴整理

浙公网安备 33010602011771号

浙公网安备 33010602011771号